El empaquetado 3D es cada vez más recurrente para poder mejorar las prestaciones de los actuales chips, ya sean los chips de procesamiento o también los de memoria, apilando varios de ellos para conseguir mayores capacidades. Por eso, en este artículo te vamos a explicar qué es TSMC 3D Fabric, una tecnología usada por ejemplo para la AMD 3D V-Cache, y otros rivales que existen en la actualidad para otras foundries.

Quizás también te puede interesar:

Tipos de empaquetados

Antes de comenzar con las tecnologías de empaquetados 3D, como TSMC 3D Fabric, vamos a conocer qué tipos de empaquetados de chips existen. A continuación, se explica cada uno de ellos:

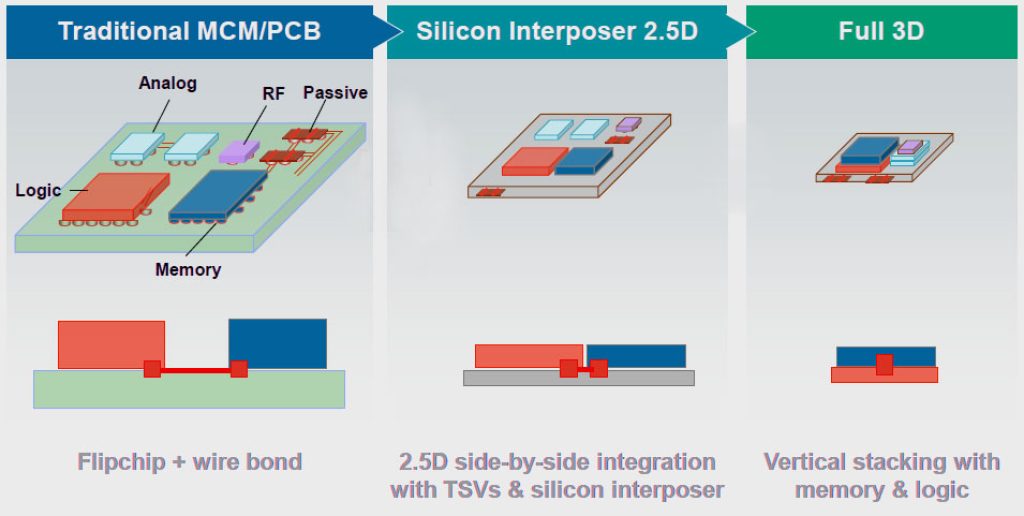

- Empaquetado convencional: es el método convencional utilizado para montar y conectar chips individuales en una placa de circuito impreso (PCB). En este enfoque, los chips sobre un sustrato como el usado en multitud de diseños como las CPUs de hace unos años, donde solo había una PCB en la que se unía el chip o los chips del empaquetado.

- Empaquetado 2.5D: implica la colocación de múltiples chips y otros componentes en un sustrato intermedio llamado interposer. El interposer actúa como un puente entre los chips y la placa de circuito impreso, proporcionando conexiones eléctricas y de comunicación. Esto permite una mayor densidad y mayor ancho de banda en comparación con el empaquetado convencional o 2D del punto anterior.

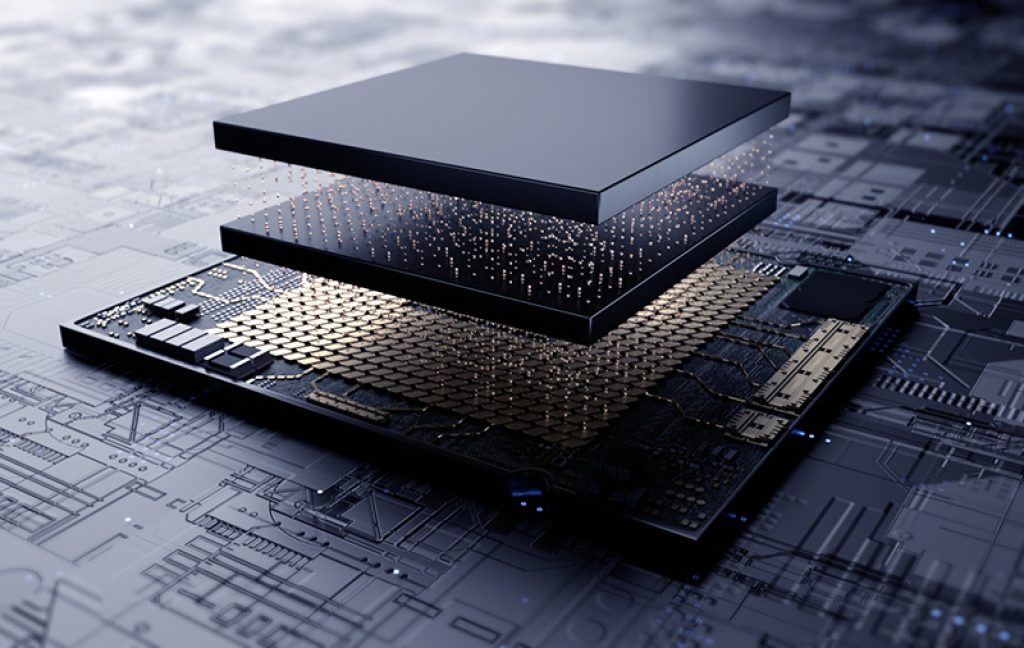

- Empaquetado 3D: también conocido como chip stacking, implica el apilamiento de múltiples capas de chips directamente encima uno del otro para formar una estructura tridimensional. Cada chip se conecta a través de interconexiones verticales llamadas «through-silicon vias» (TSVs), que permiten la comunicación entre los diferentes niveles del apilamiento. El empaquetado 3D proporciona una alta densidad de componentes, mayor capacidad de procesamiento y menor consumo de energía al reducir las distancias entre los chips y mejorar la eficiencia térmica. Esta tecnología se utiliza en aplicaciones como servidores de alta gama, memoria apilada (como HBM), para apilar chips de memoria flash para conseguir capacidades superiores, enfoques de integración de sistemas complejos como la memoria caché apilada sobre los chips Ryzen para la 3D V-Cache de AMD, etc.

Estos conceptos serán necesarios para comprender los siguientes apartados que comentaré en este artículo…

Ventajas y desventajas del empaquetado 3D

A continuación, se presentan algunas de las ventajas y desventajas del chip 3D packaging. Comenzando por las ventajas:

- Mayor densidad de integración: el chip 3D packaging permite apilar múltiples capas de chips, lo que aumenta significativamente la densidad de integración. Esto significa que se pueden colocar más componentes en un espacio reducido, lo que resulta en dispositivos más compactos y eficientes.

- Mejor rendimiento y menor consumo de energía: reduce la longitud de las rutas de interconexión entre los chips, lo que conduce a una mayor velocidad de transferencia de datos y un menor consumo de energía. Además, al apilar diferentes tipos de chips, como unidades de procesamiento y memoria, se puede lograr una mayor eficiencia en el rendimiento del sistema.

- Mayor ancho de banda y menor latencia: ofrece un mayor ancho de banda y una menor latencia en comparación con los enfoques tradicionales. Esto es especialmente beneficioso en aplicaciones de alto rendimiento que requieren una rápida transferencia de datos, como la inteligencia artificial, el cómputo de alto rendimiento y las redes de comunicación.

- Flexibilidad de diseño: mayor flexibilidad de diseño, ya que permite la integración de diferentes tipos de chips fabricados en diferentes tecnologías y nodos. Esto facilita la creación de soluciones personalizadas y optimizadas para aplicaciones específicas.

Por otro lado, las desventajas son:

- Costes de fabricación: al tener que apilar, enlazar, usar interposers, y procesos adicionales de grabado y demás, así como alineación, pruebas adicionales, etc., el precio de fabricación es superior.

- Desafíos de disipación de calor: al apilar múltiples capas de chips, puede generar una mayor concentración de calor. Esto puede plantear desafíos en cuanto a la disipación de calor efectiva y puede requerir soluciones de refrigeración más sofisticadas.

TSMC 3D Fabric

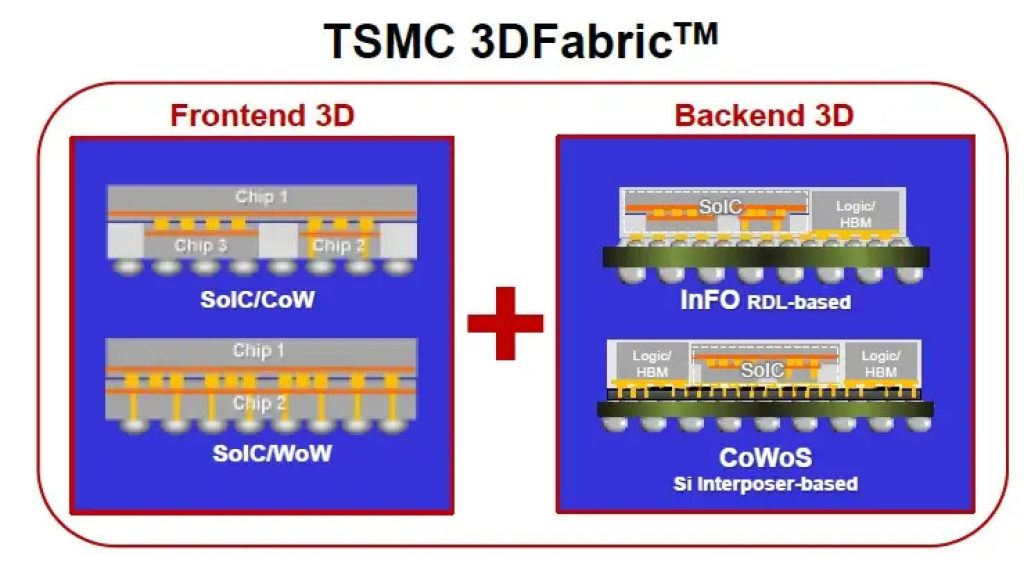

TSMC anunció hace unos años en uno de los eventos de la compañía su innovadora tecnología para permitir empaquetados 3D para sus clientes. Allí se pudo conocer la denominada 3D Fabric, que es un sistema de empaquetado 3D (y también para troqueles 2.5D) avanzado de esta foundry tan importante y que es la fábrica de marcas como NVIDIA, AMD, Apple, Qualcomm, etc.

Como su propio nombre indica, la marca 3D Fabric se refiere a un tejido o malla para poder interconectar los diferentes elementos del empaquetado:

Del anterior diagrama se pueden sacar alguna información interesante. Por ejemplo:

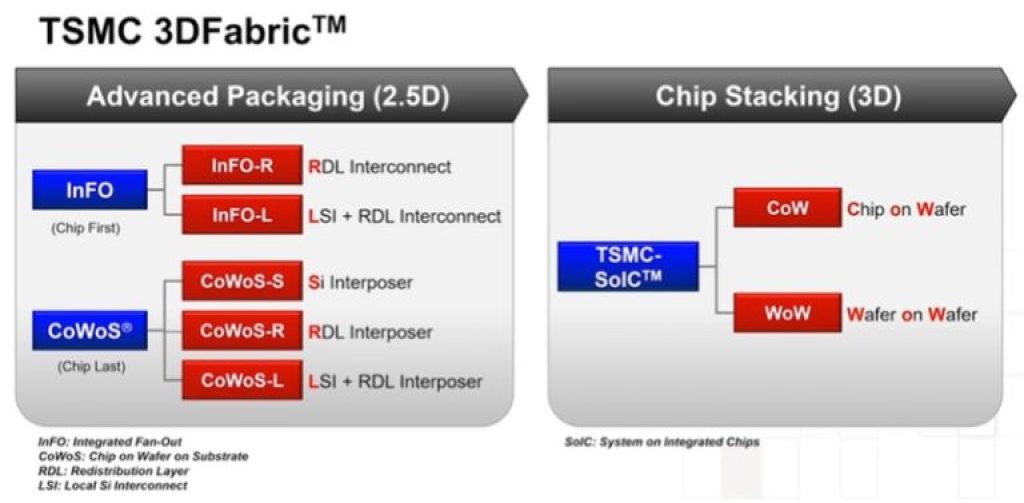

- InFO (Integrated FanOut): este tipo de paquetes 2.5D usan una oblea modificada con troquel incrustado boca abajo y rodeado de compuestos de moldeo. Las capas de interconexiones de redistribución RDL se fabrican mediante una oblea epoxi. En el caso del InFO-L se refiere a un chiplet que actúa como puente de silicio entre las matrices o troqueles incrustados en el empaquetado InFo para mejorar la conectividad sobre el paso de metalización RDL.

- CoWoS (Chip-on-Wafer-on-Substrate): es otra tecnología empleada para empaquetados 2.5D, especialmente para pilas de chips de memoria HBM, entre otras aplicaciones. Para esto se emplean intercaladores con microbumps de enlace y TSV (vías a través del silicio), ofreciendo así una densidad de interconexión mejorada. Además, podemos ver que se ofrece interposer CoWoS-S de silicio, CoWoS-R de tipo RDL, y CoWoS-L con LSI + RDL según los costes y densidades que necesite cada cliente.

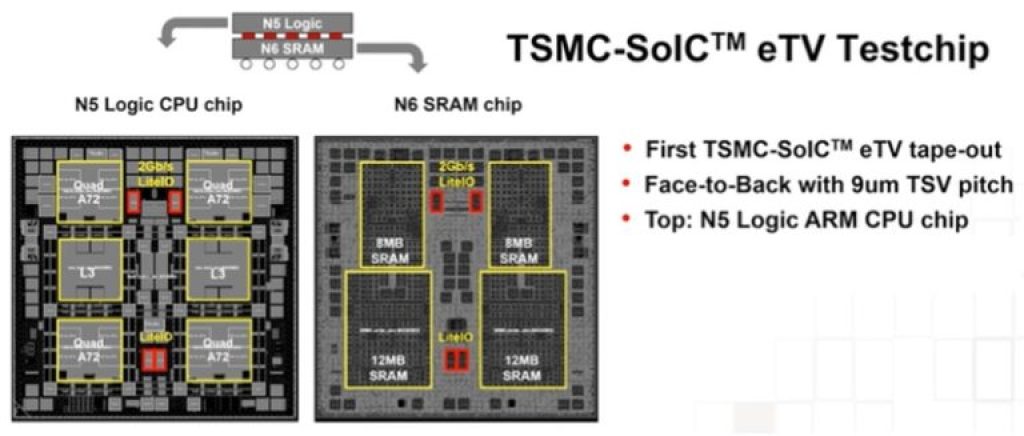

- 3D SoIC (System on Integrated Chips): por otro lado, en el empaquetado 3D tenemos esta otra tecnología perteneciente a la 3D Fabric, pero es algo más avanzada, orientada a configuraciones de troquel cara a cara o cara espalda, con una unión híbrida y conexión en vertical usando TSV.

Para este tema, la que más nos interesa es precisamente SoIC, ya que me centraré en el empaquetado 3D.

Las ventajas de un empaquetado con 3D Fabric y tipo 3D son muchas, permitiendo integrar una cantidad muy superior de chips en un mismo espacio, al hacerlo de forma vertical. Mismo principio que siguen los rascacielos frente a las casas. Sin embargo, no todo son ventajas.

El problema es que debido al alto nivel de integración de chips en vertical, cada uno de estos chips disipa calor, y esto hace que las soluciones 3D tengan exigencias de refrigeración superiores a los empaquetados clásicos, o que incluso se deba bajar el voltaje o consumo para paliar estos problemas.

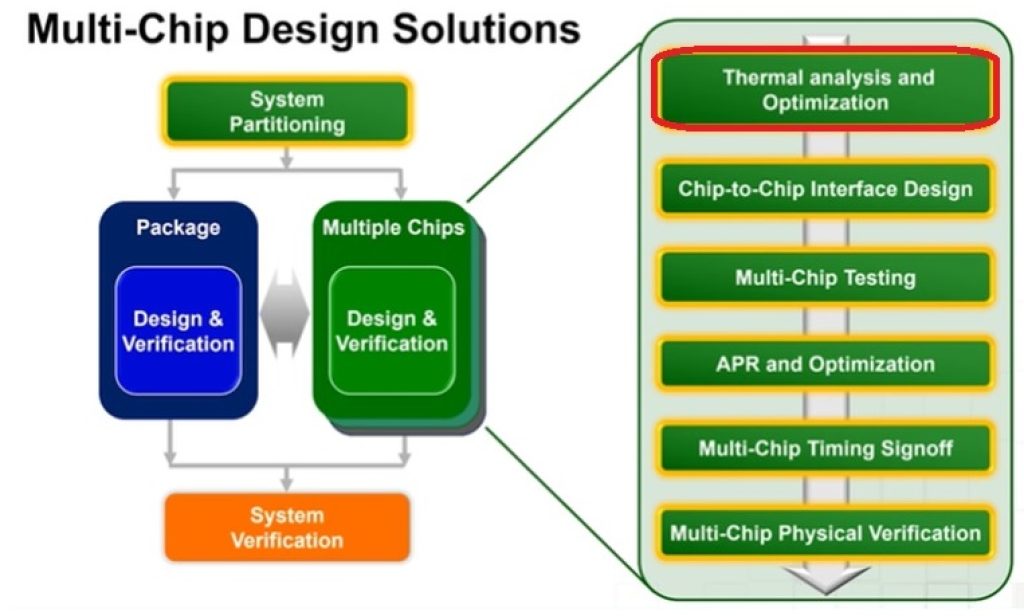

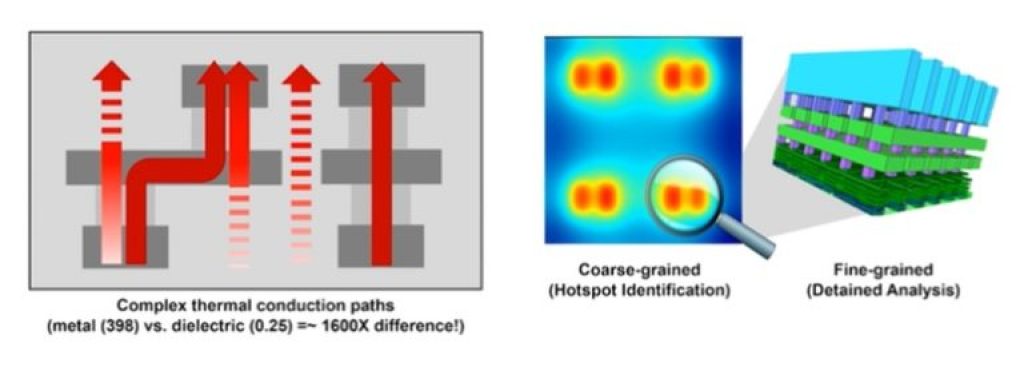

Según las simulaciones de este tipo de empaquetados, el calor disipado viaja a través de las TSV o vías que pasan de un chips a otro para interconectarlos. Por eso, hay que tener unas consideraciones particulares para el diseño de este tipo de chips:

Es decir, estas rutas actúan como si fuesen una especie de «chimenea» y que habrá que tener muy en cuenta también para las herramientas EDA que proveen los desarrolladores de este tipo de software para sus clientes. No obstante, muchas empresas importantes también usan sus propias herramientas EDA personalizadas para sus procesos o adaptadas a sus preferencias y necesidades. Pero sea como sea, son puntos críticos que hay que tener en cuenta durante el diseño antes de entregar el chip a TSMC para su fabricación, y esto también sirve para otras tecnologías que compiten con la de TMSC que veremos más adelante.

Otras tecnologías

Además de la 3D Fabric de TSMC, también hay otras tecnologías interesantes que me gustaría comentar aquí:

Samsung X-Cube

Samsung Electronics, otro de los líderes en tecnología de semiconductores junto con TSMC, ha presentado su innovador desarrollo llamado Samsung ‘X-Cube’, que marca el primer avance de silicio funcional en la industria para la creación de SRAM-logic 3D a 7 nm y más allá. Esta tecnología revolucionaria permite ajustar el ancho de banda y la densidad según los requisitos específicos de diseño en aplicaciones emergentes.

La disponibilidad inmediata de su tecnología de empaquetado tridimensional basada en silicio llegó algo más tarde que la de TSMC. Su nombre proviene de eXtended-Cube, diseñada especialmente para los nodos de proceso más avanzados del mercado. Aprovechando la tecnología de interconexión a través de silicio (TSV) de Samsung, X-Cube ofrece mejoras notables en velocidad y eficiencia energética para satisfacer las exigentes demandas de rendimiento en aplicaciones de próxima generación, como 5G, inteligencia artificial, computación de alto rendimiento, así como aplicaciones móviles y wearable.

Además, esta tecnología combinada con los nodos más avanzados basados en litografía EUV, logrará mejores rendimientos en multitud de aplicaciones, especialmente para apilar celdas de memoria SRAM sobre chips lógicos, entre otros. Recuerda que Samsung, junto con SK Hynix y Micron Technologies es uno de los líderes en el sector de la memoria.

Gracias a la integración tridimensional, el diseño de paquete ultradelgado presenta rutas de señal considerablemente más cortas entre los chips, lo que maximiza la velocidad de transferencia de datos y la eficiencia energética. Además, los clientes de la foundry de Samsung tienen la posibilidad de escalar el ancho de banda y la densidad de la memoria según sus requerimientos específicos. La metodología y el flujo de diseño probados con silicio de Samsung X-Cube ya están disponibles para los nodos avanzados de 7 nm y 5 nm (y más allá conforme vayan apareciendo). Basándose en este diseño inicial, Samsung planea continuar colaborando con clientes globales sin fábrica para facilitar la implementación de soluciones 3D IC en aplicaciones de alto rendimiento de próxima generación.

Intel EMIB 3 + Foveros Direct

Durante la pasada presentación de Intel Accelerated, también se han revelado avances en el empaquetado de chips que Intel utilizará para mejorar la tecnología Foveros que ha venido utilizando hasta ahora. Además, se ha dado a conocer una versión mejorada de EMIB, que estará presente en los próximos procesadores que Intel lanzará al mercado después de Alder Lake, previstos para octubre próximo.

Desde 2017, EMIB ha liderado la tecnología de interconexión para los chips 2,5D. Los actuales procesadores Intel Xeon para centros de datos, con nombre clave Sapphire Rapids, serán los primeros en utilizar esta tecnología EMIB, que utiliza conexiones de 55 micras. Además, se emplea un diseño de doble retícula que ofrece un rendimiento equivalente a los diseños de una sola retícula. En las generaciones futuras, se espera reducir el tamaño de estas conexiones de 55 micras a 45 micras.

La segunda generación de Foveros, que se implementa en los Intel Meteor Lake, contará con conexiones de 36 micras. Esto se logra aprovechando las capacidades de empaquetado de chips a nivel de oblea. Además de esta mejora en el tamaño de las conexiones, la versión mejorada de Foveros permitirá utilizar múltiples nodos de tecnología, lo que dará lugar a un amplio rango de TDP, desde 5 hasta 125 vatios.

La GPU Ponte Vecchio para HPC será la primera en utilizar esta nueva generación de Intel Foveros y el EMIB mejorado que se empleó para producción en masa. La siguiente generación de Foveros, presente en los sucesores de Intel Raptor Lake (los Meteor Lake), utiliza un nuevo sistema de apilado que brinda máxima flexibilidad para el apilamiento en 3D y permite la interconexión en diseños modulares. Con Foveros Omni, será posible desagregar matrices y combinar las superiores con las inferiores en los procesadores, incluso cuando se utilicen nodos de fabricación diferentes. Esta tecnología estará lista para su implementación en los procesadores Intel Meteor Lake en 2023.

Además de Foveros Omni, Intel empleará Foveros Direct, que permitirá una conexión directa de cobre a cobre, lo que reducirá la resistencia y eliminará las limitaciones entre el final de la oblea y el comienzo del paquete. Estas conexiones podrán tener un tamaño inferior a 10 micras, lo que permitirá alcanzar configuraciones de matrices que antes eran imposibles.

Tanto Foveros Direct como Foveros Omni se utilizarán conjuntamente para lograr una mayor eficiencia y mejor rendimiento en los nuevos procesadores Intel que estarán disponibles en 2023. Estas tecnologías han sido desarrolladas en las instalaciones de Intel en Oregón y Arizona, convirtiendo a Intel en la primera y única empresa que realiza estas investigaciones, desarrollo y construcción en suelo estadounidense. También es probable que pueda usar esta tecnología en las foundries a través del servicio IFS (Intel Foundry Service) para los clientes que quieran fabricar en las fabs de Intel sus próximos chips que necesiten empaquetados 3D.

Conclusión

El chip 3D packaging, o empaquetado tridimensional de chips, se considera el futuro de la industria de los semiconductores debido a sus numerosas ventajas y beneficios en comparación con los enfoques de empaquetado tradicionales.