La tecnología de los semiconductores no descansa, el progreso es constante y a niveles muy elevados. Cada vez se necesitan dispositivos con mayor rendimiento y una mejor eficiencia, y eso solo pasa por mejorar los materiales, las estructuras, y los propios dispositivos integrados, como el paso de los CMOS MOSFET hasta los FinFET actuales, hasta la llegada de nuevos transistores como los cFET o los VTFET, con los que IBM y Samsung pretenden revolucionar la industria…

Un poco de historia

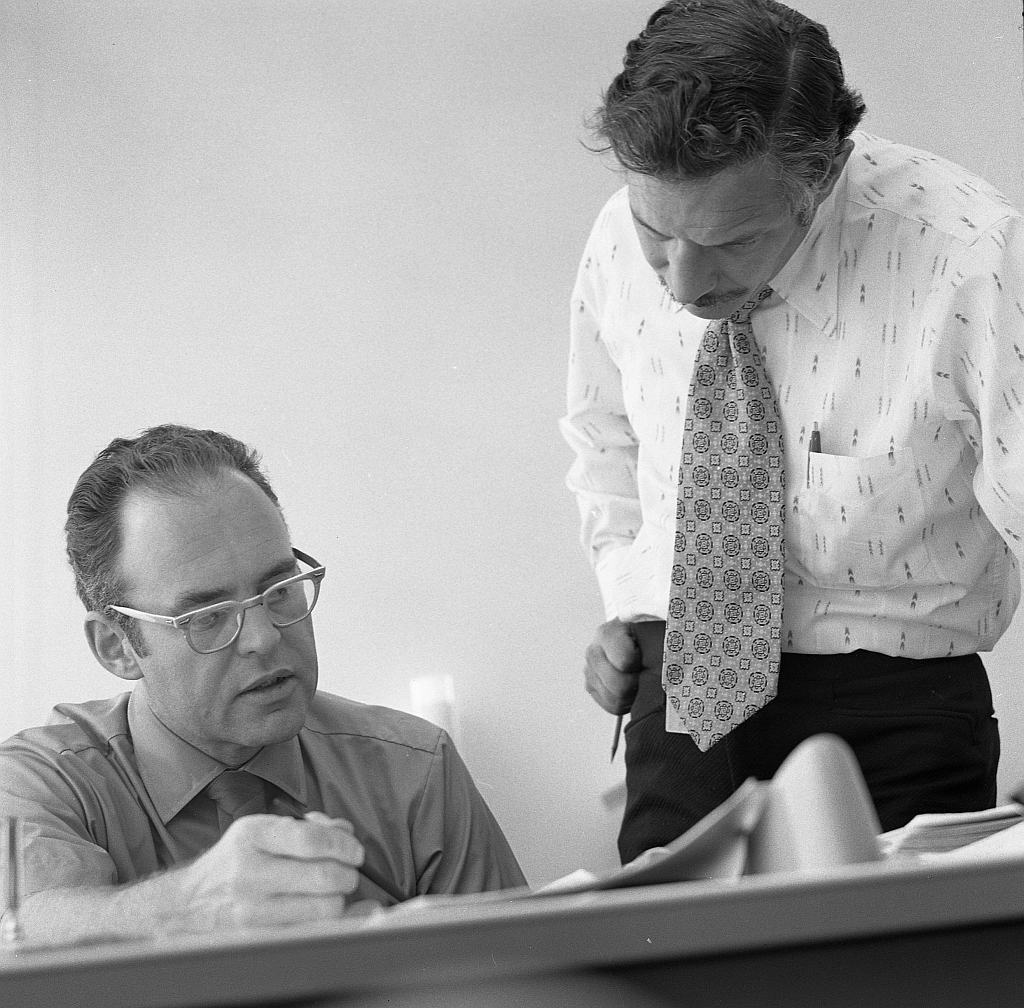

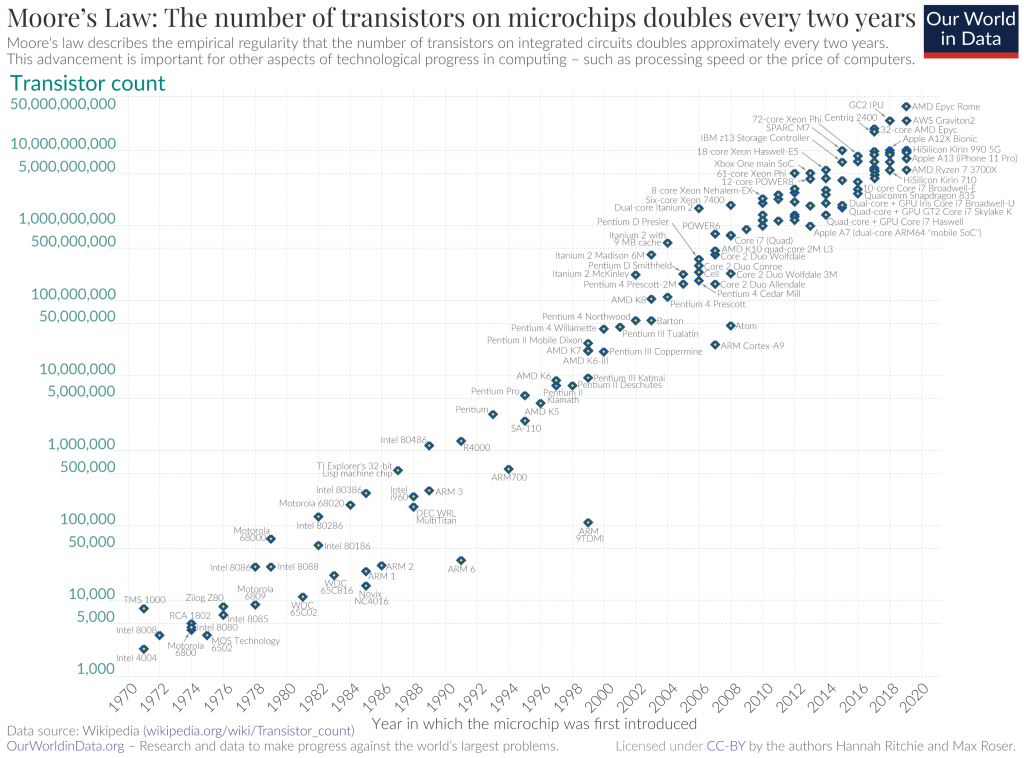

En 1965, Gordon Moore planteó por primera vez una hipótesis que ha moldeado la evolución de la tecnología: la ley de Moore. Esta afirmaba que la cantidad de componentes, como los transistores, en un circuito integrado denso se duplicaría cada dos años, impulsando así la velocidad y capacidad de los ordenadores. Sin embargo, después de más de 55 años, nos encontramos cerca del límite de lo que se puede lograr al aumentar la cantidad de transistores en un solo chip.

A pesar de ello, el camino hacia el futuro de los sistemas informáticos no se detiene. Los sistemas dinámicos de inteligencia artificial están listos para impulsar diversos aspectos de nuestras vidas, desde la seguridad vial hasta el descubrimiento de fármacos y la fabricación avanzada. Estas aplicaciones requerirán chips considerablemente más potentes que los actuales. Para seguir avanzando en velocidad y capacidad de procesamiento, tal como lo postuló Moore, se necesitaría construir chips con hasta 100 mil millones de transistores.

En este contexto, IBM Research, en colaboración con Samsung y nuestro socio Albany Research Alliance, ha logrado un gran avance en el diseño de semiconductores. Nuestro enfoque innovador, denominado Transistor de Efecto de Campo de Lámina Nanométrica de Transporte Vertical (VTFET), podría ser la clave para mantener viva la ley de Moore en los años venideros.

VTFET: Vertical-Transport Nanosheet para mantener viva la Ley de Moore

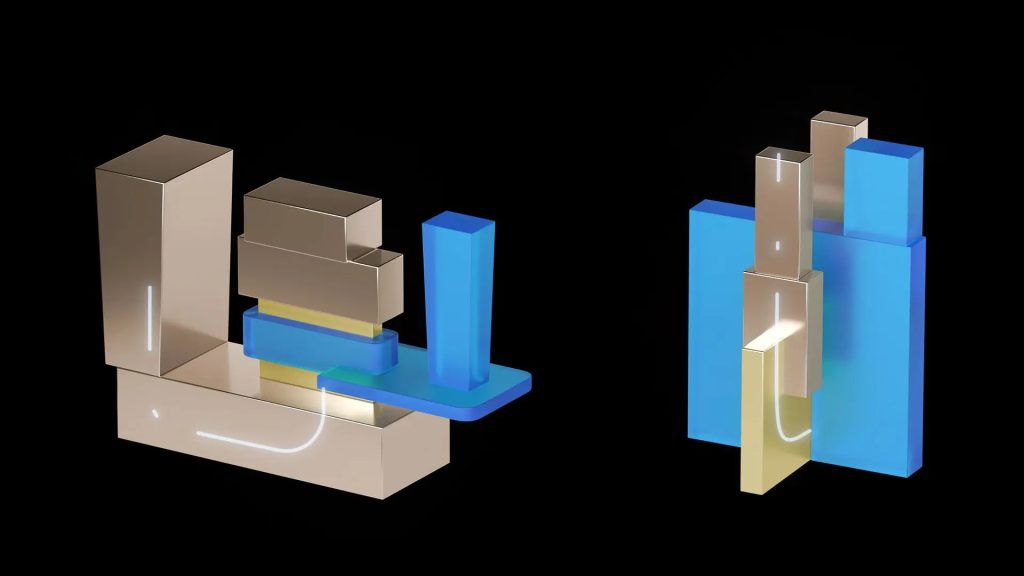

El VTFET es un enfoque disruptivo en la arquitectura de los transistores. A diferencia de los diseños convencionales, este nuevo transistor utiliza láminas nanométricas que permiten un transporte vertical de corriente eléctrica, en lugar de depender únicamente del transporte lateral. Esto resulta en un mejor rendimiento y una mayor eficiencia energética.

Una de las ventajas clave del VTFET es su capacidad para integrar un mayor número de transistores en un chip sin aumentar significativamente su tamaño. Al permitir el transporte vertical de corriente, se puede reducir la distancia que la señal eléctrica debe recorrer, lo que conduce a una mejora en la velocidad y eficiencia del procesamiento.

Además, el VTFET ofrece una mayor tolerancia al calor y a las pérdidas eléctricas, lo que lo convierte en una opción prometedora para aplicaciones de alta potencia y alto rendimiento. Esto podría ser especialmente relevante en campos como la inteligencia artificial y el cómputo cuántico, donde se requiere un procesamiento intensivo y rápido de grandes volúmenes de datos.

El enfoque VTFET de IBM Research y Samsung demuestra que la innovación continua y la exploración de nuevos enfoques pueden ayudar a superar los límites tecnológicos actuales. Aunque la ley de Moore puede estar llegando a su límite en términos de aumento de la cantidad de transistores en un chip, esta nueva tecnología ofrece una ruta prometedora para seguir impulsando el progreso de la computación en el futuro.

Encontrando más espacio

En la actualidad, las arquitecturas dominantes de los chips son los transistores de efecto de campo de transporte lateral (FET), como el transistor de efecto de campo de aleta, o FinFET (que recibe su nombre porque el cuerpo de silicio se asemeja a la aleta trasera de un pez), que apila transistores a lo largo de la superficie de una oblea. En cambio, el VTFET apila los transistores de forma perpendicular a la oblea de silicio y dirige el flujo de corriente de forma vertical a la superficie de la oblea. Este nuevo enfoque aborda las barreras de escalamiento al relajar las limitaciones físicas en la longitud de la puerta del transistor, el grosor del espaciador y el tamaño del contacto, de modo que cada una de estas características pueda optimizarse ya sea para el rendimiento o para el consumo de energía.

Con el VTFET, se ha logrado demostrar con éxito que es posible explorar la escala más allá de la tecnología de lámina nanométrica en el diseño de semiconductores CMOS. En estos nodos avanzados, el VTFET podría utilizarse para ofrecer hasta el doble de rendimiento o una reducción de hasta el 85 por ciento en el consumo de energía en comparación con la alternativa de finFET escalado.

La nueva arquitectura VTFET muestra un camino para continuar la escala más allá de la lámina nanométrica. En mayo, IBM anunció diseños de chips de nodo de 2 nanómetros que permitirán que un chip albergue hasta 50 mil millones de transistores en un espacio del tamaño de una uña. El VTFET continúa el viaje de innovación y abre la puerta a nuevas posibilidades.

En el pasado, los diseñadores empacaban más transistores en un chip reduciendo el paso de la puerta y el paso de la conexión de cables. El espacio físico donde todos los componentes encajan se denomina Contacted Gate Pitch (CGP). La capacidad de reducir los pasos de la puerta y de conexión ha permitido a los diseñadores de circuitos integrados pasar de miles a millones de transistores en nuestros dispositivos. Pero con las tecnologías finFET más avanzadas, solo hay tanto espacio para espaciadores, puertas y contactos. Una vez que se alcanza el límite de CGP, no hay más espacio disponible.

CGP se refiere a la distancia mínima desde la puerta de un transistor hasta otra y es funcionalmente un indicador del espacio físico donde encajan todos los componentes.

Al orientar el flujo de corriente eléctrica de forma vertical, las puertas, espaciadores y contactos ya no están limitados de las formas tradicionales: tenemos espacio para escalar CGP al tiempo que mantenemos un tamaño saludable de transistor, contacto y aislamiento (Shallow Trench Isolation o STI). Liberados de las limitaciones de la disposición lateral y el flujo de corriente, además, los investigadores pudieron usar contactos de fuente/drenaje más grandes para aumentar la corriente en el dispositivo. La longitud de la puerta se puede seleccionar para optimizar la corriente de conducción y la fuga del dispositivo, mientras que el grosor del espaciador se puede optimizar de forma independiente para una menor capacitancia. Ya no están obligados a comprometer el tamaño de la puerta, el espaciador y el contacto, lo que puede resultar en una mayor velocidad de conmutación y una reducción del consumo de energía.

Otra característica clave del VTFET es la capacidad de utilizar STI para el aislamiento de circuitos adyacentes y lograr un Aislamiento de Rotura de Difusión Cero (ZDB, por sus siglas en inglés), sin pérdida de pasos de puerta activos. En comparación, la densidad de la circuitería FET de transporte lateral se ve afectada por roturas de difusión doble o simple requeridas para el aislamiento de circuitos, lo que afecta la capacidad de reducir aún más la tecnología.

Esperanza de futuro

Incluso hace una década, se podía ver que las arquitecturas laterales alcanzarían límites de escalamiento con pasos de puerta agresivos: prácticamente, cada uno de los componentes del dispositivo se acercaba a los límites de escalamiento. Se pretendía encontrar otros caminos que pudieran romper esas barreras, y nuestra motivación nunca ha cambiado. Nuestro objetivo siempre ha sido producir un dispositivo competitivo para las tecnologías del futuro.

Con un paso de puerta más agresivo que cualquier cosa conocida en producción y transistores lógicos CMOS con un paso de puerta inferior a los 45 nm en obleas de silicio a granel, y los expertos creen que el diseño VTFET representa un gran avance hacia la construcción de transistores de próxima generación que permitirán una tendencia de dispositivos más pequeños, más potentes y eficientes en energía en los próximos años.