Seguramente estés interesado en saber qué es RTL (Register-Transfer Level). Y es que si te gusta la electrónica o quieres aprender cómo se diseña un circuito integrado o chip, este es un concepto vital durante el proceso. Por eso vamos a ver qué significa y todo lo que deberías saber.

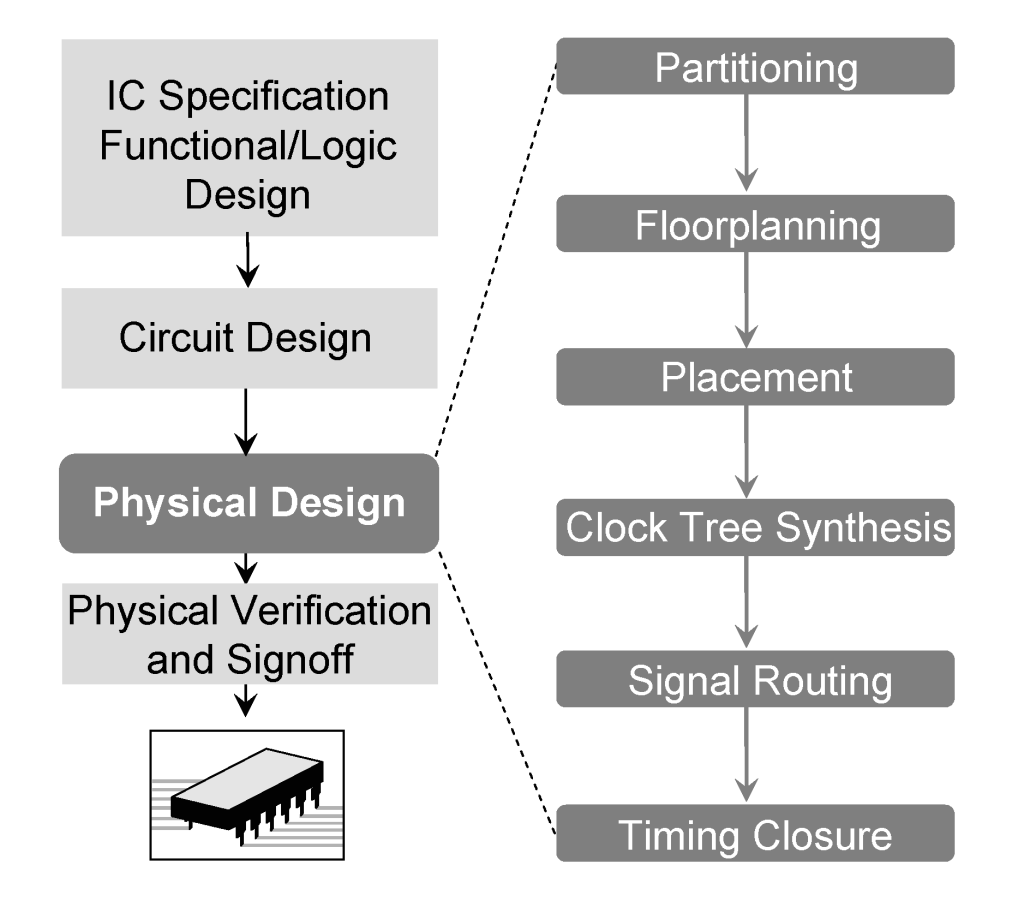

Flujo de diseño de chips

Lo primero que deberías conocer es el flujo de diseño de un chip o circuito integrado (CI). Un proceso bastante complejo para luego fabricarse en una foundry. De este modo, podrás comprender cómo encaja la pieza del RTL en todo esto, ya que si no estarás un poco perdido.

Especificaciones del Sistema

Lo primero que se hace durante el proceso de diseño de un chip es definir las especificaciones que tendrá. En el caso de una CPU o una GPU, lo primero sería diseñar la ISA que se empleará, es decir, la arquitectura principal que definirá todo lo demás. También se especificarán detalles como el tamaño de palabra que manejará, etc.

Diseño arquitectónico

Una vez completado el primer paso, se comenzará a diseñar a nivel arquitectónico el sistema en forma de diagrama de bloques. Una especie de nivel de jerarquía va a operar el sistema que se está diseñando.

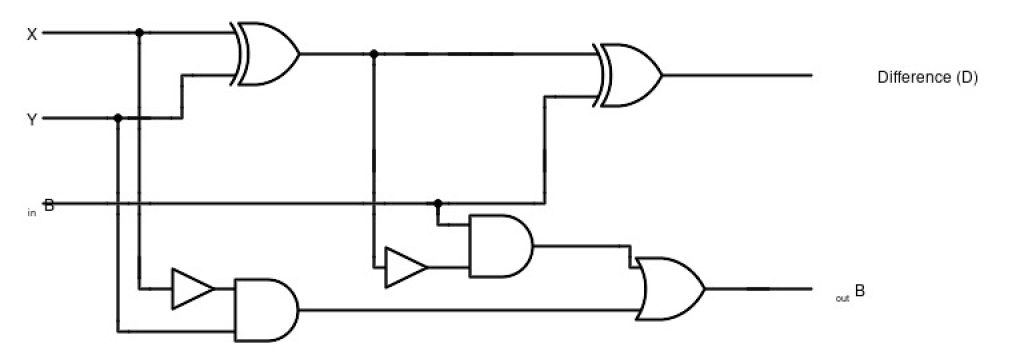

Diseño Lógico Básico

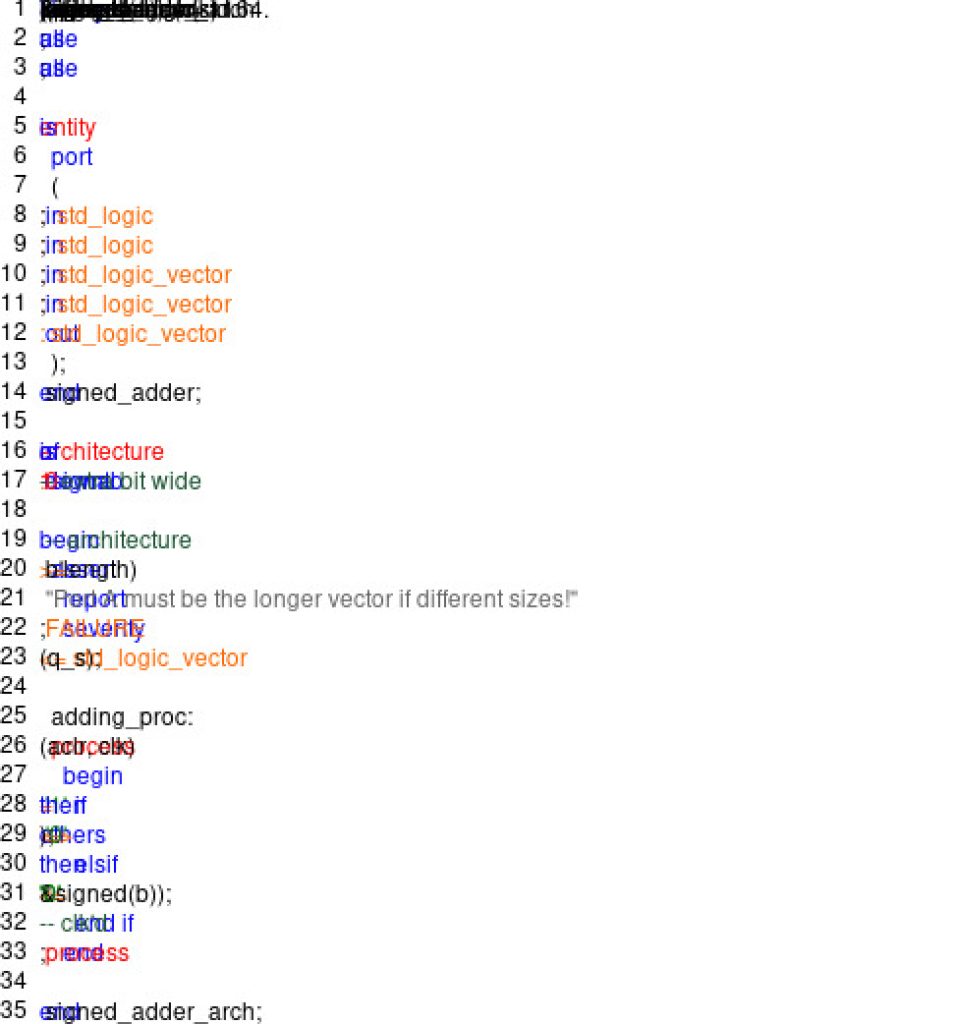

La siguiente etapa es diseñar el sistema lógico a nivel básico. Para ello se utiliza un software EDA y lenguajes de descripción de hardware, es decir, unos lenguajes de programación similares a los de software, pero que definen hardware. Gracias a ellos se pueden crear las unidades lógicas elementales y describir el comportamiento que tendrá.

Algunos ejemplos de estos lenguajes pueden ser VHDL, Verilog, Chisel, etc. Con ellos los desarrolladores pueden trabajar de una forma más abstracta para diseñar chips complejos. Además, el modelo obtenido puede emplearse para etapas posteriores del proceso de una forma sencilla.

Verificación lógica

Cuando se completa el diseño esquemático del sistema, el siguiente paso es verificar su funcionamiento. Crear un chip con un defecto puede ser desastroso, por eso un 80% del proceso se destina a comprobar que todo funciona correctamente a varios niveles.

Para ello, se pueden usar los modelos creados en los lenguajes HDL para luego usar software de simulación que suelen integrarse en los entornos EDA. De este modo, se podrá simular el funcionamiento como sucedería en la realidad y realizar pruebas para determinar si existe algún problema.

En caso de detectar algún problema, se volverá al nivel de diseño esquemático para depurar los problemas. Se generará un esquema actualizado y se seguirá con los siguientes paso hasta llegar nuevamente aquí para volver a verificar que la corrección ha tenido efecto o si existiera algún otro problema. Este bucle se repetirá tantas veces como sea necesario hasta obtener un sistema 100% funcional y sin problemas.

Una de las cosas que se emplean para la verificación es un RTL, es decir, un modelo apto para la simulación que se puede obtener a partir del lenguaje HDL que nombramos anteriormente.

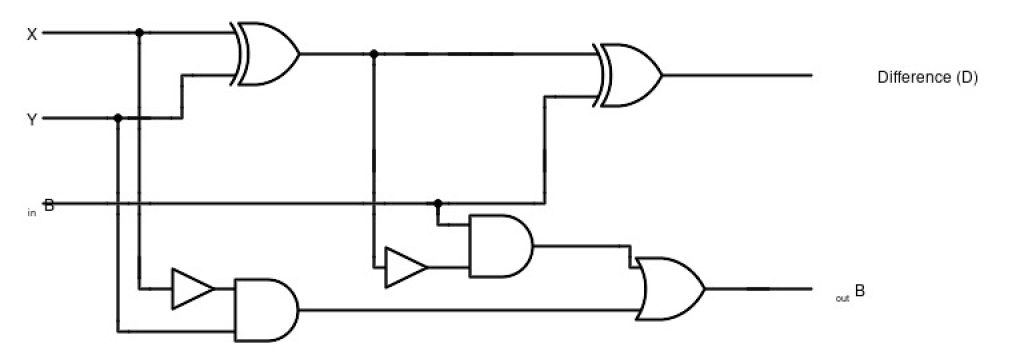

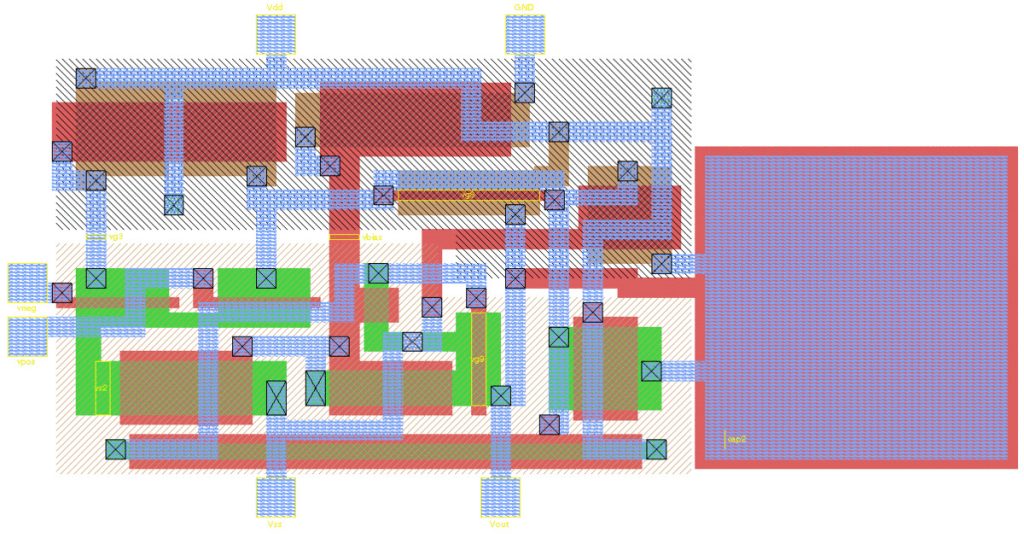

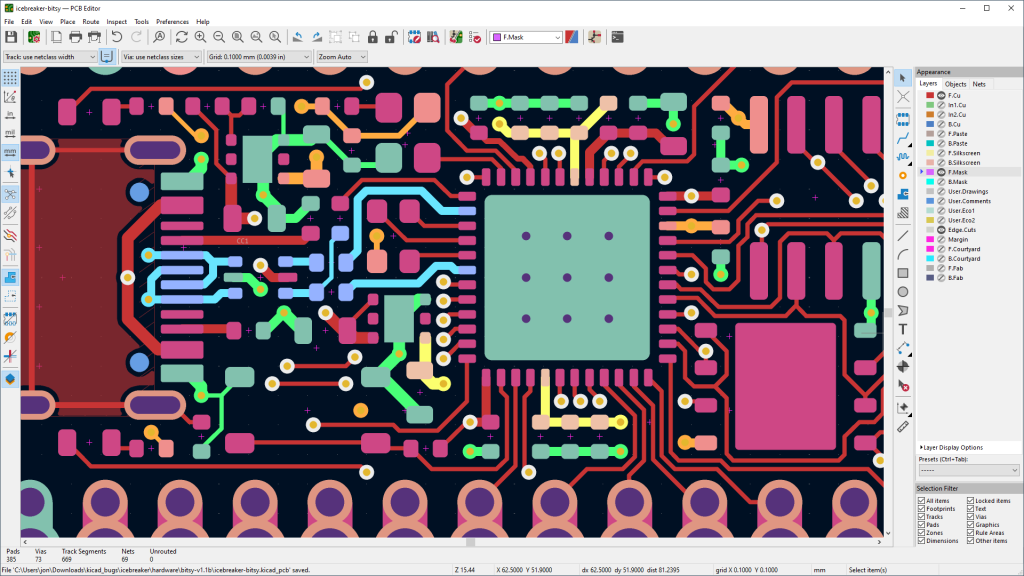

Disposición de diseño físico

El siguiente, y más importante paso, es traducir el sistema al nivel físico. En este nivel, el esquema se convierte en un diseño físico utilizando bloques de construcción básicos. Por ejemplo, se pueden usar puertas NAND compuestas a su vez de transistores u otros elementos electrónicos esenciales, además de crear también todo el entramado de interconexiones que irán en las distintas capas de metal del chip. Estos diseños suelen ser muy complejos, y los resultados se pueden apreciar en lo que se denomina layout.

Debido a que debemos asegurarnos de que todos los transistores estén colocados correctamente, los transistores no deben ocupar un espacio innecesario, todas las interconexiones se agregan según el diseño esquemático, se utilizan múltiples capas de interconexiones para evitar la complejidad y se agregan todos los contactos necesarios para hacer una unión de dos capas diferentes. Existe un proceso denominado placement & routing en el que se ordenará y colocará todo de forma correcta. Ten en cuenta que esto es muy importante para el buen funcionamiento del chip, y no solo para evitar espacios desocupados, por ejemplo para prevenir retrasos de la señal que puedan causar problemas de funcionamiento a nivel físico.

Al final quedará un layout o diseño con todo colocado en su lugar como será fabricado cuando sea enviado el archivo con el diseño a la fábrica donde se crean las máscaras del proceso de fabricación y con ellas se realiza la fabricación en la foundry.

Verificación del diseño físico

Antes de ir a las instalaciones de fabricación, se requiere la verificación del diseño físico. Hasta ahora se ha comprobado el funcionamiento del circuito a nivel de comportamiento y lógico. Pero también es importante comprobarlo a nivel físico y eléctrico, ya que podría haber fallos no detectados en pasos anteriores que deben ser corregidos antes de la producción en masa del chip.

Para eso, se utilizan múltiples técnicas de verificación que incluyen:

- Verificación de reglas de diseño (DRC) donde la herramienta de diseño verifica cualquier violación en las reglas de diseño, como espaciado de metal, tamaños de contacto, etc. para verificar si el diseño diseñado es similar al diseño esquemático, y verifica todas las conexiones y las verifica, etc.

- Análisis de tiempo y potencia para verificar si el diseño realizado viola algún problema de tiempo y agrega retrasos innecesarios, si hay cualquier violación, esto se puede eliminar agregando inversores y búferes, donde sea necesario. La mala planificación de los retrasos de tiempo da como resultado una menor frecuencia de operación, por lo que esta validación y corrección de los retrasos de tiempo es importante para cualquier diseñador.

Dependiendo del tipo de chip, en algunos casos complejos, esto no termina ahí. Por ejemplo, podría haber pasos adicionales como la fabricación de un engineering sample, es decir, un chip de prueba que se empleará para volver a comprobar que todo funciona correctamente. Por ejemplo, sometiéndolo a bechmarks, ejecutando software de todo tipo, etc.

Fabricación y Pruebas Finales

El paso final es la fabricación del diseño físico. Es decir, usar el layout para fabricar el CI en masa. Mientras se diseña el sistema en las herramientas, la foundry que va a fabricar el chip proporciona todas las bibliotecas y la información de las capas para el proceso o nodo específico en el que se fabricará. Por ejemplo, no es lo mismo fabricar un chip de 10 nm con FinFET que hacerlo con 3nm GAA o con 60nm MOSFET…

Una vez que el sistema está diseñado y verificado, se envía un archivo .GDS a la fundición para su fabricación. En algunos casos se requerirá de un tercero para fabricar las máscaras a partir de dicho archivo. Estas máscaras se usarán como patrones en el proceso de fotolitografía para fabricar las diferentes capas del chip y obtener el diseño requerido.

La prueba final se realiza en el propio wafer u oblea donde se fabrican los chips, y se seguirán realizando pruebas una vez se separan los chip y se empaquetan (la mayoría de las veces, el empaquetado se realiza en otra fabrica donde se ensambla el chip con el PCB, etc.). Todo tiene que funcionar a la perfección. Además, aquí también entraría en juego el proceso del binning, aunque esto es otra historia…

Herramientas de diseño de chips

Hay diferentes empresas que ofrecen herramientas para el diseño de chips. Para cada etapa del proceso de diseño, las herramientas son diferentes. Los entornos EDA suelen tener todo o casi todo lo necesario para todas las etapas del proceso. Algunos de estos software conocidos son:

- Siemens proporciona varias herramientas de diseño y verificación para el diseño de circuitos integrados que incluyen:

- Análisis de integridad de la señal para garantizar que se reduzca el tiempo de diseño y hacer que el diseño sea perfecto en el primer intento.

- Calibre Design Solutions que se utiliza para superar los problemas de capacitancia en el circuito.

- IC Custom para completar.

- Cadence es uno de los gigantes en la industria del diseño de circuitos integrados. Proporcionan herramientas que se pueden utilizar para crear circuitos integrados tanto analógicos como digitales. Cadence también ofrece herramientas muy efectivas para reducir la carga de diseño del diseñador al proporcionar herramientas de generación automática de diseños. De esta forma, un diseñador crea un módulo de nivel superior en un lenguaje RTL y la herramienta lo traduce al nivel físico.

¿Qué es RTL?

El Register-Transfer Level (RTL) es una metodología de diseño digital utilizada para crear circuitos integrados y otros sistemas digitales. El RTL es un nivel superior de abstracción utilizado por los ingenieros para crear diseños lógicos digitales más fáciles de leer, comprender y modificar.

El RTL simplifica el proceso de diseño y facilita la comprensión de diseños digitales complejos. Este método se utiliza para describir el comportamiento de un circuito digital mediante registros, elementos de memoria y puertas lógicas combinacionales. El RTL sirve de puente entre los diseños abstractos y las implementaciones reales de los circuitos. Proporciona un mayor nivel de abstracción que facilita la depuración y modificación del diseño.

El RTL es cada vez más popular entre los diseñadores digitales porque permite realizar diseños más eficientes y precisos. Se utiliza en un número cada vez mayor de aplicaciones, desde chips informáticos a sistemas embebidos. El RTL puede ayudar a mejorar la velocidad, precisión y fiabilidad de los proyectos de diseño digital, lo que lo convierte en una herramienta inestimable en el ámbito del diseño digital.

Ten en cuenta que los circuitos digitales se construyen desde cero utilizando dos bloques de construcción principales: puertas lógicas y registros. Las puertas lógicas son los componentes básicos de los diseños digitales y son los elementos de conmutación reales que dirigen el diseño. Los registros son elementos de almacenamiento que contienen datos y sirven de interfaz entre la lógica y el mundo exterior.

Un diseño RTL es una representación de alto nivel de un circuito digital. Se construye combinando registros, memorias y lógica combinacional. La representación a nivel de registro-transferencia de un diseño suele ser mucho más fácil de entender que un diagrama de circuito. Este método se utiliza para describir el comportamiento de un circuito digital mediante registros, elementos de memoria y puertas lógicas combinacionales. El RTL sirve de puente entre los diseños abstractos y las implementaciones reales de los circuitos. Proporciona un mayor nivel de abstracción que facilita la depuración y modificación del diseño.

Ventajas del RTL

Entre las ventajas que tiene el RTL destacan:

- Aumento de la precisión del diseño: la primera y más importante ventaja del RTL es que puede mejorar la precisión de un diseño digital. El uso de una metodología de diseño de alto nivel permite a los ingenieros encontrar y corregir errores en el diseño desde el principio, antes de que tengan la oportunidad de aparecer en el circuito final. Esto puede ahorrar tiempo y dinero en comparación con la depuración de un diseño incorrecto que ya se ha implementado.

- Mayor eficiencia del diseño: otra ventaja de utilizar RTL es que puede mejorar la eficiencia del diseño. El proceso de diseño se agiliza cuando los ingenieros utilizan un lenguaje de alto nivel, lo que facilita la creación de diseños precisos en menos tiempo.

- Diseños complejos más fáciles de entender: los diseños RTL son más fáciles de entender tanto para los diseñadores como para los ingenieros que no estén familiarizados con el diseño digital.

- Mayor depuración: el diseño RTL es útil para la depuración porque es mucho más fácil visualizar el diseño. Como el diseño se divide en partes más pequeñas, es más fácil entenderlo y depurarlo.

- Mayor modularidad del diseño: crear un diseño que se divide en partes más simples también puede ayudar a la modularidad del diseño. Los diseñadores pueden reutilizar partes del diseño, lo que aumenta su reutilización.

- Mayor modificación del diseño: otra ventaja de utilizar RTL es que puede facilitar la modificación del diseño. Dado que el diseño se divide en partes más pequeñas, es más fácil modificar el diseño sin cambiar accidentalmente algo más.

Metodología de diseño RTL

El primer paso en el diseño RTL es dividir el diseño en partes. Los diseñadores suelen crear un diagrama a nivel de registro para describir la estructura general del diseño. El diagrama muestra las entradas y salidas del diseño, así como el flujo de datos a través del diseño. El diseñador debe decidir qué tipo de lógica se utilizará para cada parte del diseño.

El tipo de lógica (TTL, ECL, CMOS,…) determina la funcionalidad de cada parte del diseño. Una vez que el diseñador ha decidido el tipo de registro y la funcionalidad, el siguiente paso es crear la interfaz entre cada parte del diseño. Hay varias maneras de hacerlo, pero el método más común es crear un diccionario de datos. El diccionario de datos desglosa cada parte del diseño, mostrando cómo se conecta cada parte con las demás. El diccionario de datos es especialmente útil para encontrar errores en el diseño.

RTL en el diseño digital

El diseño digital es el proceso de transformar una función lógica en una implementación física. La función lógica describe la función del circuito físico, que puede ser cualquier circuito físico, incluidos ordenadores, sensores y otros dispositivos con circuitos eléctricos. El diseño digital puede describir el circuito mediante álgebra booleana o utilizando un lenguaje de nivel superior de transferencia de registros.

El diseño digital suele implementarse en silicio mediante un circuito integrado, o chip. El proceso de diseño incluye el diseño de la lógica, o el algoritmo que implementa el circuito, y el diseño del circuito físico, o la disposición de los componentes electrónicos en la placa del circuito que implementará el algoritmo. El proceso de diseño comienza con un algoritmo de alto nivel que se implementa en software, como un programa informático. El algoritmo estará representado por una serie de instrucciones y datos. A continuación, el proceso de diseño continúa con la implementación del algoritmo en forma de circuito, ya sea en software (soft-core) o en silicio (implementación física).

Flujo de diseño RTL

El diseño a nivel de transferencia de registro es una metodología de diseño descendente. Esto significa que el diseño comienza en un nivel alto y avanza hacia un nivel más detallado según sea necesario. Los diseñadores comienzan desglosando el diseño global en sus partes más simples y, a continuación, combinan esas partes y añaden detalles adicionales hasta que tienen una descripción completa y precisa del diseño.

Esta metodología de diseño es una forma eficaz de crear diseños digitales, ya que permite a los diseñadores descomponer un diseño complejo en partes más pequeñas y sencillas sin perder de vista el panorama general. Los diseñadores pueden encontrar y corregir errores en el diseño desde el principio, cuando son más fáciles de corregir.

Verificación RTL

Anteriormente hablé de la verificación, pero ahora toca profundizar un poco más en la verificación RTL. La verificación es el proceso de comprobar que el diseño cumple los requisitos especificados por el ingeniero. Los ingenieros utilizan diversos métodos para verificar sus diseños, como la simulación, la verificación formal, la emulación y el análisis formal:

- Simulación: es uno de los métodos más comunes para verificar un diseño digital. Resulta útil para comprobar la funcionalidad de un diseño, pero no tanto para detectar errores. Los ingenieros pueden utilizar la simulación para comprobar las entradas y salidas del diseño y asegurarse de que son correctas.

- Verificación formal: es otra forma de verificar un diseño o su comportamiento. Es una técnica que utiliza ecuaciones matemáticas para verificar que el diseño cumple las especificaciones requeridas. Los ingenieros crean un modelo abstracto del diseño en un programa informático y aplican reglas de verificación al modelo para determinar si el diseño es correcto.

- Emulación: es otro método para verificar un diseño. Los ingenieros crean un modelo de silicio del diseño para facilitar la detección de errores en el mismo.

Síntesis RTL

Una vez verificado el diseño, el siguiente paso es crear una implementación del diseño en silicio. El proceso de creación de una implementación a partir de un diseño se denomina síntesis. El ingeniero utilizará una herramienta de implementación para crear una lista de redes del diseño que incluya las características eléctricas del mismo, como tensiones y corrientes.

Una vez que el ingeniero ha creado un diseño y verificado que es correcto, utilizará una herramienta de diseño para crear una descripción del diseño utilizando un lenguaje de alto nivel. La herramienta de diseño convierte el diseño en una descripción a nivel de silicio con un layout. El ingeniero utilizará la descripción a nivel de silicio para crear un chip de silicio que implemente el diseño…

Técnicas de codificación RTL

Hay una serie de técnicas de codificación que los ingenieros pueden utilizar para crear un diseño RTL exitoso. Entre ellas se incluyen las siguientes:

- Placement & Routing: es el proceso de colocar componentes como estarían en el silicio y optimizar el diseño del silicio para que sea lo más eficiente posible en todos los aspectos.

- Estimación del retardo: es una parte importante de la colocación y el trazado. Consiste en calcular el tiempo que tardan las señales en atravesar el silicio. Si alguna señal se retrasa a la entrada de alguna unidad, esto puede crear un error fatal, ya que tomará el valor previo (fuese 0 o 1) y dará una salida errónea. Por ejemplo, imagina un sumador de dos entradas o bits (A y B) y cuya salida (S) dará el resultado de la suma. Si la entrada A tarda más en llegar que la entrada B, A podría estar tomando un valor previo para la suma y S sería incorrecto.

- Cierre de temporización: es el proceso de determinar cuándo todas las señales del diseño cumplen sus requisitos de temporización y funcionarán correctamente en el circuito.

- Simulación: es el proceso de comprobación de la funcionalidad del diseño. Es útil para encontrar errores en el diseño.

Herramientas y recursos de diseño RTL

El proceso de creación de diseños digitales es complejo y requiere diversos conocimientos y herramientas como ya hemos visto anteriormente. El avance en este tipo de herramientas está haciendo que el diseño sea cada vez más simple, pese a que los chips son cada vez más complejos.

Actualmente también se está empezando a emplear otras ayudas para crear mejores diseños. Por ejemplo, la IA o inteligencia artificial también está interviniendo para quitarle trabajo a los arquitectos de chips o ingenieros diseñadores.