La memoria HBM está dando mucho que hablar, y será una compañera que estará entre nosotros por mucho tiempo, especialmente en el sector del HPC, pero también en el PC. Y es que, el ancho de banda y la latencia de la memoria volátil se ha transformado en factores imprescindibles a la hora de mejorar el rendimiento de unidades de procesamiento como la CPU y la GPU. Y es eso lo que esta memoria viene a resolver…

¿Qué es HBM?

HBM son las siglas de High Bandwidth Memory, es decir, memoria de alto ancho de banda. Este tipo de memoria es una especie de memoria volátil de acceso aleatorio, es decir, una RAM. Como tal, puede ser usada para alimentar de datos e instrucciones a unidades de procesamiento tales como la CPU o la GPU.

Ten en cuenta que muchos chips de GDDR para las GPUs, se apilan juntos y se empaquetan para conseguir una matriz combinada de DDR de gran capacidad y un alto ancho de bits.

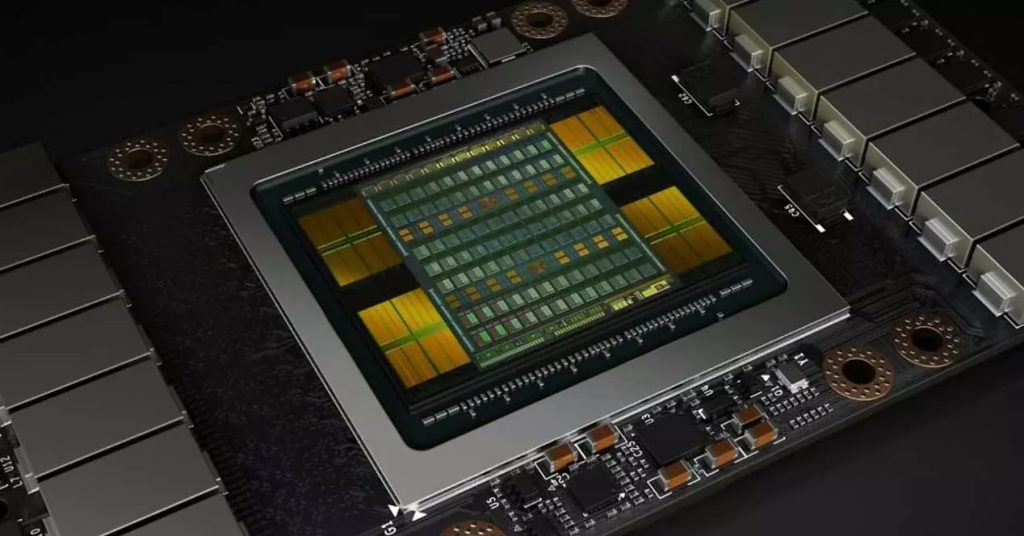

Generalmente, estos chips de HBM usan un máximo de 4 capas por cada pila tridimensional, y en pilas de 2, 4 u 8. Esta complejidad de fabricación las hace caras de producir, por eso no son tan frecuentes como las DDR. Pero NVIDIA las usa en sus productos para centros de datos, AMD también lo hace, e incluso en el caso de las Radeon, también la usaron en las Fuji para PCs, en vez de la GDDR, aunque después volvieron a la GDDR como NVIDIA. Intel y AMD, entre otros, también las usan para sus CPUs para HPC.

Conforme madure la tecnología y se hagan más baratas, no será extraño que podamos ver estas memorias HBM también en otros productos de consumo. Por el momento, se está optando por otras soluciones en la jerarquía de memoria, como la SDRAM. Sin embargo, la HBM conseguiría un ancho de banda muy superior a la DDR o GDDR actuales.

En el caso de la HBM, hay que decir que se usan chips basados en celdas DRAM, y que están apilados en 3D quemo he mencionado anteriormente. Además, existen varias versiones, como las que puedes ver en la siguiente tabla:

| Especificaciones | HBM1 | HBM2 | HBM3 |

|---|---|---|---|

| Densidad por troquel | 2 GB | 8 GB | 16 GB |

| Velocidad máxima por pin | 1 Gbps | 2 Gbps | 6.4 Gbps |

| Nº de chips apilados | 4 | 2/4/8 | 4/8/12/16 |

| Ancho de banda por chip | 128 GB/s | 256 GB/s | 819 GB/s |

| E/S interface | CMOS | CMOS | Interfaz de bajo voltaje |

| Consumo | Menor que la GDDR5 y GDDR5X | Menor que la HBM | — |

| Fabricantes | Hynix, Samsung, Nvidia | Samsung, Hynix | Samsung, Hynix,… |

| Apariencia | Cubo | Cubo | Cubo |

| Usado en estos modelos de tarjetas gráficas | Radeon R9, Fury X, Radeon Pro Duo | Nvidia Tesla P100, Nvidia Quadro GP100, Radeon Rx Vega 56, Radeon Rx Vega 64, Nvidia Titan V, AMD Radeon VII | — |

¿Se podría usar para la CPU?

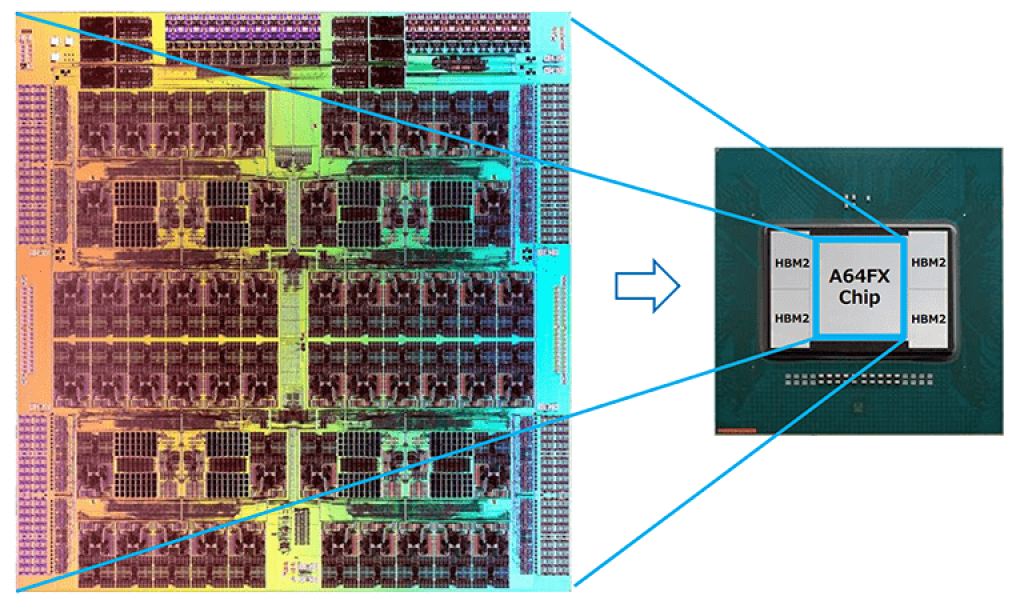

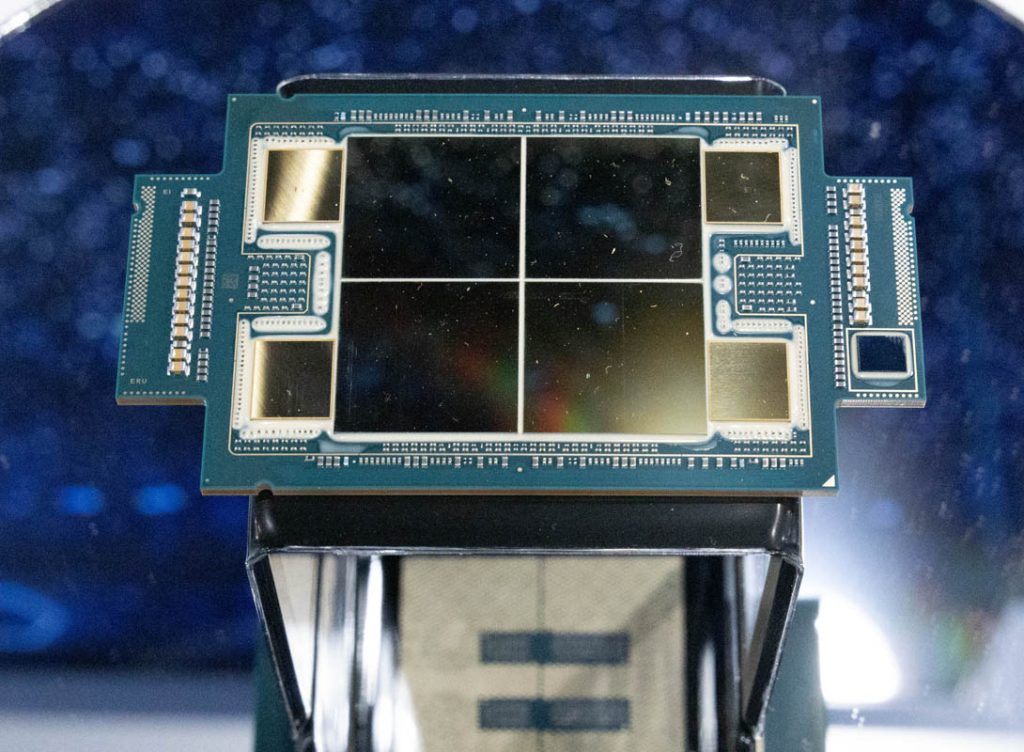

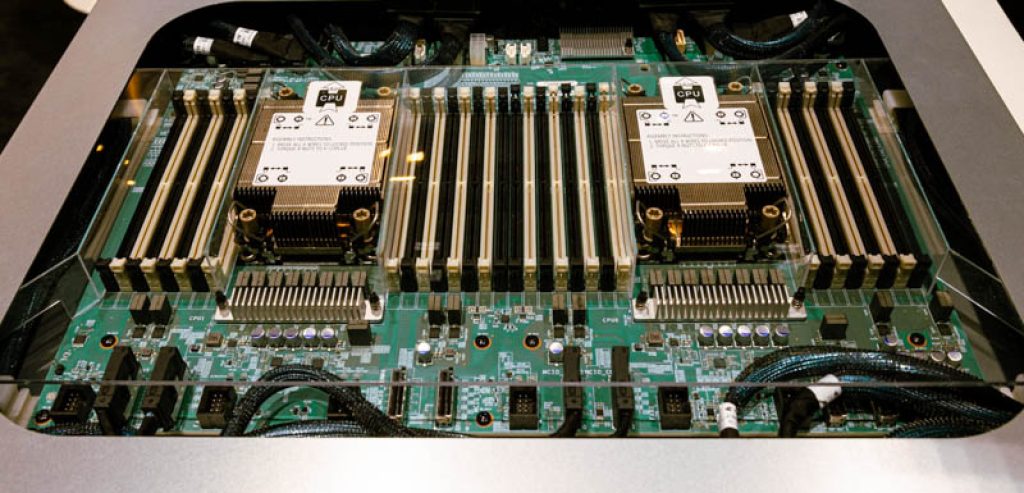

Como he dicho antes, la HBM se puede emplear tanto para la GPU como para la CPU e incluso para otras unidades de procesamiento. No tiene límites en ese sentido. Sin embargo, en el mundo del PC no existen CPUs con HBM, pero sí que existen en el caso del HPC, como el Intel Xeon Sapphire Rapids, el Fujitsu A64FX, el NEC SX-Aurora TSUBASA, etc. Y llegarán más…

También con los nuevos desarrollos de IA se está popularizando este tipo de memoria HBM, ya que en estas aplicaciones, tipo Chat-GPT, se necesita un gran ancho de banda de la memoria y una gran potencia de cálculo FP simple.

En cambio, en el ámbito del cliente, no será fácil ver una CPU con HBM a corto plazo por cuestiones de costes, aunque no hay que descartarlo para un futuro. De hecho, este tipo de memoria podría ser un sustituto de la RAM que traería un rendimiento mayor.

Los secretos de la HBM

Como hemos dicho, la HBM es un tipo de memoria que logra un mayor ancho de banda de transmisión sin incrementar su tamaño. Además, puede tener mayor eficiencia que las memorias DDR y GDDR convencionales.

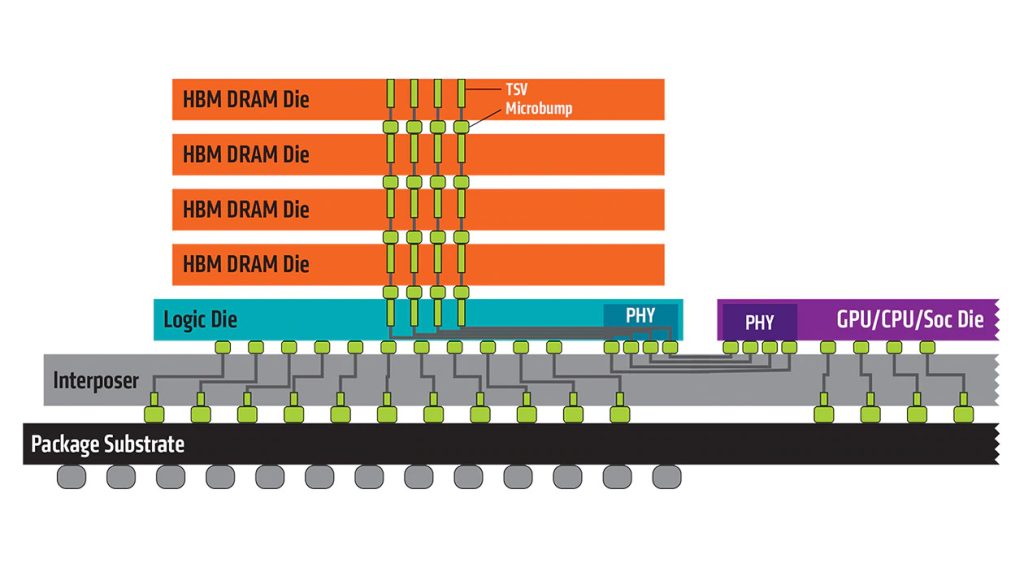

Para conseguir esto, el empaquetado de la HBM consta de varias capas de chips DRAM. Es decir, es un empaquetado 3D con interconexiones entre los chips gracias a la tecnología TSV (Through Silicon Via) y microbump, que consiste en escavar en los chips unos pilares para interconectar otros pisos apilados, usando también unas microbolas similares a las de un BGA.

Además del empaquetado HBM de memoria, también se empleará una capa, que es la inferior, con un chip lógico que se encarga de controlar esta memoria. Luego, esta capa de control se interconectará con la CPU o la GPU de forma diferente a como se hace con la GDDR o DDR. Y es que, en vez de estar situada en la PCB, normalmente se interconecta mediante un interposer. Todo esto se puede apreciar bien en la imagen superior.

A partir de esta estructura, se puede conseguir ese ancho de banda superior que se quiere. Y es que la cantidad de contactos interconectados es mucho mayor que la cantidad de líneas que conectan la memoria en un chip DDR y que van hacia la CPU/GPU. Es decir, la interfaz PHY de la HBM está a un nivel superior que la interfaz de la DDR.

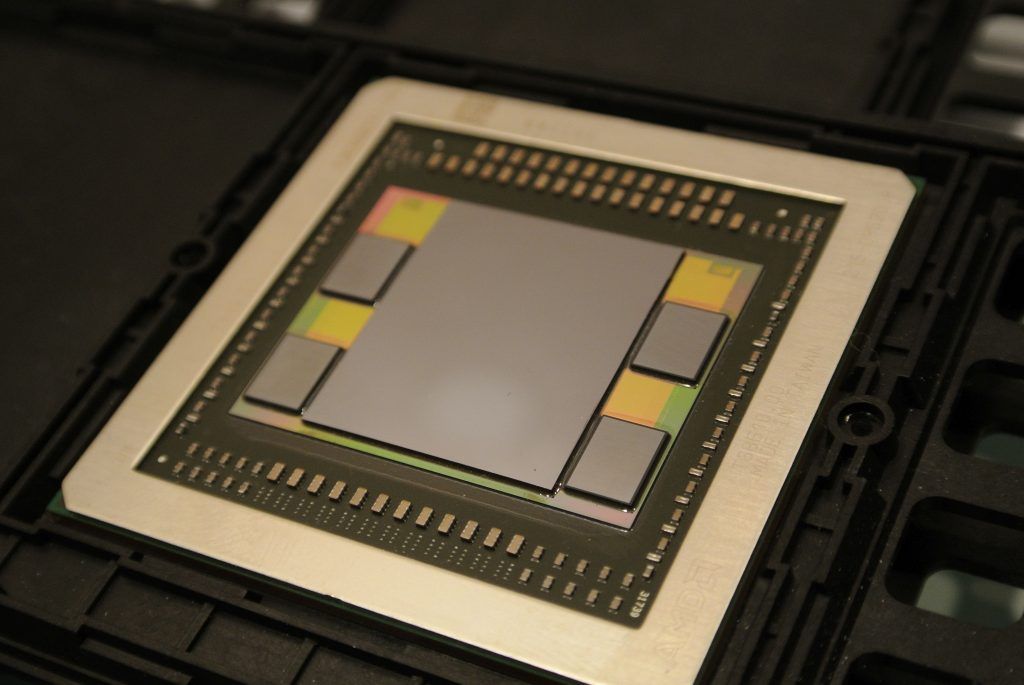

Por ejemplo, desde el punto de vista de cada capa DRAM, se pueden conseguir dos canales de 128-bit de ancho, lo que supondría llegar a los 1024-bit en caso de tener cuatro capas. Si a esto sumamos la cantidad de empaquetados que tenemos de HBM, se multiplicará aún más. Por ejemplo, algunos ejemplos de CPUs y GPUs vistos anteriormente están rodeados por 4 piezas HBM, lo que sería un total de 4096-bit en este caso.

A modo de comparación, cada canal de la memoria GDDR5 tiene un ancho de 32-bit y 16 canales tienen un total de 512-bit. Y hay que tener en cuenta que lo dicho en el párrafo anterior es para la HBM, si tenemos en cuenta la segunda generación, la HBM2, se pueden apilar hasta 8 capas, y cada pila de HBM2 admite hasta 1024 pines de datos, lo que podría hacer que cada capa alcance una velocidad de transferencia de 2000 Mbit/s.

Y no solo tenemos estas ventajas, también hay otras, como su capacidad teórica para conseguir una mayor eficiencia de transmisión, es decir, emplear menos energía por cada bit transferido. ¿Todo ventajas? Pues la verdad es que, como todo en la vida, también tiene sus desventajas…

Desventajas de la HBM

AMD inició el desarrollo de esta memoria HBM en 2008 por primera vez. La intención original de esta compañía era la de lanzar esta memoria para el mercado de consumo, como hizo con algunos modelos de tarjetas gráficas. En cambio, AMD ha vuelto atrás, tratando de resolver algunos problemas técnicos del apilamiento de los chips de memoria. Y gracias a los socios como SK Hynix, Micro Technologies, o Samsung, se han hecho grandes avances al respecto.

Los empaquetados 3D ya son bastante frecuentes, los hemos visto en los AMD Ryzen con 3D V-Cache, por ejemplo, y ahora la tecnología está más madura. De hecho, los chips HBM fabricados por SK Hynix en 2013 fueron un paso muy importante. Hasta tal punto que se adoptaría como un estándar de JEDEC, el JESD235.

En 2015, esta memoria HBM fue usada por primera vez en el mercado de consumo en la tarjeta gráfica AMD Radeon R9 Fury X. Y, al año siguiente, Samsung comenzó a producir en masa los nuevos HBM2 para las NVIDIA Tesla P100 para HPC.

Todo era muy esperanzador, pero no todo son ventajas. Por la propia arquitectura de la HBM, no es difícil ver que le falta flexibilidad a la hora de alojarla. Por ejemplo, en HBM no habría posibilidad de expansión como con los módulos DDR. Además, tampoco se podría sustituir una HBM por otra con especificaciones diferentes como sí se puede hacer con los módulos DDR, ya que podrías sustituir una DDR5-3200 por una DDR5-4800 si está soportada… Y eso complicaría la vida a los fabricantes OEM y a los usuarios.

¡Ojo! En el caso de la LPDDR, que son de bajo consumo, suelen estar soldados a la PCB o placa base, por lo que tampoco se podrían sustituir… En el caso de Apple M-Series, también han optado por incluir una cantidad determinada de memoria RAM, por lo que también anulan esta flexibilidad de la DDR.

Por eso, muchos de los principales creadores de CPUs, no están pensando actualmente en usar estos chips HBM para impulsar el mercado masivo. Entre otras cosas, porque sería más complicado lanzar diferentes modelos o SKUs con varias capacidades de HBM.

Baja capacidad

Por otro lado, también hay que destacar otro detalle importante a tener en cuenta, y es que su capacidad está también más limitada. Mientras en la DDR se pueden agregar más troqueles en un módulo, en la HBM soldada esto está más limitado, y también depende mucho de la generación de HBM, y sus límites de capas. Por ejemplo, si tenemos una HBM que puede apilar 8 capas de chips DRAM y cada uno es de 8 Gbit, entonces tendremos un total de 8 GBytes. Para hacerte una idea, en los productos de HPC, se suelen usar capacidades de 32 GB de memoria, lo que perfectamente podría igualar cualquier portátil o PC de sobremesa gaming convencional…

Esta capacidad aún sigue siendo demasiado pequeña para muchos casos en los que se necesita un PC con capacidades de 64, 128 GB, etc. Además, a esto hay que agregar los precios más baratos de la DDR4/5 y que muchos fabricantes ya están usando éstos también apilados para conseguir mejoras en los módulos de gama alta, como en los RDIMM.

Por supuesto, HBM y DDR se pueden mezclar, es decir, no es un sustituto, sino que puede ser un complemento. Viendo esto desde esta perspectiva, se podría entender la HBM de una CPU como si fuese una especie de memoria cache L4, que tendría relación directa con la RAM principal.

Alta latencia de acceso

Otra de las desventajas de la HBM está en la latencia de acceso de esta memoria. Es decir, la cantidad de ciclos de reloj de la unidad de procesamiento que se necesitan para realizar un acceso (lectura o escritura). Es cierto que la latencia es razonablemente buena, pero no tanto como con la DDR en muchos casos.

La memoria DDR contemporánea generalmente está marcada con CL (latencia CAS, el número de ciclos de reloj requerido para el direccionamiento de columnas, que indica la duración de la latencia de lectura). El retraso de CAS del que estamos hablando aquí se refiere al tiempo de espera entre el momento en que se emite el comando de lectura y los datos están listos.

Después de que el controlador de memoria le dice a la memoria que necesita acceder a los datos en una ubicación específica, mediante señales de control, se necesitan varios ciclos para llegar a la ubicación y ejecutar las instrucciones emitidas por el controlador. CL es el parámetro más importante en la latencia de la memoria. En términos de la duración de la demora, el «período» aquí en realidad debe multiplicarse por el tiempo por ciclo o periodo (cuanto mayor sea la frecuencia operativa general, menor será el tiempo por ciclo).

Para HBM, una de sus características como se mencionó anteriormente es el ancho de interconexión ultra amplio, lo que determina que la frecuencia de transmisión de HBM no pueda ser demasiado alta. De lo contrario, el consumo total de energía y calor no se podría controlar.

De hecho, la frecuencia de HBM será mucho más baja que la de DDR/GDDR. Por ejemplo, la memoria usada por AMD en 2015 tenía solo 500 Mhz. La memoria Flarebolt HBM2 anterior de Samsung tiene un ancho de banda de transmisión de 2 Gbit/s por pin, una frecuencia de 1 GHz. Más tarde e lanzaron algunos productos que pueden llegar a 1,2 GHz, pero no mucho más que eso.

¿Podría sustituir a la memoria RAM actual?

Las características de alto ancho de banda y alta latencia determinan que HBM sea muy adecuada como memoria de GPU porque los juegos y el procesamiento de gráficos en sí mismos son tareas altamente predecibles y concurrentes. Además, este tipo de aplicaciones no son tan sensibles al retardo.

Sin embargo, para usar con la CPU, es algo más complejo, ya que las tareas que ejecuta esta unidad pueden ser muy diversas, y no es tan predecible como en la GPU. Además, en estos casos sí que son más sensibles a los retardos. Por eso solo se suele usar en casos de HPC, o para aplicaciones como IA, donde sí que son apropiados.

En definitiva, para un PC para un usuario convencional, la HBM no sería la mejor opción en la actualidad debido a la latencia y a los límites de capacidad, además de su elevado precio. Sin embargo, salvando alguna de estas barreras, se podría usar en un PC en un futuro. No obstante, no sería para sustituir a la DDR, sino como un complemento más en la jerarquía de memoria como he mencionado antes.

Si algún día llega, o mejor dicho vuelve, sería antes para una GPU de gama alta que para una CPU.

Sin embargo, no tenemos una bola de cristal para predecir lo que ocurrirá en el futuro del PC. Pero no sería extraño que se comenzaran a crear soluciones híbridas HBM/DDR en unos años…

HBM3: una esperanza

Desde los PCs hasta los dispositivos móviles e incluso los de IoT e IA, se podrían beneficiar de futuros desarrollos de la HBM. Por el momento, las aplicaciones de IA y HPC son las que se están nutriendo de las ventajas que puede tener este tipo de memoria, sin importar el coste, ya que se trata de sistemas de alto rendimiento donde los costes no son un problema principal.

Además, el futuro de la HBM parece prometedor, especialmente tras conocer la tercera generación denominada HBM3. Esta memoria podría solventar algunos problemas de sus anteriores generaciones.

Hay que aclarar que a finales de 2018, JEDEC también anunció otra nueva actualización intermedia entre la HBM2 y la HBM3 denominada como HBM2E. Se trata de una mejora con mayor ancho de banda y capacidad. Esta especificación puede admitir hasta 307 GB/s por pila, con una velocidad efectiva de 2.5 Tbit/s. Además, se agregó soporte para hasta 12 capas o niveles de altura, lo que permite llegar a 24 GB por pila. Samsung fue una de las primeras en crear su chip HBM2E, y más tarde llegaría el de SK Hynix, consiguiendo cifras de rendimiento muy impresionantes.

HBM3 es ya una realidad, y los principales fabricantes de memoria ya han creados sus productos. Rambus fue uno de los primeros en anunciar un subsistema compatible con HBM3, y luego vendría la memoria HBM3 de SK Hynix en 2021. También Synopsys anunció una solución completa de verificación e IP para esta industria, colocando otra nueva pieza del puzle para tener esta HBM3 en producción masiva.

Hay que decir que la memoria de SK Hynix inicial, consiguió un rendimiento de 665 GB/s de ancho de banda, y una velocidad de E/S superior a 5.2 Gbps. Y parece que esos no son los límites, y que se puede exprimir aún más. Rambus, de hecho, anunció un sistema de hasta 8.4 Gbps y ancho de banda de hasta 1,075 TB/s.

En junio de este año, Taiwan Creative Electronics lanzó una plataforma de red/AI/HPC basada en la tecnología CoWoS de TSMC, equipada con un controlador HBM3 y PHY IP, con una velocidad de E/S de hasta 7,2 Gbps. Creative Electronics también está solicitando una patente de cableado de interposición, que admite cableado en zigzag en cualquier ángulo y puede dividir el HBM3 IP en dos SoC para su uso.

La solución IP HBM3 completa anunciada por Synopsys proporciona un controlador, PHY e IP de verificación para un sistema de paquete de chips múltiples 2.5D, lo que indica que los diseñadores pueden usar memoria con bajo consumo de energía y mayor ancho de banda en SoC. El controlador DesignWare HBM3 y PHY IP de Synopsys se basan en el HBM2E IP probado con chip, mientras que el HBM3 PHY IP se basa en el proceso de 5 nm. La velocidad de cada pin puede alcanzar los 7200 Mbps y el ancho de banda de la memoria se puede aumentar a 921 GB/s.

Actualmente, Micron Technologies, Samsung Electronics, SK Hynix, y otros fabricantes de memoria, ya están siguiendo este nuevo estándar DRAM. El diseñador de SoC Socionext ha cooperado con Synopsys para introducir HBM3 en su diseño de chips múltiples, además de la arquitectura x86 que debe ser compatible, la plataforma Neoverse N2 de Arm también ha planeado admitir HBM3, y el SoC RISC-V de SiFive también ha agregado HBM3 IP. Pero incluso si JEDEC no está «atascado» y lanzó el estándar oficial HBM3 a finales de año, es posible que tengamos que esperar hasta la segunda mitad de 2022 para ver los productos relacionados con HBM3 disponibles.