En la era actual de la informática, donde la demanda de potencia de procesamiento y capacidades avanzadas no conoce límites, los chips de gran tamaño emergen como protagonistas destacados en la vanguardia de la innovación tecnológica. Estos colosos microelectrónicos, cuyas dimensiones exceden los estándares convencionales, están redefiniendo los límites de lo posible en términos de rendimiento y funcionalidad. En este artículo, nos sumergiremos en el fascinante mundo de estos mega chips, y mostraremos los motivos que hay para crear estos dispositivos cuando la corriente predominante es hacer justo lo contrario, tratar de hacerlos cada vez más pequeños…

¿Qué es WSI?

Wafer Scale Integration, o WSI, es un sistema muy poco conocido y raramente utilizado para construir redes de circuitos integrados muy grandes, es decir, esos mega chips de los que comentamos en la introducción de este artículo.

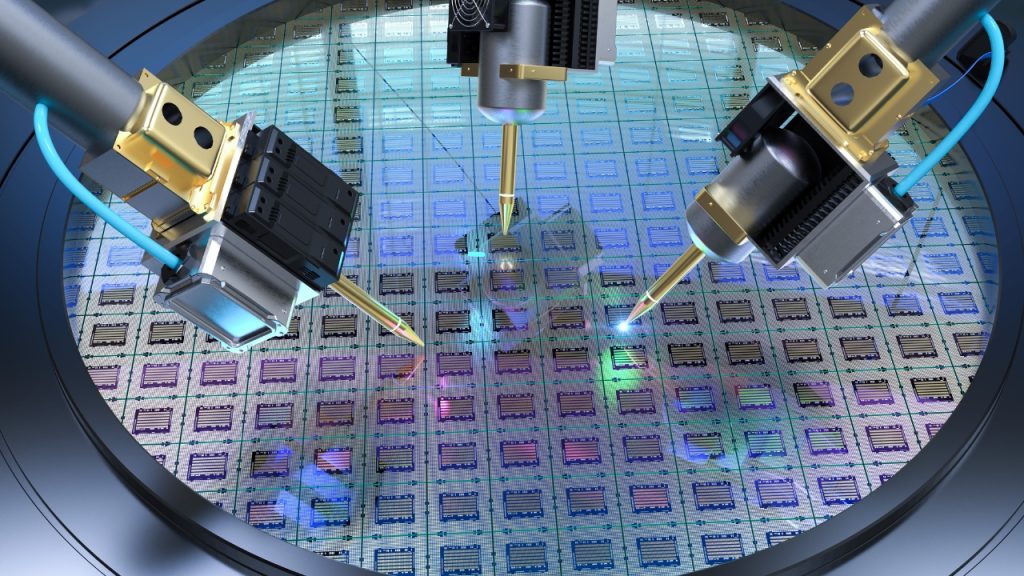

Como bien sabrás, los chips se fabrican en obleas o wafers, dependiendo de su tamaño o área ocupada, pueden salir 100, 200 o 300 chips por oblea perfectamente. En cambio, en este caso tenemos un solo chip por oblea, es decir, el chip ocupa toda la oblea de la superficie, y esto es lo que denominados superchip o mega chips.

Cuando se empezó a pensar en este tipo de diseño con un tamaño grande y un solo empaquetado para todo el wafer, la idea era reducir enormemente los costes de producción, ya que se podía fabricar todo el sistema en un solo wafer y así evitar la necesidad de otros chips o PCBs adicionales. Además, se pensó que podría ser muy útil para la supercomputación paralela, al poder crear en un mismo wafer muchas unidades de procesamiento trabajando juntas e interconectadas de una forma más rápida y eficiente que si se separan en chips individuales.

No obstante, esto no ha sido así en la práctica, y al final muchos de los proyectos basados en WSI han terminado desechándose por todo lo contrario, se han encontrado con costes muy elevados debido al yield, que en este caso tiene que ser del 100%, lo cual podría significar desechar obleas completas hasta conseguir un diseño funcional completo.

Ten en cuenta que cuando se fabrican chips convencionales, al tener una centena o varias centenares de ellos en una oblea, si el yield no es del 100%, puedes descargar los chips que han surgido defectuosos y realizar el llamado binning en los demás. Sin embargo, cuando hablamos de todo un sistema que debe trabajar en conjunto, esto ya no es así, ya que si falla alguno de los elementos esenciales, se debe descartar toda la oblea completa.

Es decir, la economía de producción en masa de chips convencionales se basa en que la venta del resto de chips que no han resultado defectuosos tras los tests puedan compensar los costes de fabricación y generar una ganancia adicional. En cambio, esto no resulta así si el chip es de mayor tamaño. Como hemos podido ver, en los chips con un área de superficie grande tenemos precios del producto final muy elevados por el menor yield, y mientras el número de núcleos crece y la superficie, peor es este yield. Es por eso que muchos diseñadores de chips han comenzado a utilizar los llamados chiplets en MCM, como es el caso de AMD, o más recientemente Intel en su 14ª Gen.

Pero, a diferencia de esto, en vez de hacer los chips lo más pequeños posibles para mejorar el yield y reducir los costes, en un WSI tenemos todo lo contrario. Sin embargo, sí que se puede ahorrar en otras áreas de producción, como en las pruebas individuales de los chips, que en este caso se hacen solo a nivel de oblea, el corte o separación de los chips, ya que solo tendríamos uno, y el empaquetado, que se empaquetaría todo en un mismo encapsulado y no en cientos de ellos.

Por supuesto, esto no es fácil, ya que, dadas las imperfecciones en las obleas, un diseño grande impreso en una oblea casi siempre no funcionaría. Ha sido un objetivo continuo desarrollar métodos para manejar áreas defectuosas de las obleas a través de la lógica, en lugar de cortarlas de la oblea. En general, este enfoque utiliza un patrón de rejilla de subcircuitos y una red de interconexión entre ellos para así poder desactivar las partes afectadas y que solo funcionen las que se han fabricado bien, y así pueda usarse estos mega chips pese a que haya subcircuitos defectuosos.

Además, hay que agregar que uno de los procesos que más fallos aporta es el proceso de metalización en las capas que interconectan los transistores en las primeras capas. Para esto hay que generar métodos innovadores para poder reducir estos fallos y tratar de interconectar de forma correcta pequeños chiplets implementados en la oblea para que funcionen todos como un único chip.

Los desafíos superaban a la tecnología de la década de los 70 y 80, donde muchas empresas trataron de crear sistemas WSI, pero todos estos proyectos terminarían fracasado. Uno de los primeros en intentarlo fue Texas Instruments, que pensaba crear microprocesadores complejos y así volver a ingresar en este mercado donde había perdido terreno frente a otros competidores en esta época. Pero finalmente no consiguieron lanzar ningún producto viable al mercado.

El propio Gene Amdahl, el que daría nombre a la famosa ley, también trataría de implementar WSI para poder construir un supercomputador en un solo chips. Para ello fundó la compañía Trilogy Systems en 1980, y consiguieron inversiones de Digital Equipment Corporation, Sperry Rand y Groupe Bull por el gran interés en este tipo de proyectos. Amdahl pensó en un diseño de un chips de 2.5 pulgadas de ancho y con 1200 pines en la parte inferior, algo muy elevado para esta época. Sin embargo, el proyecto estuvo plagado de una serie de desastres, incluso se llegó a inundar la planta de fabricación y se arruinó completamente la sala limpia de la foundry.

Tras el desastre, con lo que había sobrado del capital invertido compraron la compañía Elxsi, un fabricante de ordenadores compatibles con VAX de DEC en 1985, pero los objetivos no pudieron llegar a un buen puerto, y el interés por un WSI cesó. Más tarde llegaría otro intento por parte de Anamartic, una empresa de tecnología que quería crear una memoria de muy alta capacidad basada en la tecnología de Ivor Catt en 1989, pero no pudo garantizar el suministro suficiente de wafers y cerraría en 1992.

Hasta recientemente, no lo han vuelto a intentar, como veremos en el último apartado…

¿Qué es SoW?

En un SoC (System on a Chip) tradicional, todos los elementos, como procesador, memoria, controladores, y a veces incluso componentes específicos de la aplicación, se integran en un solo chip. Esto permite reducir el tamaño, menor consumo de energía y, a menudo, reduce los costes en comparación con sistemas que requieren múltiples chips, así como un mejor rendimiento al ser un diseño monolítico.

Pues bien, se conoce como System on Wafer (SoW) a un wafer u oblea que contiene todo el sistema. Es decir, un WSI en el que se integran todas las partes como en un SoC convencional, pero con un mayor tamaño, y con las ventajas que esto supone, así como las desventajas ya citadas en el apartado anterior. Es decir, SoW sería un concepto relacionado con el SiP que analizaré en el siguiente apartado.

Como sabrás, la integración de sistemas y la miniaturización ha sido una obsesión durante los últimos años, hasta llegar a los actuales SoCs disponibles en multitud de equipos actuales o los denominados SiP. Sin embargo, con los sistemas de alto rendimiento, los aceleradores para IA y la integración heterogénea, se ha dado paso hacia un enfoque WSI conocido como SoW, donde el sistema es mucho más complejo y se implementa sobre uno de estos mega chips que ocupará toda la oblea.

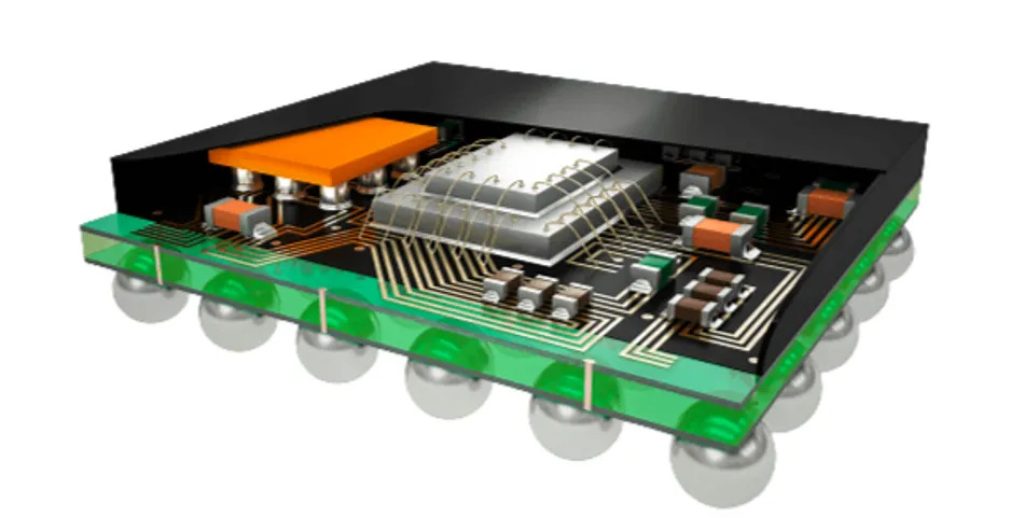

Para llevar a cabo el SoW, se necesita un conjunto tecnológico específico que incluya todas las tecnologías de envasado estándar, como el flip chip, la rerouting de señales y la integración de componentes pasivos, así como nuevas tecnologías avanzadas como los sistemas microelectromecánicos, interconexiones avanzadas, integración de fuentes de energía, refrigeración integrada o a través de vías de silicio.

Hoy en día, se han desarrollado varios enfoques diferentes para realizar el empaquetado en 3D, incluidas tecnologías como el sistema en paquete (SiP), sistema en chip (SoC) o sistema en paquete (SoP). Si embargo, CAE-LETI ha sido el que ha desarrollado este nuevo concepto para la integración heterogénea que se llama sistema en oblea (SoW). Y para ello se han valido de tecnologías como TSV, mejoras en el grabado DRIE y la fotolitografía, nuevo software EDA, etc.

¿Qué es SIP?

Un System in Package (SiP) es una técnica de diseño y fabricación en la que varios componentes electrónicos individuales se integran en un solo paquete para formar un sistema completo. En lugar de tener componentes discretos separados en una placa de circuito impreso (PCB), los componentes se apilan y conectan dentro de un encapsulado más pequeño.

En un SiP, los componentes pueden incluir microprocesadores, memorias, sensores, y otros dispositivos necesarios para realizar una función específica. Estos componentes pueden provenir de diferentes tecnologías o procesos de fabricación, y se combinan para formar un sistema funcional más compacto y eficiente.

Gracias a este diseño SiP, se pueden conseguir integrar en un menor espacio más funciones, desarrollar componentes más flexibles que diseñar algo para una función específica, reducir el espacio para aquellos sistemas IoT o embebidos donde esto sea importante, mejorar el rendimiento al reducir las distancias y latencias para las comunicaciones entre las distintas unidades, mejorar el rendimiento al estar todo más integrado, optimizar la eficiencia energética y mejorar la fiabilidad frente a componentes separados.

Los SiP se utilizan en una variedad de aplicaciones, como dispositivos electrónicos portátiles, sistemas de comunicación inalámbrica, dispositivos médicos, reproductores multimedia portátiles, y muchos otros productos electrónicos donde la eficiencia del espacio y el rendimiento son fundamentales.

¿Qué es WLP?

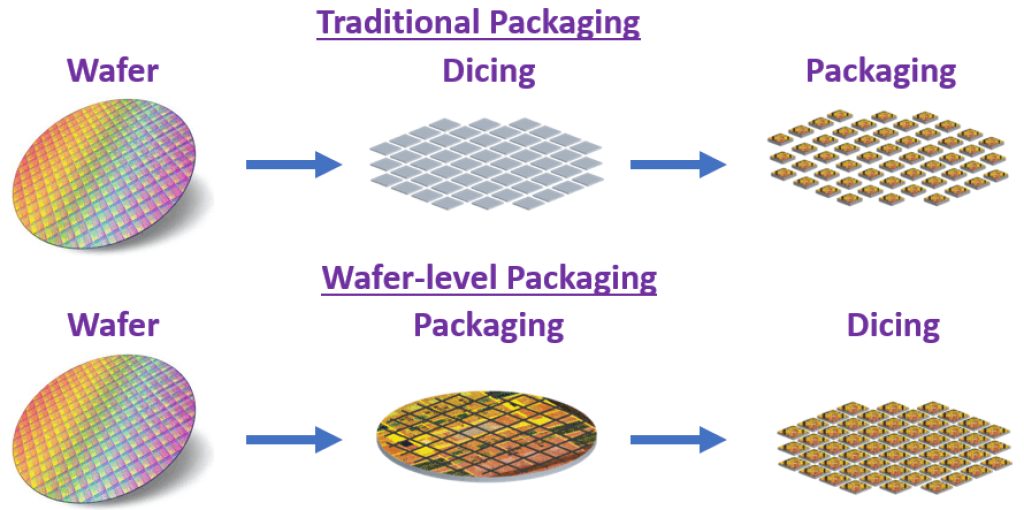

No hay que confundir WSI con lo que se denomina como WLP, ya que son conceptos diferentes, como podrás comprobar aquí. Se denomina WLP o Wafer Level Packaging a un método en el cual los chips se encapsulan antes de que la oblea sea cortada o dividida en chips. Esto se diferencia del proceso convencional, donde primero se dividen los chips y luego se empaquetan por separado.

Por tanto, en el WLP, las capas superior e inferior y los puntos de soldadura se unen a los circuitos integrados mientras aún están en la oblea. Y este tipo de proceso se puede usar también para un WSI, por lo que también es importante conocer de qué se trata.

Básicamente WLP es un CSP (Chip Scale Package), ya que el empaquetado resultante es prácticamente del mismo tamaño que el chip. Sin embargo, este tipo de proceso permite que el empaquetado se haga por lotes, al igual que las pruebas tras el empaquetado de cada chip y también el marcado, frente a tenerlo que hacer con los chips separados.

Un área de aplicación importante de los WLP son los smartphones debido a las restricciones de tamaño. Por ejemplo, dispositivos como el Samsung Galaxy, Apple iPhone, etc., tienen varios chips que usan este mismo empaquetado WLP. Las funciones proporcionadas por los WLP en los dispositivos móviles es muy variada, incluyen sensores, gestión de energía, conectividad inalámbrica, etc. E incluso se pueden usar para diseños MEMS, como algunos rumores que apuntan a que empresas como Apple podrían usar este tipo de empaquetado para un sistema de refrigeración mucho más pequeño.

Algunas empresas que se dedican a realizar este tipo de empaquetados sobre las obleas ya fabricadas son OSAT, Advanced Semiconductor Engineering (ASE), etc. Este tipo de compañías ofrecen distintas soluciones de este tipo, como pueden ser:

- WL-CSP o WLCSP: es simplemente un chip desnudo con una capa de redistribución (RDL, interposer o paso de E/S) para reorganizar los pines o contactos en el dado de modo que sean lo suficientemente grandes y tengan un espacio suficiente para ser manejados como un BGA para su montaje superficial.

- Fan-in: os paquetes WLCSP fan-in tienen un interposer del mismo tamaño que el dado,

- Fan-out: mientras que los paquetes WLCSP fan-out tienen un interposer más grande que el dado, similar a los empaquetados BGA convencionales, con la diferencia de que la interposición se construye directamente sobre el chip, en lugar de que el dado se adhiera a ella y se refleje mediante el método de chip invertido.

En ambos casos, el dado con su interposición puede estar cubierto con material encapsulante como una resina epoxi o similares. Sin embargo, este tipo de empaquetados a veces presenta problemas. Por ejemplo, la SBC Raspberry Pi 2 que usaba un empaquetado de este tipo tenía problemas con los destellos de luz de xenón y otras luces de onda larga, ya que producían un efecto fotoeléctrico dentro del chip por no estar protegido de forma adecuada mediante su empaquetado. No obstante, hablamos de una PCB desnuda, como es el caso de la Pi…

Ejemplos de proyectos de mega-chips

Después de toda esta teoría sobre WSI y estos mega chips, ahora toca poner algunos ejemplos, ya que estos diseños se han venido usando en algunos casos con éxito, pese a los primeros intentos fallidos que comenté anteriormente. Por ejemplo:

WSE de Cerebras

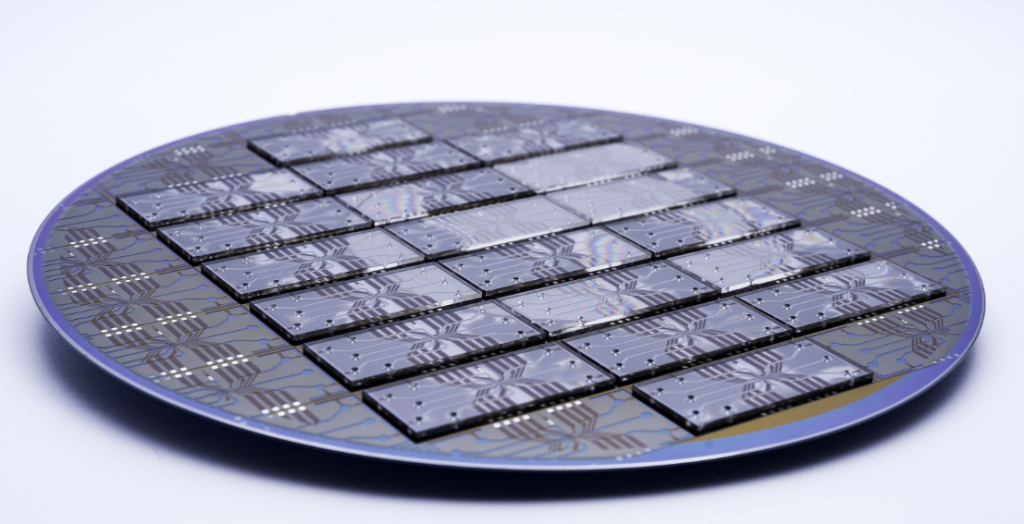

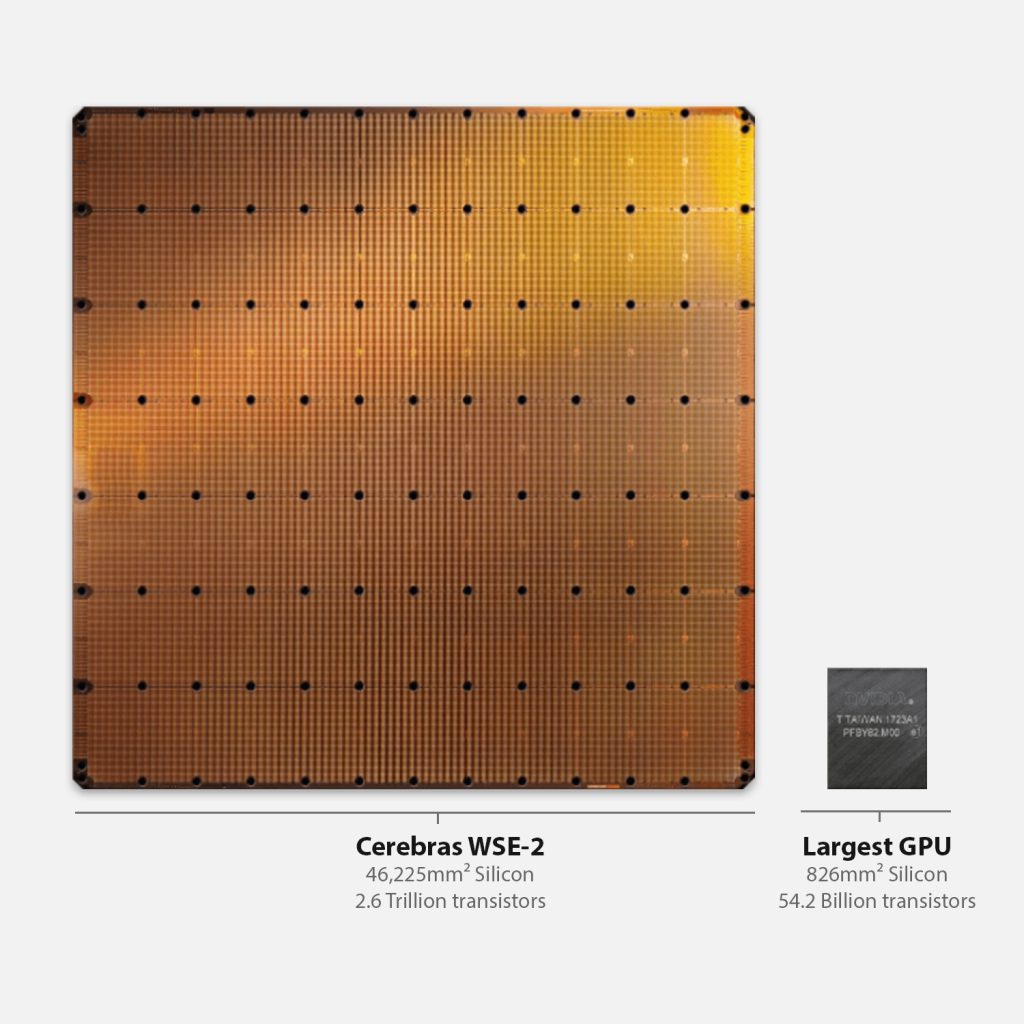

En 2019 una empresa denominada Cerebras Systems presentó un diseño WSI, un procesador muy potente que sería para acelerar cargas de aprendizaje profundo. Este diseño se denominó Wafer Scale Engine. Y la primera generación era un chip que ocupaba toda una oblea de 300 mm, con 46,225mm2 (215x215mm), lo que suponía 56 veces más grande que el chip de la GPU más grande de ese momento.

Esta oblea fue producida por TSMC y se utilizó el proceso de fabricación de 16 nm. El WSE-1 para el equipo CS-1 de Cerebras contenía nada menos que 1.200.000.000.000 transistores, con 400.000 núcleos de procesamiento AI, 18 GB de memoria SRAM (caché) on-chip, y una red de interconexión por todo el wafer que conseguía un ancho de banda de 100 Pbit/s, y hasta 1.2 PB/s para las comunicaciones fuera del wafer, es decir, para el E/S de este diseño WSI. Gracias a esto, el WSE de Cerebras era hasta 200 veces más rápido que el supercomputador Joule de NETL en CFD, y con menos consumo energético, ya que consume 15 kW, frente a varios MW que consume el Joule.

Más tarde llegaría la segunda generación, ya que en 2021, Cerebras presentaría el WSE-2, para el equipo CS-2, un sistema con el doble de transistores (2.6 billones de transistores) que el anterior y con un 100% de yield según Cerebras. Este otro diseño también se le encargó a TSMC con nodo de 7nm, y su producción en serie fue más exitosa. Este diseño contenía 850.000 núcleos de IA, 40 GB de memoria SRAM integrada, un ancho de banda de 20 PB/s a nivel E/S y hasta 220 Pb/s a nivel interno. Y, tanto la Gen 1 como la Gen 2 tenían exactamente el mismo área de silicio, 46.225 mm2.

Otros diseños

Aunque no existen demasiados diseños WSI, sí que ha habido intentos como he mencionado anteriormente. Y pronto estará aquí el Cerebras WSE-3, la tercera generación, que veremos qué nos depara, aunque por el momento no tiene fecha de presentación, ya se rumorea que podría usar tecnología de 5nm o 4nm. Pero será realmente impresionante como sus dos antecesores. Sin embargo, en un futuro próximo es probable que se conozcan más diseños dados los resultados de Cerebras. De hecho, compañías como IBM ya están con las puestas miras de combinar WSI y el 3D packaging, para usar varios niveles de wafers empaquetados y conectados a través de TSVs.

Las aplicaciones de estos mega chips WSI serán cada vez más, como puede ser para procesadores para sistemas HPC de paralelismo masivo, para memorias de gran capacidad, para sistemas tolerantes a fallos, y para cargas de IA para acelerar estas aplicaciones cada vez con mayor importancia.

Algunos diseños que ya están en marcha y que podemos citar de WSI son por ejemplo el proyecto ELSA europeo. Sus siglas pertenecen a European Large SIMD Array, y como su propio nombre indica, se trata de crear un procesador SIMD para cálculos en paralelo de tipo vectorial y que estará en una matriz 2D. Sin embargo, por el momento está en desarrollo y bajo experimentación.

Por otro lado, también existe otro caso europeo, se trata del Project 824, que también pretende usar la escala WSI para crear mega chips con hasta 25 millones de transistores por oblea de 4 pulgadas usando un enfoque jerárquico para implementar tolerancia a fallos. El proyecto se compondría de tres fases para probar la viabilidad de un diseño WSI:

- Memoria SRAM: de 4.5 Mbit con t iempos de acceso a 100ns para verificar la posibilidad de usar switches eficientes para descartar elementos defectuosos y que solo se puedan usar los funcionales para crear una red de interconexión final con este propósito, como ya usan sistemas como los citados anteriormente.

- Systolic Array: las matrices sistólicas son adecuadas para WSI porque todas las comunicaciones son entre los núcleos adyacentes o vecinos más cercanos. El enfoque adoptado fue definir una arquitectura de propósito general con aplicaciones como podría ser el procesamiento de imágenes, reconocimiento de objetos, dispositivos de memoria avanzados o de gran capacidad, aceleración de IA, y matrices de procesamiento tipo manycore.

- Microprocesador: básicamente es una CPU sencilla de 16 bits y con el objetivo a largo plazo era integrar un sistema completamente dedicado en un solo chip utilizando bloques predefinidos incrustados en una estructura de interconexión flexible (un mar de compuertas, por ejemplo).

La primera prueba de integración a escala de obleas se procesó con éxito. Y podían ser grabados para eliminar elementos innecesarios del WSI o para la reconfiguración según el objetivo de la aplicación.

Los entornos de desarrollo y CAD, así como las máscaras para la fabricación, y la testabilidad de este proyecto resultaron exitosos, y ahora el desarrollo técnico y el conocimiento adquirido podrá usarse para crear ASICs WSI o mega chips mucho más complejos…