Los semiconductores supusieron una enorme revolución y el transistor probablemente haya sido uno de los inventos más destacados de los últimos tiempos. Gracias a ellos se ha pidido impulsar la tecnología electrónica tal como la conocemos actualmente. Sin embargo, pese a que llevan muchos años entre nosotros, parece que tienen un futuro prometedor, aunque algo incierto…

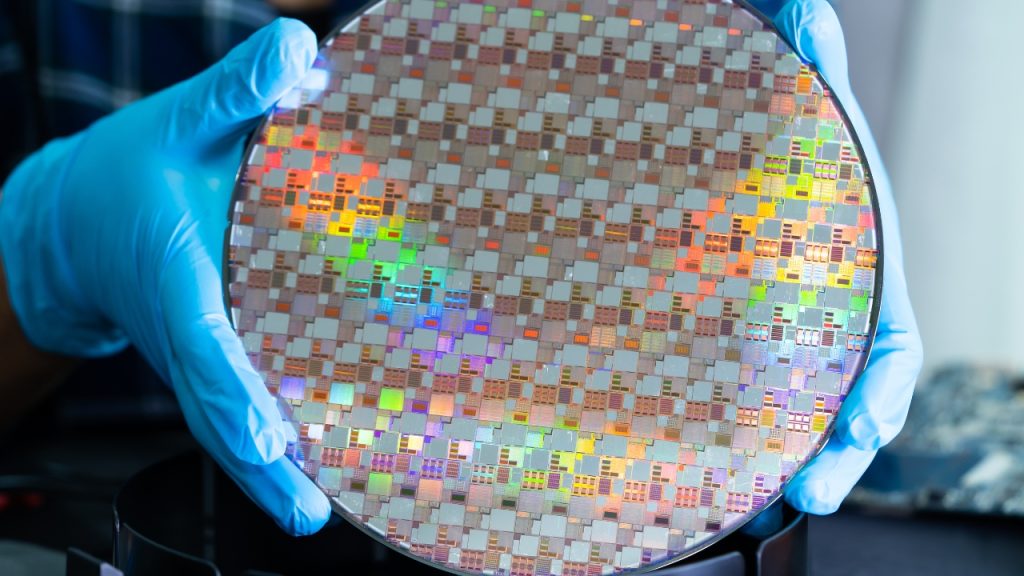

Los transistores que componen los chips de computo, lógica general y memoria actual deben tener unas características ideales, conduciendo la máxima corriente cuando se encienden, no permitiendo que fluya corriente cuando está apagado, y que sean capaces de conmutar lo más rápido posible. Además, deben poderse integrar con la máxima densidad posible y consumir la menor cantidad de energía posible. Pero esto no siempre es sencillo de conseguir. Por eso, la industria de los semiconductores es una de las más activas en cuanto a investigación y desarrollo.

Un poco de historia del transistor

Los tubos de vacío eran los dispositivos empleados para ordenadores de la época, sistemas de telecomunicaciones, etc. Sin embargo, estos tubos de vacío tenían varios graves problemas. Uno de ellos era que se podían fundir como las bombillas, por lo que había que estar sustituyéndolos de forma periódica. Otro problema es que a veces podían fallar, además de ser de un tamaño considerablemente grande, consumir gran cantidad de energía, se calentaban mucho, etc.

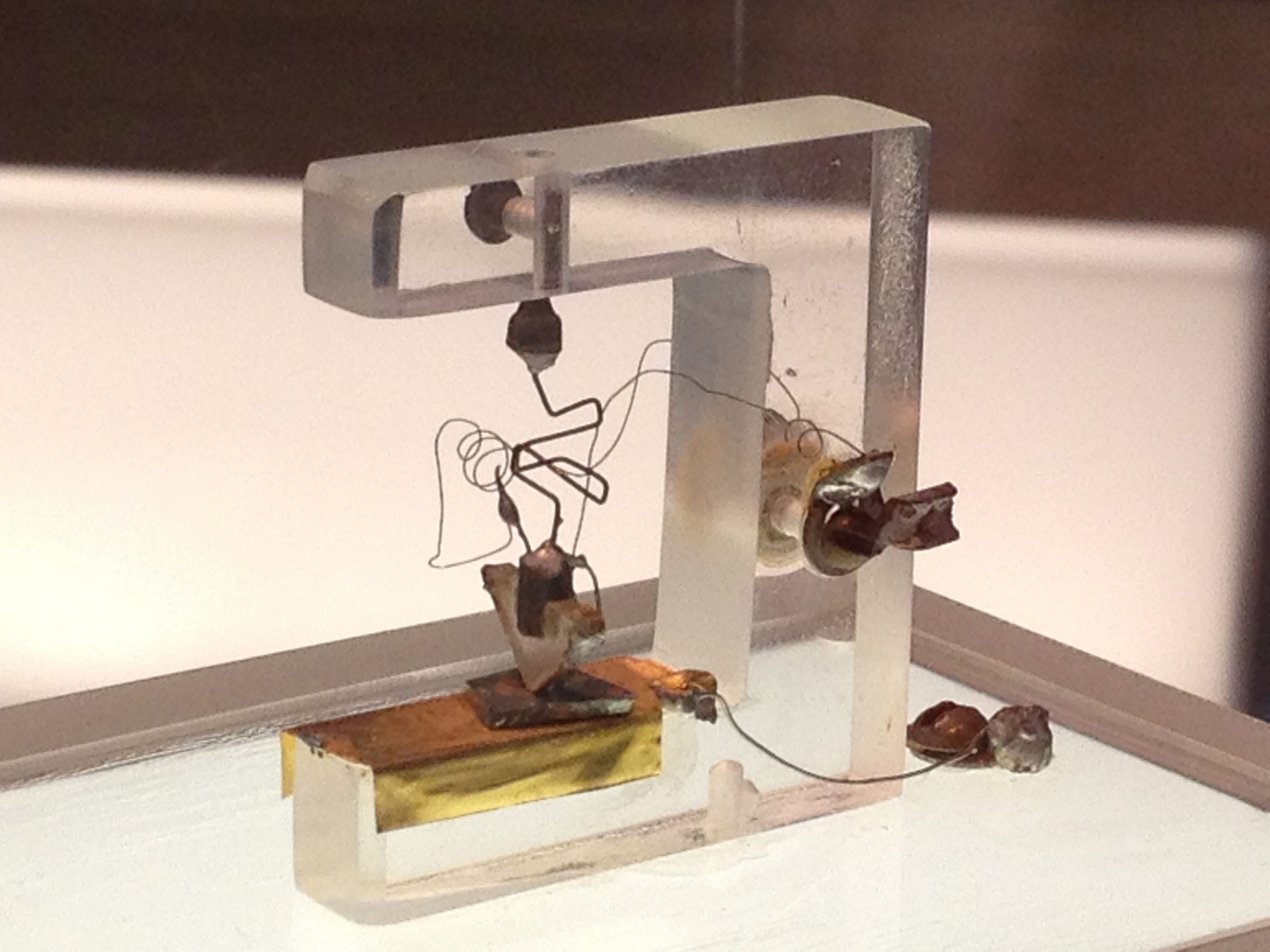

Por eso se pusieron a investigar para tratar de conseguir algo similar al tubo de vacío pero de estado sólido, es decir, los semiconductores. Y el primer fruto fue el transistor, que llegaría de la mano de Bell Labs, los famosos laboratorios de AT&T en aquella época. Y los que se reconocieron como sus inventores fueron John Bardeen, Williams Shockley y Walter Brattain, los tres ganadores del Premio Nobel.

El primer transistor era algo tosco, difícil de fabricar, y a veces había que moverlo un poco para que volviese a funcionar, ya que usaba una punta de contacto que a veces se podía mover. No obstante, pronto se desarrollarían transistores más robustos tal como los conocemos actualmente.

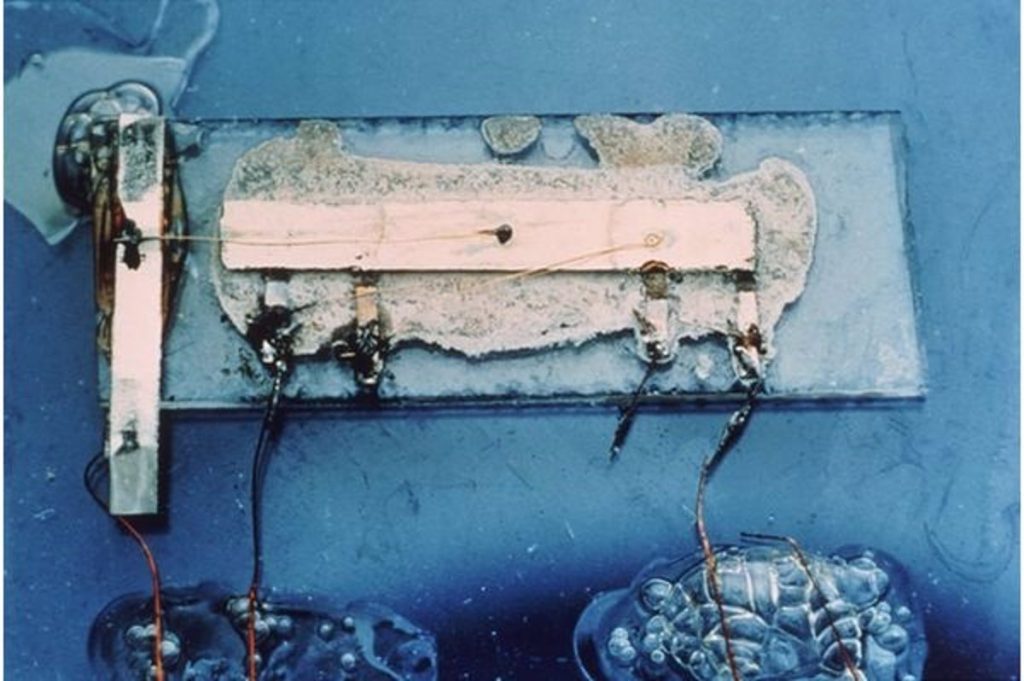

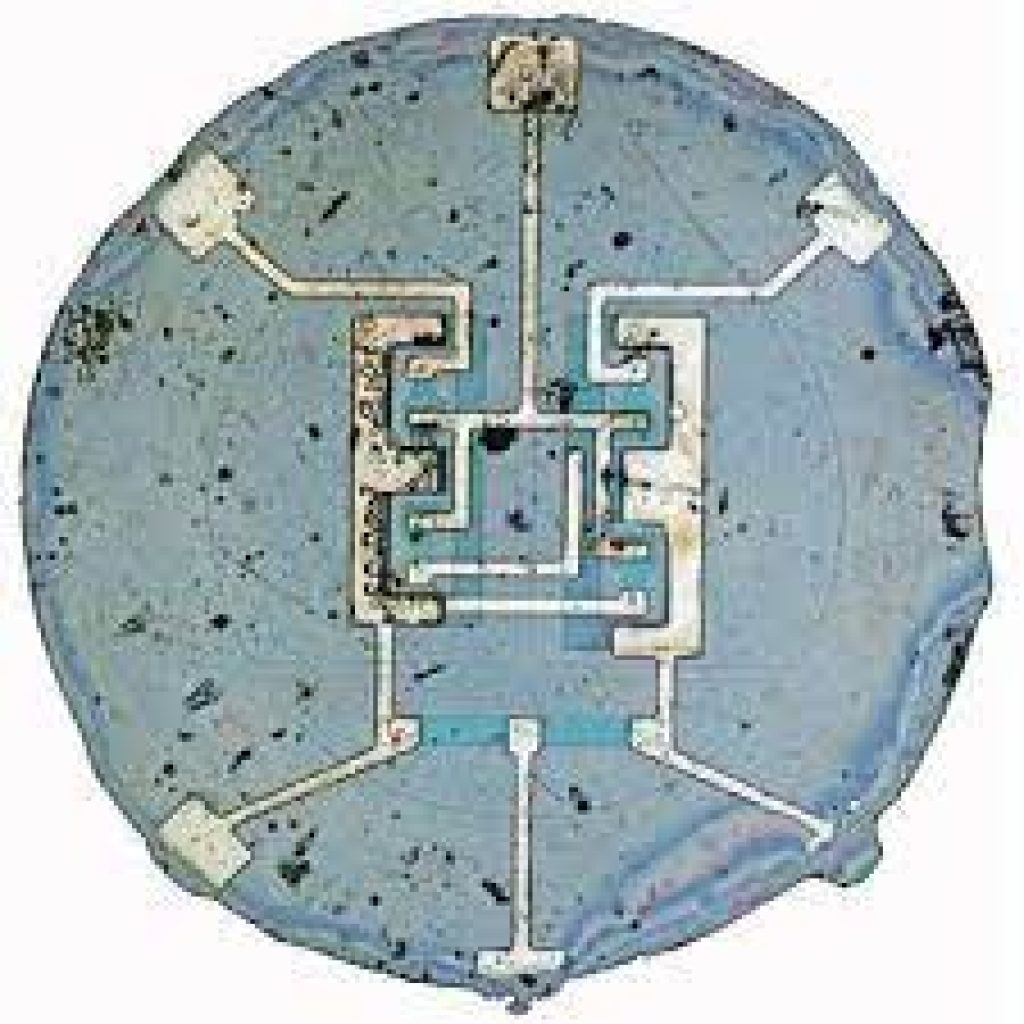

Más tarde, Jack Kilby y Robert Noyce, de Texas Instruments y Fairchild Semiconductor respectivamente, idearon la forma de integrar varios de estos transistores en una sola pastilla monolítica de semiconductor. Es decir, inventaron el chip tal como lo conocemos hoy en día. Sin embargo, la tecnología de TI era algo más tosca, tipo MESA, y finalmente triunfaría la de Fairchild tipo PLANAR, que es la que se ha usado hasta nuestros días.

Tras la mejora del transistor y la invención del chip, poco a poco se ha buscado siempre la forma de mejorar las prestaciones de estos dispositivos semiconductores. Desde usar nuevos materiales, alterar las estructuras, hasta miniaturizarlos cada vez más. Incluso se llegó a usar algunas técnicas de ingeniería avanzada como strained silicon, donde se estiraba o se comprimía la estructura cristalina del silicio para generar menor o mayor resistencia eléctrica según convenía.

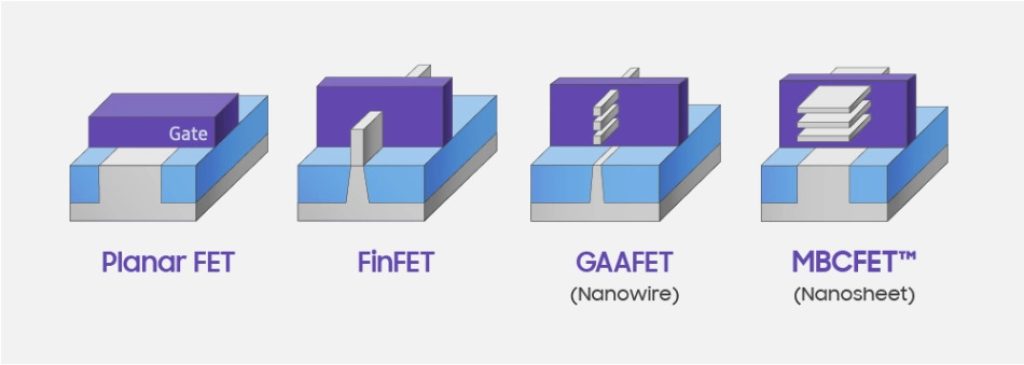

Se han vivido grandes cambios en la industria de los semiconductores que han supuesto grandes avances, como la introducción del cobre para las interconexiones metálicas para sustituir al aluminio, la introducción de los materiales dieléctricos High-K, pasando últimamente por el cambio de los CMOS MOSFET planar por estructuras tridimensionales como los FinFET.

Hay que tener en cuenta que las puertas de los transistores tenían una capa de dióxido de silicio muy fina como capa aislante para separarla del canal del transistor. Sin embargo, a partir de los 45nm, esta capa se volvió insuficiente, por lo que se introdujo el dieléctrico High-K basado en hafnio.

Por otro lado, a partir de los 28nm llegaría otro gran problema, y es que se comenzaron a acrecentar los efectos de canal corto. Y es que, mientras el transistor seguía reduciendose de tamaño, el canal se iba estrechando cada vez más, y esto reducía la capacidad para controlar el flujo de corriente del canal, produciendo corrientes de fuga excesivas. Es por eso que se comenzó a usar los FinFET o transistores 3D.

Gracias a estos transistores FinFET se pudo seguir reduciendo el tamaño de los transistores sin esos problemas de canal corto. Y esto era debido a que el canal estaba rodeado por la puerta en tres de sus lados, en vez de solo uno como en la tecnología planar. Esto permitía un mejor control de la corriente que fluía y reducir los problemas de fugas. Además, se conseguían tiempos de conmutación más rápidos, lo que permitía aumentar la frecuencia de reloj.

Pero la industria de los semiconductores ya apunta hacia otro gran avance para salvar los problemas de delgadez y altura de los «fins» o aletas de los FinFET, y esto llega con la nueva generación de transistores no planar, los llamados SGT o también conocidos como GAAFET (Gate-All-Around). Estos nuevos transistores de efecto de campo usan nanosheets o nanohojas colocadas en forma horizontal y apiladas, lo que permite que la puerta del canal esté alrededor de 4 lados y no de tres como en los FinFET.

Esto incrementa el control de la corriente y el rendimiento de estos transistores que se están comenzando a usa. Por otro lado, la anchura de cada nanosheet y el número de cada nanosheets en cada transistor puede variar, permitiendo diseños personalizados.

En 2022 Samsung fue la primera en anunciar el uso de GAA en su proceso de 3nm. Sin embargo, debido a problemas con el yield para fabricar alto volumen de chips, GAA fue retrasado hasta 2024. TSMC tiene previsto comenzar a usar GAA en su nodo de 2 nm para 2025 o 2026, mientras que Intel hará algo parecido con su nodo de 20A.

En cambio, tras los GAA la industria de los semiconductores no se quedará quieta, y eso es precisamente lo que te vamos a contar aquí, ¿qué viene después de los GAA?

El futuro de los semiconductores

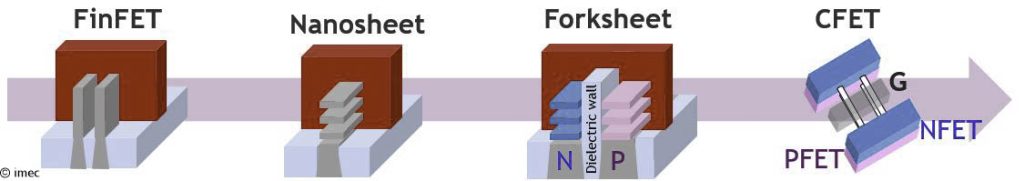

Después de los GAA, los transistores comenzarán a cambiar para mejorar aún más, y lo harán en corma de forksheet o también conocido como CFET (3D Complementary FET). En este tipo de transistores que llegarán en unos años, el canal n y p serán movidos juntos, muy cerca, y apilados verticalmente.

La estructura de los CFET demostró una mejora de rendimiento del 8% frente a las tecnologías actuales, además de una reducción del área en un 44%, lo que supone una mayor densidad de integración. Sin embargo, quedan retos que superar en lo que respecta a la fabricación.

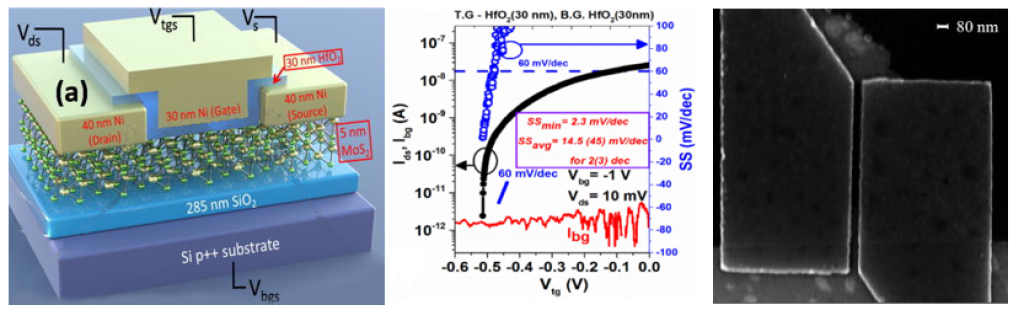

Pero no será la única innovación que tendremos, ya que vendrán de la mano de otras, como los materiales 2D, es decir, capas de un átomo de espesor de sólidos cristalinos. Uno de los materiales más conocidos en este caso es el grafeno, que consiste en una capa de carbono de un solo átomo de espesor y estructurados en celdas cristalinas hexagonales. Pero no será el grafeno el único material empleado de este tipo.

Uno de los materiales 2D más prometedores para la nueva generación de nanosheets será el TMD (Transition Metal Dichalcogenide). Esta familia de materiales incluyen el disulfuro de molibdeno (MoS), disulfuro de tungsteno (WS), diseleniuro de tungsteno (WSe), etc. Estos materiales serán claves para los futuros procesos de fabricación de chips.

En el pasado también se apuntó hacia los CNTs o nanotubos de carbono, un material unidimensional también muy prometedor, pero ha tenido graves dificultades para su manufactura, pese a que se lleva más de 30 años investigando en ello. Y es que se deben hacer crecer millones de nanotubos individuales y que estén alienados de la misma manera, algo que no es fácil. Por eso los materiales 2D son muchos más versátiles y fáciles de fabricar.

Para poder crecer los materiales 2D, se pueden emplear técnicas que ya se usan en la industria de los semiconductores, como CVD, ALD, etc. Es decir, deposición de vapor químico, deposición de capa atómica, etc. Sin embargo, no deja de tener sus retos, por eso en la actualidad no se está usando para su producción en masa, aunque hay muchas empresas con los ojos puestos en estos materiales, como es el caso de las europeas Graphenea y Applied Nanolayers, que están construyendo foundries de grafeno.

Además de los métodos de deposición o crecimiento, los materiales 2D que se depositan sobre sustratos de cobre o zafiro, entre otros, necesitan de un paso de transferencia adicional para poder trasladar el material a la oblea de silicio final. Sin embargo, los métodos actuales que existen para este traslado son insuficientes para el mercado CMOS. Por ejemplo, la técnica de transferencia más convencional es el grabado húmedo en el sustrato de cobre usando PMMA (PoliMetacrilato de Metilo), pero los residuos de PMMA pueden degradar las propiedades eléctricas del grafeno.

Estos métodos pueden ser suficientes para aplicaciones menos exigentes, como pantallas, sensores, etc., pero no para chips de alto rendimiento… pero llegarán en unos años.

¡La industria del chip está más viva que nunca! Y al Si aún le queda un largo recorrido…