- MI450X IF128 enlaza 128 GPU con HBM4 y Ethernet acelerado, priorizando densidad y ancho de banda.

- Frente a Rubin NVL144, AMD apunta a mayor memoria y FLOPS agregados por bastidor.

- La clave será el software: ROCm y HIP deben acercarse a la experiencia CUDA.

- IF64 podría adelantarse por rampa de producción, con despliegues reales a partir de 2026.

El acelerador AMD Instinct MI450X se ha colocado en el centro del debate sobre la nueva generación de infraestructuras de inteligencia artificial, y no es para menos: su planteamiento de escala de bastidor promete un salto grande en densidad y conectividad. En este análisis desgranamos cada pieza del rompecabezas: desde la arquitectura IF128 e IF64, pasando por HBM4 y Ethernet acelerado, hasta la comparación con Vera Rubin de NVIDIA y los retos de software que AMD debe resolver para convertir la potencia bruta en resultados reales.

Más allá de los titulares, lo interesante es que AMD prepara su primer clúster de GPU realmente concebido a escala de rack, con decisiones de diseño que persiguen ancho de banda masivo, baja latencia y despliegues más sencillos en centros de datos. Todo ello llega acompañado de señales claras desde la cúpula de la compañía: su objetivo es que MI450 sea su particular momento Milan, ese punto de inflexión en el que el mercado deja de dudar y adopta su pila tecnológica con confianza.

Qué es MI450X IF128 y por qué su enfoque de rack importa

AMD ha dividido su familia Instinct MI400 en dos líneas con objetivos distintos: MI430X, orientada a HPC de precisión, y MI450X, enfocada a IA a gran escala. Dentro de esta última aparece el despliegue estrella, MI450X IF128, una arquitectura de bastidor que enlaza 128 GPU mediante Infinity Fabric sobre Ethernet. En paralelo, la compañía planea una placa base IF64, pensada para instalaciones más sencillas en un solo rack con aproximadamente la mitad de recursos.

En la configuración IF128, cada acelerador MI450X se espera fabricado en nodo de clase 3 nm de TSMC y empaquetado con CoWoS-L. La memoria integrada es HBM4, con al menos 288 GB por GPU y hasta 18 TB/s de ancho de banda, una cifra que encaja con los objetivos de entrenamiento de modelos gigantescos. El cómputo declarado ronda 50 PetaFLOPS en FP4 por GPU, ubicando al sistema en la primera línea de la carrera por escalar tokens y parámetros sin estrangulamientos de memoria.

El plano de comunicación interno no se queda corto: AMD habla de aproximadamente 1,8 TB/s de ancho de banda unidireccional por GPU dentro del rack. Sumado entre los 128 aceleradores, el tejido del bastidor alcanzaría unos 2.304 TB/s agregados. Sobre el papel, esta cifra responde a los cuellos de botella clásicos que aparecen cuando se diseminan miles de GPUs y se pretende mantener eficiencia alta en entrenamiento distribuido.

Si agregamos capacidades, el conjunto MI450X IF128 se movería en torno a 6.400 PetaFLOPS FP4 y unos 36,9 TB de memoria HBM de gran ancho de banda dentro del bastidor. Para la modalidad IF64, los valores serían aproximadamente la mitad, algo útil para centros que deseen empezar en un solo rack sin renunciar al camino de crecimiento que propone la misma pila tecnológica.

Otro dato relevante es la envolvente térmica: las fuentes sitúan el consumo por acelerador entre 1,6 y 2,0 kW. Este parámetro no es menor, porque condiciona densidad por rack, requisitos de energía y refrigeración, y en última instancia el coste total de propiedad del despliegue.

Existe además una discusión interesante sobre empaquetado: algunas fuentes apuntan a que el recuento anunciado para NVIDIA en su sistema NVL144 combina 72 paquetes con 2 GPU por paquete, de donde salen las 144 unidades lógicas finales. En el caso de AMD, se ha hablado de 128 paquetes, y si finalmente cada paquete incorporase 2 GPU, el clúster se iría a 256 GPU por rack. Ese salto implicaría una ventaja potencial del 77% en ampliación de densidad frente a NVL144, con todo lo que ello implica en rendimiento y consumo total.

Interconexión: Infinity Fabric sobre Ethernet, UALink y NIC Pensando

El punto diferencial del MI450X para IA está en el tejido de comunicaciones. En lugar de apoyarse en un bus tradicional, AMD usa Infinity Fabric sobre Ethernet y conecta cada GPU a tres NIC de 800 GbE de la familia Pensando. El objetivo es claro: habilitar escalado horizontal con tecnología estandarizada y aceleración por hardware, aprovechando la madurez del ecosistema Ethernet en centros de datos.

En esta generación, UALink aparece como la pieza para la conexión de GPU a GPU sin depender de PCIe, pero la realidad industrial manda: los conmutadores UALink de proveedores como Broadcom o Astera Labs no estarán listos desde el día uno. Por eso, AMD ha diseñado opciones de topología que no dependan de esos conmutadores, manteniendo rendimiento alto con la malla y la red basada en Ethernet acelerado.

Este contexto explica también la segmentación de producto: MI430X UL4, orientado a HPC de doble precisión, utiliza una malla punto a punto con cuatro GPU para minimizar latencias en clústeres compactos, precisamente porque los switches UALink aún tardarán. La otra vía, MI450X para IA masiva, centra su apuesta en Ultra Ethernet y el soporte de conmutadores UEC ya presentes, lo que allana el despliegue de granjas con cientos de nodos sin esperar a que madure el silicio específico de UALink.

En la práctica, esta estrategia reduce riesgos de calendario y ofrece una ruta de adopción inmediata: si ya tienes tejido Ethernet de alto rendimiento, puedes integrar el bastidor IF64 o IF128 con menos fricción, coordinando entrenamiento a gran escala con las herramientas que los equipos de NetOps y SRE dominan desde hace años.

Conviene subrayar que la apuesta por Ethernet no es sinónimo de cuellos de botella: la cifra de 1,8 TB/s unidireccionales por GPU y el uso de tres enlaces de 800 GbE por acelerador dibujan una canalización muy generosa para el tráfico de activaciones, gradientes y all-reduce en cargas modernas.

La comparación con NVIDIA: Vera Rubin VR200 y el salto a VR300

Para medir el alcance del IF128, hay que mirarlo frente a la competencia directa de NVIDIA. Las estimaciones público-técnicas sitúan a Vera Rubin VR200 NVL144 en torno a 3.600 PetaFLOPS de cómputo FP4 por bastidor y unos 936 TB/s de ancho de banda de memoria agregada. Frente a ello, el enfoque IF128 de AMD apunta a aproximadamente el doble de ancho de banda de memoria a escala de rack y una cifra de cómputo superior.

Otro aspecto a tener en cuenta es el ritmo de revisiones. Fuentes con acceso a hojas técnicas aseguran que tanto AMD como NVIDIA han incrementado TGP y ancho de banda de memoria respecto a los primeros planes, ajustándose sobre la marcha a la presión competitiva. En el lado de AMD, se habla de un aumento de unos 200 W en TGP sobre cifras iniciales; en el de NVIDIA, el salto se habría ido hasta unos 2.300 W por acelerador. En memoria, Rubin habría pasado de ~13 TB/s a hasta 20 TB/s por GPU en sus iteraciones más ambiciosas.

La clave, con todo, es el calendario. Mientras AMD perfila su primer bastidor IF128 para la segunda mitad de 2026, NVIDIA ya estaría acumulando adopciones tempranas de Rubin en grandes actores del sector, con menciones de clientes del tamaño de OpenAI. Es decir, la carrera está en marcha y el ganador parcial de cada tramo dependerá de fechas y disponibilidad tanto como de métricas puras.

En el horizonte aparece también la evolución de NVIDIA hacia VR300 Ultra NVL576, un sistema que elevaría el recuento a 144 GPU, cada una con cuatro chiplets de cómputo, sumando 576 die de cálculo por bastidor. Si AMD llega primero con IF128 y mantiene ventaja tangible en ancho de banda, tendrá una ventana de oportunidad antes de ese salto generacional de su rival.

Por si fuera poco, la aritmética del empaquetado añade matices: si AMD termina usando 2 GPU por paquete en sus 128 paquetes, el total de GPU por rack sería significativamente mayor que los 72 paquetes con 2 GPU del NVL144 de Rubin. Ese diferencial se traduciría en más capacidad de entrenamiento por unidad de espacio físico, un argumento contundente en centros con limitaciones de potencia y refrigeración por bastidor.

Hardware sin buen software no gana: CUDA frente a ROCm y el papel de HIP

Si hay un obstáculo histórico para AMD en IA, ese es el software. La supremacía de CUDA y su ecosistema con millones de desarrolladores, herramientas, bibliotecas y tutoriales hace que el mejor hardware no baste por sí solo. Muchos laboratorios primero piensan en compatibilidad de frameworks, estabilidad de drivers y madurez de kernels antes de mirar las especificaciones del acelerador.

En este punto, hay señales prometedoras. Contactos directos con la dirección de AMD han dejado claro que la compañía es consciente de los puntos flacos de ROCm y la necesidad de mejorar HIP para facilitar el salto desde CUDA. Incluso se ha hablado de sesiones técnicas con equipos externos reportando bugs, cuellos de botella y recomendaciones de roadmap, con involucración personal de la cúpula para priorizar correcciones.

La cuestión de fondo es si AMD podrá ofrecer, a tiempo, un entorno donde la paridad funcional sea suficiente y la migración desde CUDA no suponga meses de ingeniería extra. La historia reciente con drivers de gaming demuestra que, con foco y constancia, AMD es capaz de remontar. En IA, el reloj corre y el listón lo marcan librerías muy optimizadas en la plataforma rival.

Este debate no es exclusivo de AMD. El caso de Huawei con su CloudMatrix 384 revela lo costoso que es no tener un entorno de software redondo: pese a combinar 384 chips Ascend 910C en 16 racks, con alrededor de 300 PetaFLOPS BF16 y 560 kW de consumo, las limitaciones de software y de cadena de suministro (ópticas restringidas a exportación) complican la adopción. Es una lección clara para cualquiera que quiera escalar IA a ritmos de hiperescala.

Por eso el MI450X IF128 será también una prueba clave de si un tejido basado en Ethernet puede cumplir con las exigencias de entrenamiento en el mundo real. No bastará con números de laboratorio; la métrica relevante será la eficiencia final por nodo, por rack y a nivel de clúster, con las pilas de software que ya usan los clientes.

La trayectoria de AMD: de MI325X y MI355X a la ambición de MI450

Para entender dónde encaja MI450, conviene recordar los pasos previos. MI325X compitió con H200 en una franja donde AMD recortó distancia en valor, aunque no marcó un golpe definitivo. Más tarde, MI355X se acercó a Blackwell Ultra en términos de rendimiento por euro, si bien no logró igualar la potencia bruta en el tope de gama de su rival.

Con MI450, AMD eleva la apuesta: el mensaje desde su división de centros de datos es que alcanzarán rendimiento líder en entrenamiento e inferencia. La compañía lo compara con su momento Milan en CPU, una etapa en la que EPYC dio el vuelco y superó la barrera del 10% de cuota, consolidando después su avance hasta cifras muy relevantes de ingresos en servidores.

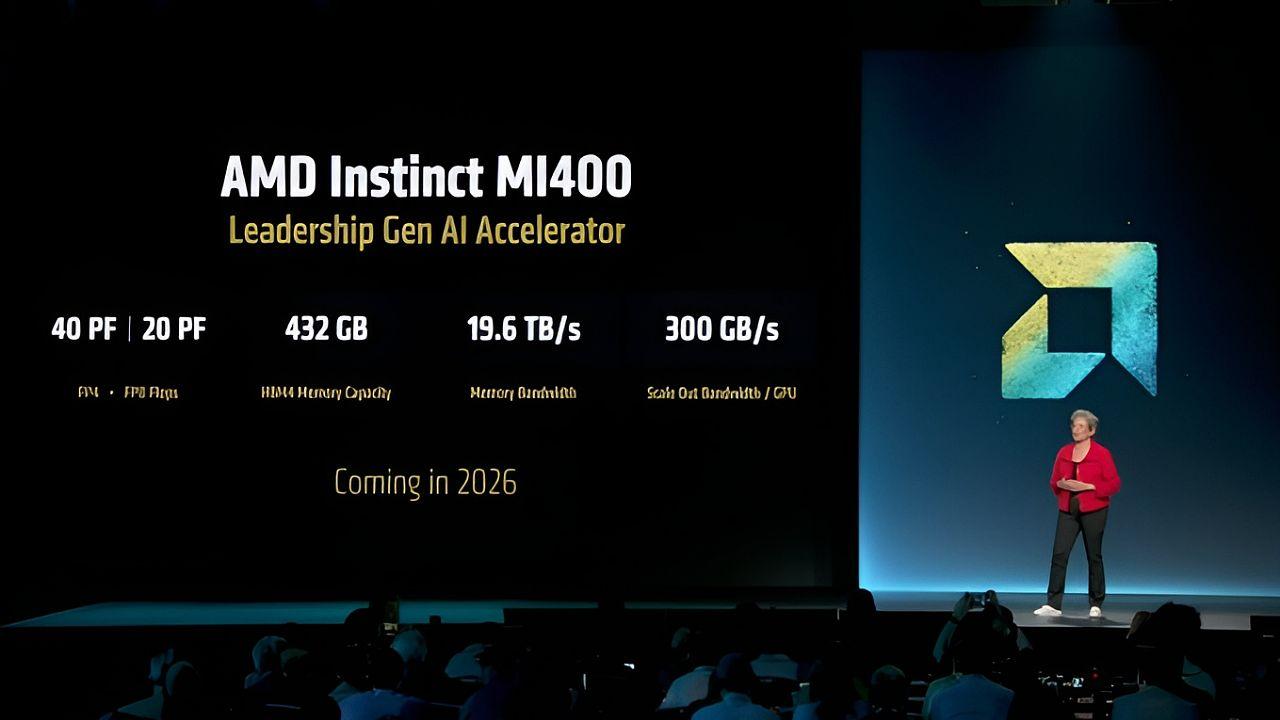

El plan técnico acompaña al discurso. En la familia MI400/MI450 se habla de HBM4 con capacidades de hasta 432 GB en algunas configuraciones, un ancho de banda muy superior al de generaciones anteriores, y una arquitectura de rack (conocida internamente como Helios en algunas hojas) que busca escalar de forma ordenada desde un bastidor hasta granjas con cientos de nodos.

Esta hoja de ruta separa claramente el foco: MI430X UL4 para FP64 y aplicaciones HPC con topologías compactas de baja latencia, y MI450X para IA a gran escala con Ethernet de alto rendimiento y enlace a NIC de 800 GbE. Esta segmentación permite a AMD atacar dos necesidades distintas con soluciones optimizadas sin esperar a que maduren todos los elementos de UALink.

En paralelo, la compañía refuerza el mensaje de software: quieren que ROCm llegue preparado al lanzamiento y que los clientes no perciban desventaja al elegir su plataforma. Si la paridad de software acompaña al salto de hardware, el efecto sobre la adopción podría parecerse al punto de inflexión que vivieron con EPYC en su día.

Especificaciones y cifras clave del sistema MI450X IF128

Para quienes prefieren ver lo esencial de un vistazo, estas son las magnitudes más relevantes que se han adelantado para el bastidor IF128:

- 128 GPU por rack conectadas mediante Infinity Fabric sobre Ethernet; opción IF64 con ~la mitad.

- HBM4 por GPU: al menos 288 GB y hasta 18 TB/s; en la familia MI400 se contemplan configuraciones de hasta 432 GB.

- Rendimiento por GPU: en torno a 50 PetaFLOPS FP4; total del rack cerca de 6.400 PetaFLOPS.

- Ancho de banda interno: aproximadamente 1,8 TB/s unidireccional por GPU y 2.304 TB/s agregados por rack.

- Red: tres NIC Pensando 800 GbE integradas por GPU; escalado horizontal con Ultra Ethernet.

- Consumo: objetivo de 1,6 a 2,0 kW por acelerador, condicionado por revisiones de TGP.

Estas cifras colocan a MI450X IF128 como una plataforma de densidad agresiva, concebida para entrenar modelos frontera y servir inferencia a gran escala sin re-cableados exóticos.

Riesgos de producción, tiempos y estrategia de despliegue

Una arquitectura tan ambiciosa no llega sin retos. Se ha señalado que la rampa de producción podría ser compleja, tanto por la integración de HBM4 y CoWoS-L como por la disponibilidad de componentes de red avanzados. Conscientes de ello, en AMD barajan salir antes con IF64, el bastidor más simple, mientras completan la industrialización de IF128.

El calendario que se maneja sitúa el primer clúster de GPU a escala de rack de AMD en la segunda mitad de 2026. De cumplirse, supondría la entrada formal de la compañía en el juego de sistemas llave en mano comparables a los de NVIDIA, y permitiría a los clientes cualificar la plataforma con cargas reales en paralelo a la mejora del software.

De cara a los operadores, eso significa que 2026 y 2027 serán años de pruebas comparativas intensas entre bastidores de AMD, Rubin y posteriores iteraciones. El coste total de propiedad (energía, refrigeración, ocupación, eficiencia de software) será tan determinante como la cifra bruta de FLOPS o de ancho de banda, especialmente para hyperscalers.

Un punto que no se debe pasar por alto es la evolución de la memoria: HBM4 y sus capacidades marcarán cuánta secuencia de tokens por segundo se podrá sostener en entrenamiento e inferencia. Si AMD consolida 288 GB por GPU y habilita variantes con mayor capacidad cuando madure el packaging, ganará flexibilidad para modelos que exigen contextos enormes.

En definitiva, la combinación de red Ethernet acelerada, HBM4 de alta capacidad y un diseño afinado a bastidor define una propuesta atractiva… siempre que ROCm y el ecosistema acompañen sin fisuras.

La fotografía completa de MI450X IF128 revela una estrategia coherente: AMD quiere competir no solo con números, sino con una arquitectura pensada para escalar racks enteros usando tecnologías ampliamente aceptadas en centros de datos. Frente a Rubin, su apuesta se apoya en más ancho de banda de memoria agregado y en densidad potencial por bastidor si el empaquetado a dos GPU por paquete se confirma. Sin embargo, será el software quien incline la balanza: si ROCm y HIP cierran la brecha con CUDA con la suficiente rapidez, la propuesta de AMD tiene mimbres para seducir a operadores que buscan diversificar y evitar dependencias, sin renunciar a la eficiencia ni a la velocidad de puesta en marcha.