- IBM demuestra corrección de errores cuánticos en tiempo real sobre FPGA de AMD, con rendimiento 10x por encima de lo exigido.

- El enfoque híbrido combina cúbits con CPU, GPU y FPGA, apoyado en ecosistemas abiertos como Qiskit e infra HPC de AMD.

- qLDPC reduce drásticamente la sobrecarga de cúbits físicos, acercando el objetivo de sistemas tolerantes a fallos para 2029.

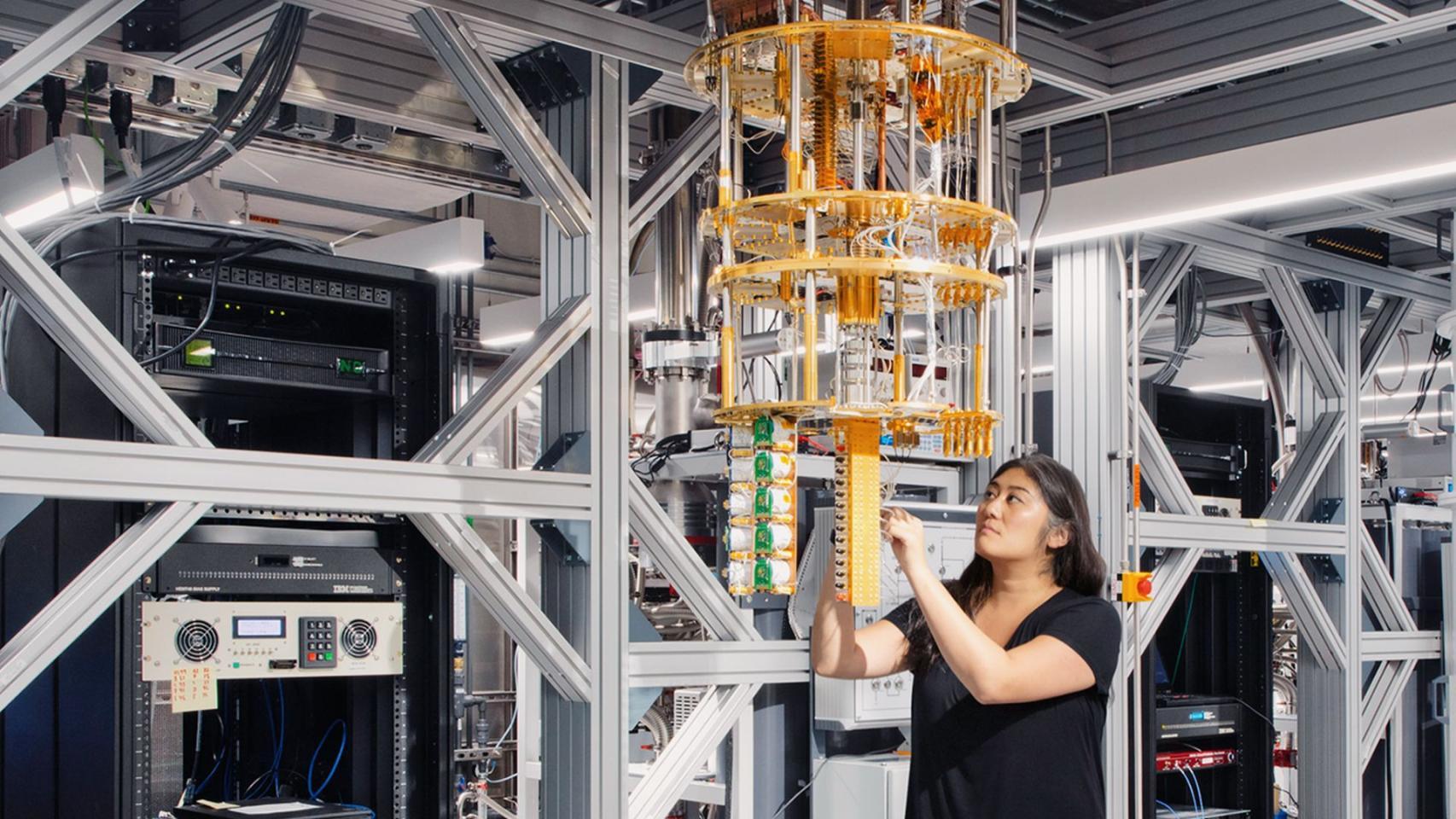

El salto que muchas tecnológicas perseguían desde hace años empieza a tomar forma: IBM ha logrado ejecutar en tiempo real un algoritmo clave de corrección de errores cuánticos sobre hardware clásico. No es un detalle menor ni un experimento de laboratorio aislado; hablamos de correr esa lógica en chips FPGA comerciales de AMD, una pieza que hasta ahora funcionaba como puente acelerador en centros de datos y que, de repente, pisa el terreno cuántico con propósito.

Mientras la inteligencia artificial ocupa titulares, la computación cuántica marca su propio ritmo. Google anunció recientemente un avance en algoritmos cuánticos y, en paralelo, IBM da un paso que ataca el gran talón de Aquiles del sector: los errores debidos al ruido. La noticia, citada por Reuters y ampliada por diversos medios, no solo cuenta que “se puede”; añade que la ejecución es diez veces más rápida de lo que haría falta, y que se ha logrado en FPGAs de AMD disponibles en el mercado y nada “ridículamente” caros.

Qué ha anunciado exactamente IBM

La compañía asegura haber demostrado que sus algoritmos de corrección de errores cuánticos funcionan en tiempo real sobre FPGA (field-programmable gate array) de AMD. Esto significa que la parte “clásica” puede apoyar y estabilizar a los cúbits en plena ejecución, reduciendo el impacto del ruido sin necesidad de hardware exótico adicional en esa capa de soporte.

Según el director de investigación de IBM, Jay Gambetta, el equipo ha sido capaz de implementar el algoritmo en estos chips con un margen de rendimiento de 10x respecto a lo necesario. Este detalle es crucial: la corrección de errores en vivo exige latencias muy bajas, y los FPGA sobresalen justamente en eso, con pipelines deterministas y una reconfigurabilidad que encaja como un guante en escenarios de control y feedback cuántico.

El experimento no se ha quedado en simulaciones: los algoritmos se han ejecutado en condiciones “de mundo real”. Ese matiz despeja dudas sobre implementaciones teóricas que, cuando aterrizan en hardware, se rompen por latencias, cuellos de botella o costes. Aquí, además, la elección de AMD añade otro mensaje: hay ecosistema y disponibilidad.

IBM enmarca este avance dentro de una hoja de ruta ambiciosa que busca ordenadores cuánticos tolerantes a fallos a gran escala antes de que termine la década. En concreto, la compañía ha hablado del proyecto Starling y de arquitecturas capaces de sostener del orden de 100 millones de operaciones cuánticas soportadas por unos 200 cúbits lógicos.

Por qué la corrección de errores es el punto crítico

Para entender el calado del anuncio hay que volver a lo básico: los cúbits no se comportan como los bits. Pueden estar en superposición y entrelazarse, abriendo caminos a atajos matemáticos imposibles en la informática clásica. Pero pagan un precio: son extremadamente sensibles a perturbaciones externas como el calor, vibraciones o incluso rayos cósmicos, lo que introduce errores que pueden echar por tierra cualquier cálculo.

La industria trabaja desde hace tiempo con dos frentes. Por un lado, mejorar el hardware cuántico para reducir el ruido. Por otro, diseñar esquemas de corrección que “vigilan” y estabilizan la información cuántica mientras se ejecutan las operaciones. Esta segunda vía implica medir y actuar en tiempo real, algo que únicamente es viable si la capa clásica responde a gran velocidad y con latencias predecibles.

De ahí que los cúbits lógicos sean tan relevantes: encapsulan la información de un cúbit ideal en un conjunto de varios cúbits físicos, de modo que se detectan y corrigen fallos entre ellos. El coste de esta estrategia, sin embargo, suele ser alto: hace falta una gran sobrecarga de cúbits físicos por cada cúbit lógico útil.

En ese contexto, IBM ha puesto el foco en los códigos qLDPC (quantum Low-Density Parity-Check). Estos códigos prometen reducir hasta en torno a un 90% el número de cúbits físicos necesarios por cada cúbit lógico frente a métodos anteriores, lo que recorta varios órdenes de magnitud los recursos para desplegar computación cuántica tolerante a fallos.

La combinación de qLDPC con la ejecución de corrección en tiempo real sobre FPGA de AMD envía un mensaje doble: hay un camino tecnológico plausible y, además, se puede articular con componentes clásicos accesibles. En otras palabras, no hace falta reinventar todo el stack; se puede hibridar.

El papel de los FPGA de AMD y por qué encajan

Los FPGA son circuitos integrados reprogramables tras su fabricación, capaces de adaptarse a tareas específicas con paralelismo masivo. Su valor diferencial, frente a CPU o GPU, está en la latencia extremadamente baja y la predictibilidad temporal, claves para controlar y corregir en bucle procesos delicados como los cuánticos.

AMD, además de CPUs y GPUs de alto rendimiento, cuenta con un porfolio sólido de FPGA para centros de datos y aplicaciones embebidas. IBM subraya que el algoritmo funciona en dispositivos disponibles y relativamente asequibles, alejando el fantasma de soluciones “de escaparate” impracticables por coste o por logística.

La implementación descrita por IBM demuestra que la orquestación entre el chip cuántico y el FPGA puede sostenerse a una velocidad diez veces superior a la mínima requerida. Ese margen no es un lujo: es lo que convierte un prototipo en algo desplegable, porque absorbe ineficiencias inevitables cuando se escala a sistemas reales y se conectan más piezas.

Otro punto a favor de esta arquitectura es su flexibilidad: los FPGA permiten ajustar el diseño lógico según evolucionen los códigos de corrección, sin esperar a nuevas generaciones de silicio. En un campo con avances rápidos, ese dinamismo acorta ciclos de experimentación y reduce el riesgo de quedar “atrapado” por el hardware.

Una alianza clara: IBM y AMD apuestan por el híbrido

En agosto, ambas compañías hicieron público un acuerdo para desarrollar capacidades conjuntas de computación cuántica e integrar tecnologías. No es un pacto simbólico: materializa la visión de “cada cosa en su sitio”, donde la parte cuántica se encarga de lo que mejor sabe (simulaciones a nivel atómico, optimizaciones combinatorias gigantes), y la parte clásica lleva el peso del procesamiento masivo, el movimiento de datos, el entrenamiento de modelos y el postprocesado.

IBM aporta su músculo cuántico con un ecosistema ya reconocible: Qiskit como marco de programación y IBM Quantum System Two como arquitectura modular. La empresa presume de integraciones con supercomputadores como Fugaku (RIKEN, Japón) y de colaboraciones con entidades como Cleveland Clinic, el Gobierno Vasco o Lockheed Martin, donde se buscan casos de uso con impacto medible.

AMD pone sobre la mesa el otro medio campo: CPU EPYC, GPU Instinct y sus FPGA, la misma columna vertebral que impulsa sistemas exaescala como Frontier (Oak Ridge) y El Capitan (Lawrence Livermore), ambos en lo más alto del TOP500. Además, su pila de software abierta es ya habitual en los grandes proveedores de nube y en despliegues de IA generativa.

El plan a corto plazo pasa por enseñar un primer flujo end-to-end donde un ordenador cuántico de IBM se coordina con CPU, GPU y FPGA de AMD para ejecutar un pipeline híbrido completo. No es solo invocar un kernel cuántico: se trata de orquestar colas, sincronizar latencias entre mundos muy distintos y, sobre todo, sostener la corrección de errores en tiempo real.

Que esta colaboración insista en plataformas abiertas no es casualidad. Si los algoritmos híbridos quedan dentro de un SDK propietario, la adopción se frena. Con Qiskit y stacks abiertos, investigadores y empresas pueden moverse sin tirar su trabajo cada vez que cambie el hardware, lo que reduce fricción y acelera la llegada a producción.

Contexto competitivo: Google, Microsoft y el pulso del mercado

El movimiento de IBM llega justo cuando Google ha comunicado un avance relevante en algoritmos cuánticos, reavivando la carrera entre gigantes. Microsoft tampoco se queda al margen, empujando su visión de integración cuántica con la nube y herramientas de desarrollo orientadas al usuario empresarial.

Más allá de lo técnico, el mercado reaccionó con fuerza. Algunas crónicas hablan de subidas intradía del 9% para IBM hasta los 310,75 dólares a media sesión, mientras que el cierre citado por Reuters recogió un avance cercano al 7,9% hasta rondar los 397,46 dólares. AMD también celebró la noticia, con alzas de aproximadamente el 7,6% hasta los 252,92 dólares; variaciones que cuadran con una jornada de fuerte optimismo inversor.

En el acumulado anual más reciente, y según distintas fuentes del sector, AMD habría rebotado en torno al 94% e IBM en torno al 30%. El mensaje que se desliza es que la computación de alto rendimiento, ya sea para IA o para cuántica, empuja las valoraciones; y que la cooperación entre ambos jugadores abre oportunidades comerciales reales.

También hay lectura estratégica: AMD se acerca al terreno de Nvidia en el cómputo acelerado, consolidándose como proveedor clave para nubes públicas y actores de IA como OpenAI, Microsoft o Google. Este cruce con la agenda cuántica de IBM refuerza la idea de que el futuro será mixto y que, en esa mezcla, la latencia y la integración cuentan tanto como la potencia bruta.

Objetivo 2029: hacia máquinas tolerantes a fallos

IBM sitúa el listón alto con su plan Starling: un ordenador cuántico tolerante a fallos y a gran escala para 2029. En esa visión aparecen números concretos, como la ejecución de cerca de 100 millones de operaciones cuánticas con unos 200 cúbits lógicos. No se trata solo de más cúbits, sino de cúbits “mejores”, sostenidos por capas de corrección robustas.

El avance presentado ahora se habría completado un año antes de lo previsto, lo que sugiere que la curva de aprendizaje se está acelerando. Aquí, de nuevo, la opción de descargar parte de la complejidad en FPGA de propósito general ayuda a comprimir tiempos: se prototipa, se itera, se ajusta, y se valida sin depender de ciclos largos de fabricación.

Si esa hoja de ruta se cumple, la frontera de lo posible en simulación, optimización y diseño de materiales se moverá varios escalones. Muchas cargas que hoy están fuera de alcance incluso para superordenadores clásicos podrían entrar en plazo con estrategias híbridas bien orquestadas.

Para qué sirve todo esto: casos de uso con pies en el suelo

En descubrimiento de fármacos, por ejemplo, la parte cuántica puede encargarse de la simulación fina de interacciones moleculares, mientras la parte clásica filtra bibliotecas gigantes, entrena modelos y valida resultados a gran velocidad. Ese reparto adelgaza el tiempo total de ciclo y reduce costes.

En materiales, los cúbits explorarían configuraciones electrónicas que hoy resultan prohibitivas; la supercomputación clásica confirmaría y escalaría los mejores candidatos, conectando laboratorio y planta de producción. Lo mismo ocurre en energía, donde optimizaciones complejas de redes podrían beneficiarse de heurísticas cuánticas apoyadas por control clásico en tiempo real.

La logística y las finanzas no se quedan fuera. Problemas de enrutado, asignación y cobertura que combinan miles de restricciones pueden plantearse con formulaciones que aprovechen el entrelazamiento y la superposición, dejando al back-end clásico la ingestión y actualización de datos del mundo real sin cuellos de botella.

Y, por supuesto, en ciberseguridad y criptografía poscuántica, la validación masiva y el testeo sistemático de nuevos esquemas se aceleran al tener un banco de pruebas híbrido, donde los cuellos de latencia están domados por FPGA que encajan con los ritmos del hardware cuántico.

Los retos que no se pueden barrer bajo la alfombra

No todo son fuegos artificiales. Los códigos de corrección siguen siendo costosos en recursos; orquestar un flujo híbrido introduce latencias y complejidades de sincronización; y los centros de datos no están diseñados (todavía) para convivir con criogenia a gran escala y requisitos electromagnéticos tan estrictos.

También hay una cuestión de costes. La parte clásica ya es exigente en consumo y CAPEX; añadir el componente cuántico sin un retorno claro sería un lujo. Aquí es donde la estrategia de IBM y AMD intenta marcar diferencias: integrar, estandarizar, reutilizar y apoyarse en hardware disponible para evitar sobreingeniería.

En el plano del software, la estandarización de interfaces y telemetría para control cuántico será clave. Sin APIs y protocolos comunes, cada laboratorio acaba reinventando su propia rueda, frenando la transferencia de conocimiento y complicando los despliegues multi-proveedor.

Finalmente, la formación de equipos híbridos —gente que entienda de control en tiempo real, teoría de códigos, electrónica de baja latencia y modelado cuántico— es un cuello de botella de talento. La buena noticia es que la apuesta por plataformas abiertas y colaboración con centros de supercomputación crea cantera y acelera el aprendizaje.

Cómo encaja la novedad con lo que ya existe

Lo que se ha anunciado no reemplaza nada; se suma a lo que ya funciona. CPU para flujos de control y gestión, GPU para cómputo intensivo y entrenamiento, FPGA para determinismo de latencia y control fino, y el hardware cuántico para los núcleos de cálculo donde merece la pena. Ese reparto, bien coreografiado, es el que da opciones de llevar la cuántica del laboratorio a la empresa.

Tampoco es casualidad que IBM hable de demostraciones integrales a corto plazo: mostrar un pipeline completo, con colas de trabajo, sincronización y monitorización, hace tangible la promesa. Se pasa del “PowerPoint” a tuberías reales que se pueden medir, depurar y versionar.

En paralelo, otras grandes como Google y Microsoft seguirán apretando para marcar sus propios hitos. La competencia beneficia al sector: acelera la estandarización, multiplica las herramientas y, sobre todo, acorta el tiempo entre un paper y un servicio utilizable.

El impacto económico y las señales al inversor

Más allá del laboratorio, el mercado escuchó el mensaje. Los saltos de IBM y AMD en bolsa tras el anuncio encajan con un patrón conocido: cuando hay avances que acercan la cuántica a su explotación comercial, los flujos se mueven hacia los proveedores que pueden ejecutarlos a escala.

Dicho esto, conviene recordar lo obvio: no es una recomendación de inversión. Algunos medios que recogieron la noticia lo hicieron con la cautela de siempre: el rendimiento pasado no garantiza nada y cada lector debe valorar riesgos y horizontes antes de mover ficha. El interés aquí es tecnológico y de ecosistema, no de operativa bursátil.

Con todo, la señal que queda es potente. El mercado no solo premia la IA; también aplaude pasos concretos hacia la cuántica práctica, especialmente cuando se apoyan en hardware accesible y estrategias híbridas que reducen la incertidumbre de adopción.

La foto que se dibuja es clara: la informática del futuro no será “cuántica” o “clásica”, será las dos a la vez. El anuncio de IBM de ejecutar corrección de errores cuánticos en FPGA de AMD, con margen de rendimiento y en hardware disponible, coloca una pieza clave en ese puzle. El resto —estandarización, talento, latencia y coste— se está trabajando a buen ritmo; si la trayectoria se mantiene, veremos cada vez más pipelines híbridos resolviendo problemas que, hasta hace poco, parecían fuera de alcance.