Quizás no sabes qué es el IMC, pero resulta un factor decisivo que actúa entre la memoria RAM y la CPU. Es importante conocer qué es, su funcionamiento y también muy especialmente sus límites y deterioro. A todo esto dedicamos este artículo de hoy.

No hay que confundir el término IMC que aquí vamos a explicar con el término IMC (In-memory Computer), que también hemos hablado de él. En el caso de este otro IMC, se trata de algo diferente…

¿Qué es un controlador de memoria integrado o IMC?

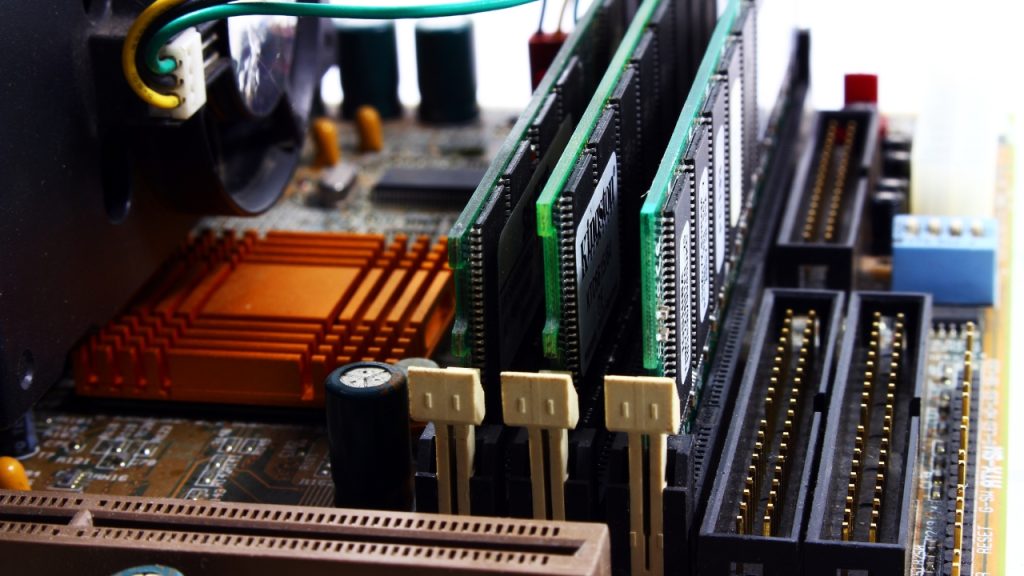

El controlador de memoria es un circuito digital que gestiona el flujo de datos que va y viene de la memoria principal o memoria RAM de un ordenador. Puede ser un chip independiente o estar integrado en otro chip, como puede ser el chipset (en el Northbridge) como se hacía anteriormente, o dentro del propio microprocesador, como se hace actualmente. En este último caso, generalmente se le llama controlador de memoria integrado (IMC, por sus siglas en inglés).

A veces, también se le denomina controlador de chips de memoria (MCC o Memory Chip Controller) o unidad de control de memoria (MCU o Memory Controller Unit). Una forma común de controlador de memoria es la unidad de gestión de memoria (MMU o Memory Management Unit), que se emplea en las arquitecturas que hacen uso de memoria virtual, como la inmensa mayoría de la actualidad.

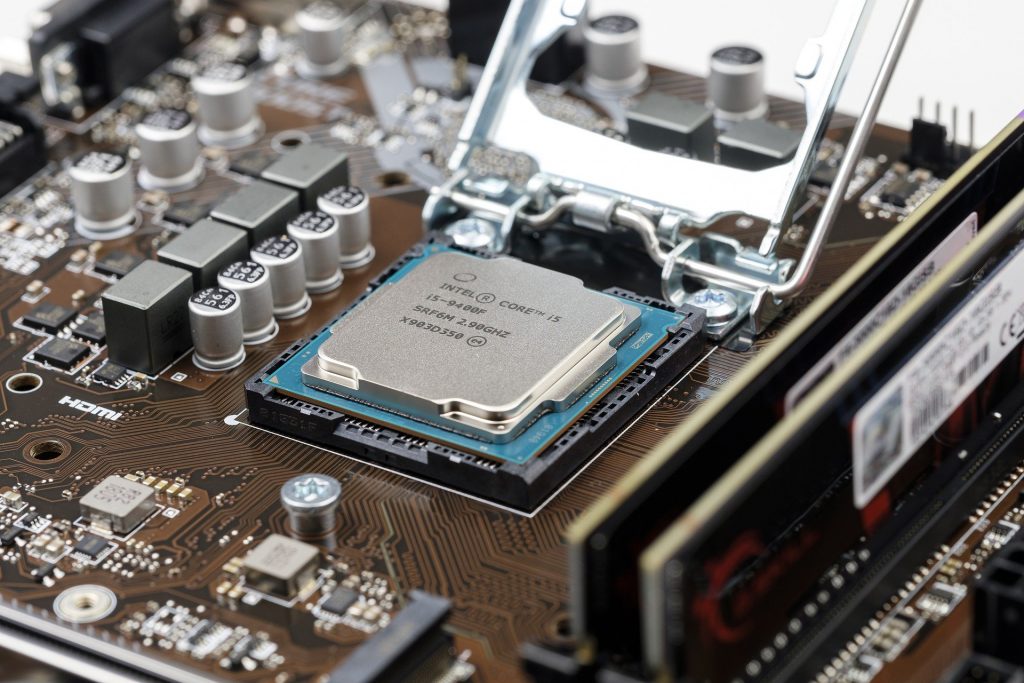

La mayoría de los microprocesadores modernos utilizan un controlador de memoria integrado (IMC), incluyendo microprocesadores de Intel, AMD y aquellos basados en la arquitectura ARM, entre otros como los IBM POWER5, Oracle UltraSPARC T1, etc. Pero no siempre ha sido así… No obstante, no pienses que desde el IBM POWER5 en adelante se han integrado dentro del procesador, por ejemplo, en el IBM POWER8 se volvieron a sacar como un chip independiente implementado fuera. Concretamente, el POWER8 usaba chips controladores Centaur externos montados en los propios módulos de memoria DIMM, actuando a la vez como una memoria caché L4 externa. Aunque con el paso de la DDR3 a la DDR4, volvieron a estar integrados en esta arquitectura.

Algunos microprocesadores de la década de 1990, como el DEC Alpha 21066 y el HP PA-7300LC, tenían controladores de memoria integrados. Sin embargo, en lugar de ser implementados para mejorar el rendimiento, se llevó a cabo para reducir el coste de los sistemas al eliminar la necesidad de un controlador de memoria externo.

Sin embargo, en los procesadores x86 para escritorio, esto llegó algo más tarde, el pionero fue nuevamente AMD. Antes de AMD Athlon64/Opteron (K8), en 2003, los microprocesadores tenían un controlador de memoria implementado en el northbridge de su placa base, es decir, en el chipset, como he comentado anteriormente. A partir de K8 y posteriores, AMD empleó un controlador de memoria integrado dentro del propio microprocesador, permitiendo así acelerar la comunicación entre la memoria RAM y la CPU. Intel hizo lo mismo en su microarquitectura Nehalem (2008), resultando así prescindible el nortbridge del chipset, como ya debes saber…

Aunque un controlador de memoria integrado tiene el potencial de aumentar el rendimiento del sistema, reduciendo la latencia de memoria, también tiene una gran desventaja, y es que limita a la CPU a usar solo un tipo/s de memoria RAM soportados por el controlador. Por ejemplo, los actuales Intel o AMD pueden usar DDR4 o DDR5, pero no podrían usar una DDR3 o una DDR6 si estuviese disponible, ya que para eso hace falta modificar el chip para implementar una MMU diferente que pueda soportar estas otras tecnologías de memoria principal. Mientras que si está en el nortbridge o de forma independiente en la placa base, podría cambiarse este elemento y el microprocesador aceptaría la memoria que pueda aceptar el chip de la placa base, sin dependencias.

¿Para qué sirve el IMC?

Los controladores de memoria, o IMC, contienen la lógica necesaria para leer y escribir en la memoria DRAM y para «refrescar» dicha memoria, como es necesario. Como debes saber, sin refrescos constantes, la DRAM perderá los datos escritos en ella ya que los condensadores que componen las celdas de memoria se descargan en una fracción de segundo (no más de 64 milisegundos según los estándares JEDEC).

La lectura y escritura en la DRAM se realiza seleccionando las direcciones de datos de fila y columna de la DRAM como entradas al circuito multiplexor, donde el demultiplexor en la DRAM utiliza las entradas convertidas para seleccionar la ubicación de memoria correcta y devolver los datos, que luego se consolidan a través de un multiplexor para reducir el ancho de bus requerido para la operación. Es decir, el IMC sirve para direccionar la memoria, para que la CPU pueda tener acceso a ella.

El ancho del bus es la cantidad de líneas paralelas disponibles para comunicarse con la celda de memoria. Los anchos de bus de los controladores de memoria varían desde 8 bits en sistemas más antiguos, hasta 512 bits en sistemas más complejos. Muchos procesadores suelen usar canales de 128-bit, aunque también los hay con mayores anchos como es el caso de los M2 Pro, que llegan a los 256-bit, los M2 Max a los 512-bit y los M2 Ultra llegan a los 1024-bit. Lo mismo sucede en las GPUs, que usan memorias GDDR o HBM que suelen usar canales más anchos.

Algunos controladores de memoria, como el integrado en los procesadores PowerQUICC II, incluyen hardware de detección y corrección de errores. De esta forma, se reduce la posibilidad de errores en algunos embebidos críticos. Algo parecido ocurre en las memorias ECC que se usan en estaciones de trabajo, servidores o HPC.

Para finalizar, me gustaría agregar que los IMC, sean del tipo que sean, pueden presentar problemas de seguridad, ya que se podrían usar con algunos vectores de ataque para vulnerar los sistemas. Algunos controladores de memoria modernos, para mejorar la seguridad, incluyen sistemas de barajado de memoria, es decir, la información almacenada se almacena en sectores de la memoria que se eligen de forma seudoaleatoria.

Intel y ASUS tienen sus propios sistemas de barajado de memoria, es decir, no se usan los estándares. No obstante, se pueden desactivar desde el firmware.

También se pueden usar controladores de memoria que cifren los datos, lo que también mejoraría la seguridad ante posibles ataques usando herramientas de análisis forense o ingeniería inversa basado en la remanencia de datos que dejan las celdas DRAM. Por eso hay que implementar estas mejoras que hagan los ataques ineficaces.

Sin embargo, el barajado de memoria solo se ha diseñado para abordar problemas eléctricos relacionados con la DRAM. Para complementar, un sistema de cifrado es complementario para evitar otros ataques.

Tipos de controlador de memoria

Para saber más, hay que conocer qué tipos de IMC tenemos, y hay que destacar en este sentido:

- Controlador de memoria según el tipo: a lo largo de la historia la memoria RAM ha sufrido muchos cambios de tecnologías, como la Rambus, EDO, SDRAM, etc. Por ejemplo, tenemos los controladores de memoria DDR (Double Data Rate) se utilizan para gestionar la memoria DDR SDRAM, donde los datos se transfieren en los flancos ascendentes y descendentes del reloj de memoria del sistema. Los controladores de memoria DDR son significativamente más complicados en comparación con los controladores de tasa de datos única, pero permiten transferir el doble de datos sin aumentar la velocidad del reloj de la celda de memoria ni el ancho de bus.

- Controlador de memoria multicanal: son controladores de memoria donde los dispositivos DRAM se separan en múltiples buses diferentes para permitir que el controlador de memoria (o controladores) acceda a ellos en paralelo. Esto aumenta la cantidad teórica de ancho de banda del bus por un factor igual al número de canales. Aunque un canal para cada celda de DRAM sería la solución ideal, agregar más canales es muy difícil debido a la cantidad de interconexiones, la capacitancia de las líneas y la necesidad de que las líneas de acceso paralelo tengan longitudes idénticas.

- Controlador para FB-DIMM: los sistemas de memoria completamente bufferizada colocan un dispositivo de memoria intermedia en cada módulo de memoria (llamado FB-DIMM cuando se utiliza Fully Buffered RAM), que, a diferencia de los dispositivos tradicionales de controlador de memoria, utilizan una conexión de datos en serie con el controlador de memoria en lugar de la conexión en paralelo utilizada en diseños de RAM anteriores. Esto reduce la cantidad de cables necesarios para colocar los dispositivos de memoria en una placa base (lo que permite utilizar un menor número de capas, lo que significa que se pueden colocar más dispositivos de memoria en una sola placa), a costa de aumentar la latencia (el tiempo necesario para acceder a una ubicación de memoria). Este aumento se debe al tiempo requerido para convertir la información en paralelo leída desde la celda DRAM al formato en serie utilizado por el controlador FB-DIMM, y luego de nuevo a una forma en paralelo en el controlador de memoria en la placa base.

- Controlador de memoria flash: muchos dispositivos de memoria flash, como las unidades flash USB, los chips eMMC, y las unidades SSD, incluyen un controlador de memoria flash. La memoria flash es inherentemente más lenta de acceder que la RAM y a menudo se vuelve inutilizable después de unos pocos millones de ciclos de escritura, lo que generalmente la hace inadecuada para aplicaciones de RAM.

IMC: un factor limitante a la hora de comprar módulos de memoria RAM

A pesar de lo que podría parecer, no siempre más es mejor en términos de memoria RAM, de esto ya hemos comentado algo en otros artículos anteriores sobre cómo elegir la memoria RAM. A menudo, las marcas promocionan módulos y kits de memoria RAM de alta velocidad con latencias extremadamente bajas, o módulos acelerados mediante overclocking. Esto podría dar la impresión al usuario que estos módulos con una mayor frecuencia de reloj también tienen un mejor rendimiento. Sin embargo, la realidad es bastante diferente, ya que la memoria RAM es uno de los factores más limitantes en el rendimiento de un sistema, y hay que elegir una frecuencia que pueda extraer el máximo de la CPU, a lo que se le conoce como punto dulce.

Por un lado, siempre hay que fijarse en el soporte de frecuencia que admite una CPU/chipset/placa base (plataforma), ya que no siempre toleran todas las frecuencias de memoria RAM existentes en el mercado. De hecho, los primeros diseños de una arquitectura pueden soportar solo los valores más bajos de frecuencia. Esta limitación de velocidad en las placas base varía según el modelo y el rango de precios, donde las placas de gama alta suelen ofrecer el soporte más completo para velocidades de memoria. Por ejemplo, podríamos tener módulos de memoria RAM DDR5 6400 soportados por una placa base, mientras que quizás tengamos en el mercado módulos de hasta 8000…

Es decir, un factor crítico es el IMC. Muchos procesadores, como los de Intel y AMD, especifican cuál es la memoria o rango de memoria óptima que hay que usar. Sin embargo, aumentar la velocidad de la memoria RAM más allá de esta especificación implica un mayor voltaje, la aparición de jitter en la señal y, en función de la velocidad de los módulos, puede que el IMC no sea capaz de mantener la sincronización a dicha velocidad, ya que están limitados de serie a una frecuencia máxima a la que pueden mantener comunicaciones estables.

Superar superar mediante overclocking los rangos de memoria recomendados, no siempre se traduce en un aumento de rendimiento, hay que saber más sobre esto para asegurar que acelerando la frecuencia se puEda conseguir realmente una ganancia de rendimiento. Y, lo más importante, que el IMC pueda trabajar de forma estable, ya que de lo contrario se transformaría en bloqueos del sistema, pantallazos azules o kernel panic, errores, reinicios inesperados, etc.

Problemas en el IMC

Para finalizar, hay que decir que hay dos factores muy críticos a la hora de la comunicación CPU-RAM, uno de ellos es el propio IMC y el otro la caché. Es esencial ajustar los voltajes y comprender dónde se encuentra el punto óptimo o dulce para cada uno de ellos si queremos evitar problemas como he comentado anteriormente. En tales casos, podrías verte obligado a realizar ajustes en los voltajes o incluso a cambiar los módulos de memoria por otros de menor velocidad o mayor latencia para que el IMC trabaje de forma más desahogada.

Además, no es una solución viable aplicar un voltaje excesivo o minimizarlo al máximo, ya que el voltaje del IMC debe ser preciso y adecuado para garantizar una señal con el menor jitter posible y, por lo tanto, un desgaste mínimo. Es decir, las prácticas de undervolting y overvolting se deben hacer con mucho cuidado. Es importante destacar que superar la velocidad de memoria recomendada también implica un desgaste acelerado que a menudo se pasa por alto, pero que puede terminar con que tu equipo tiene una vida útil más corta.

Por otro lado, hay que decir que trabajar de forma puntual a frecuencias superiores no suele suponer un problema en muchos casos, pero sí cuando se hace de forma más continuada o prolongada, haciendo que el IMC se degrade y termine por dejar de funcionar. Por tanto, ten la precaución de elegir la memoria RAM adecuada para tu sistema y no fuerces la misma mediante overclocking/overvolting si lo que buscas es fiabilidad. No obstante, los perfiles Intel XMP y los AMD EXPO pueden ayudarte a mejorar el rendimiento de tu sistema de forma más segura con sus perfiles pre-establecidos.