- wafer.space abre una corrida conjunta en GF180MCU con PDK abierto y 1.000 piezas por diseño de hasta 20 mm².

- Compatibilidad con herramientas abiertas (LibreLane, Magic, KLayout) y RISC‑V como ISA ideal para chips personalizados.

- El contexto industrial está marcado por la escasez de GPU y grandes planes de inversión para ampliar capacidad.

El interés por los chips a medida está viviendo un momento dulce y, en este contexto, wafer.space se presenta como una puerta de entrada para quien quiera llevar un diseño propio a silicio real sin tener que montar una fábrica. Su propuesta aterriza sobre un proceso comercial maduro y con kits de diseño abiertos, poniendo la barrera de entrada mucho más baja que en el pasado.

Al mismo tiempo, el panorama global está repleto de movimientos industriales: desde la escasez de GPU que frena la IA hasta las iniciativas para ampliar capacidad de fabricación. Entre estos dos extremos —acceso “maker” al silicio y macroinversiones— se dibuja una foto bastante completa de hacia dónde va el sector.

Qué propone wafer.space: una “OSH Park” del silicio con GF180MCU

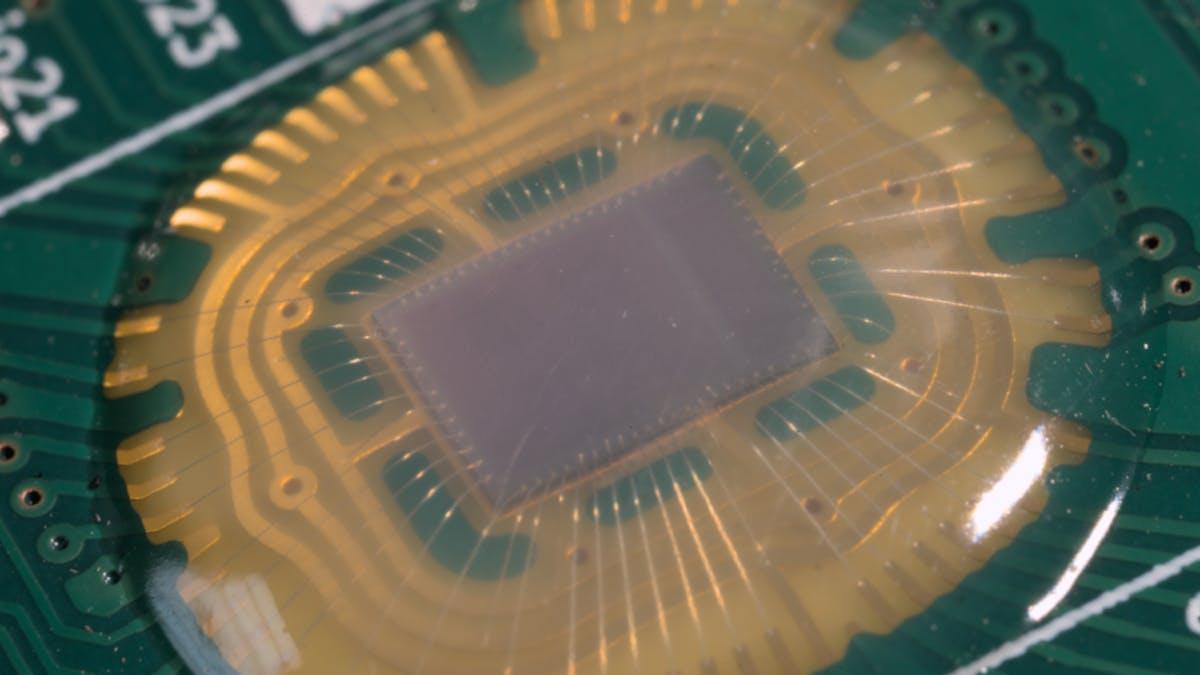

wafer.space ha abierto su primera corrida de fabricación conjunta (Run 1) en el proceso GF180MCU, con fecha límite de compra fijada para el 28 de noviembre de 2025. La referencia a “OSH Park para silicio” no es casual: igual que aquel servicio popularizó la fabricación colaborativa de PCBs, aquí se consolida un modelo tipo shuttle en el que múltiples diseños comparten un mismo wafer para abaratar costes y tiempos de entrega. Más detalles del anuncio pueden consultarse en la página del proyecto en Crowd Supply.

La pauta es clara: aportas un diseño de hasta 20 mm2 en GF180MCU y a cambio recibes 1.000 piezas. Este planteamiento favorece prototipos avanzados y series cortas de producto, algo muy difícil de alcanzar por cuenta propia. Además, el flujo está pensado para admitir tanto plantillas preexistentes como desarrollos desde cero, con la flexibilidad adicional de elegir entre herramientas de código abierto o propietarias.

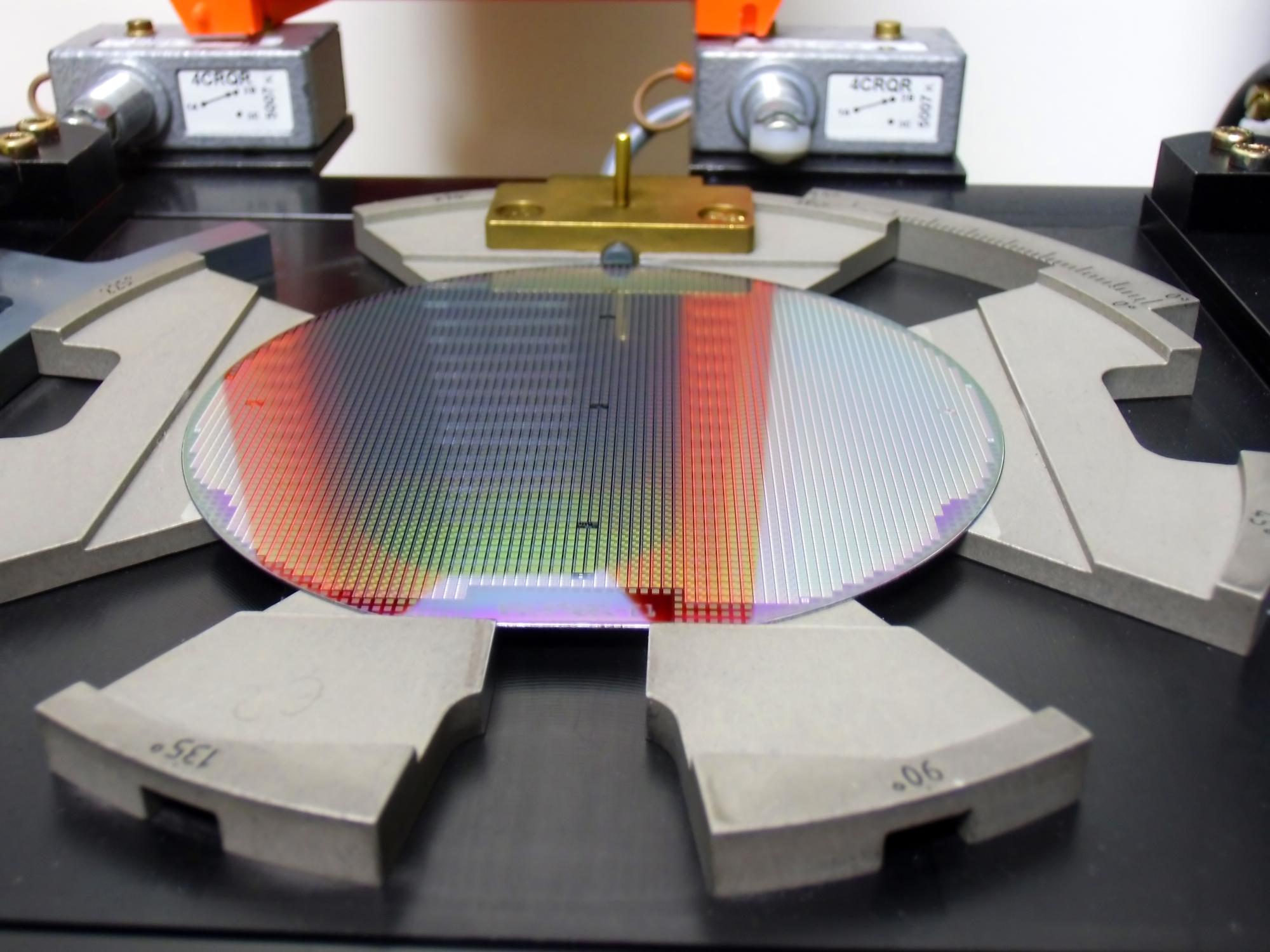

El proceso GF180MCU cuenta con PDK abierto, documentado públicamente en gf180mcu-pdk.readthedocs.io. Esta apertura es crucial: permite verificar reglas de diseño (DRC), extracción (LVS) y flujos de síntesis y place&route sin pagar licencias prohibitivas, algo que hasta hace poco solo estaba al alcance de grandes empresas o universidades con convenios especiales.

Si optas por herramientas libres, el ecosistema menciona expresamente LibreLane, Magic y KLayout entre las compatibles; si prefieres herramientas comerciales, también son válidas. En cualquiera de los casos, el itinerario no exige anillo de pads ni CPU de gestión obligatorios, lo que simplifica mucho el esqueleto del chip cuando tu objetivo es probar un bloque concreto o una combinación de periféricos e IP propia.

Para quien quiera ir deprisa, se puede partir de una plantilla existente y concentrarse en la lógica diferencial del proyecto (por ejemplo, un acelerador, un periférico especial o un microcontrolador adaptado), mientras que los más puristas pueden construir su layout completo desde cero siguiendo las reglas del PDK. Esa libertad de elección es la que acerca el silicio “real” a perfiles muy diversos, desde makers avanzados a pymes de hardware.

Una duda recurrente gira en torno al mantra de los “7 dólares por die”. En las fuentes revisadas que acompañan a esta información no aparece un desglose oficial de precio por unidad con esa cifra concreta; por tanto, conviene tratarla como un lema o cálculo orientativo que circula en la comunidad, mientras el dato firme aquí es la combinación de límite de área (20 mm²), proceso (GF180MCU), PDK abierto y lote de 1.000 piezas. La relación coste/volumen dependerá del paquete, opciones y condiciones de la corrida.

Que el PDK sea abierto no significa ausencia de rigor: las reglas de diseño y verificación siguen siendo estrictas, y ese es precisamente el valor de una plataforma que unifica el acceso. Donde antes había barreras por licencias y NDA, ahora hay documentación pública y flujos reproducibles, lo que facilita auditorías, formación y colaboración entre perfiles de diseño, verificación y fabricación.

RISC‑V como catalizador: del CH32V003 de 0,10 $ a estaciones de 64 núcleos

Una de las razones por las que esta ventana al silicio resulta tan atractiva es el claro avance de RISC‑V. Se pronuncia “risk‑faiv” y es una ISA modular, extensible y libre de licencias. Nació en entornos académicos (Berkeley) y hoy se encuentra en un abanico que va desde el microcontrolador CH32V003 de unos 0,10 dólares hasta proyectos como la iniciativa paneuropea de supercomputación, pasando por estaciones con 64 núcleos a 2 GHz en el rango profesional.

RISC‑V encaja como un guante en chips personalizados: puedes integrarlo como núcleo blando en un FPGA durante la fase de prototipado lógico, y después migrar al silicio de una corrida compartida cuando el diseño esté maduro. También existe la vía de implementar una máquina virtual de alto rendimiento si el objetivo es correr software con compatibilidad RISC‑V sin tocar hardware. Más información institucional y del ecosistema en riscv.org.

Para equipos pequeños, disponer de una ISA abierta evita renegociar licencias o comprimir el diseño a una IP cerrada: los costes de oportunidad bajan y aumentan las opciones de iteración rápida. En flujos con PDK abierto, esta combinación (ISA abierta + PDK abierto) es especialmente atractiva para docencia, investigación aplicada y startups que aún están buscando producto‑mercado.

Si el plan pasa por un microcontrolador a medida, la pila típica incluirá: síntesis del core RISC‑V elegido (desde opciones minimalistas hasta diseños más completos), integración de periféricos (GPIO, UART, I2C, SPI, temporizadores), memoria (SRAM, quizá flash externa) y, llegado el caso, un pequeño acelerador específico. Con un área de 20 mm² hay margen razonable para un MCU con periféricos y lógica personalizada.

Para quienes ya tienen IP propia (por ejemplo, un bloque criptográfico, DSP o acelerador para IA clásica), el valor de RISC‑V como “control plane” ligero y portable es enorme: no necesitas encajar tu lógica alrededor de una CPU cerrada ni someterte a cadenas de herramientas exclusivas. La interoperabilidad con herramientas libres como Magic o KLayout hace más transparente el ciclo diseño‑verificación.

Contexto industrial: escasez de GPU y la carrera por más capacidad de fabricación

Mientras florecen propuestas que democratizan el acceso al silicio, el mapa macro de la industria vive tensiones sin precedentes: las GPU son un cuello de botella para entrenar y desplegar modelos de IA, y eso empuja a actores de primer nivel a replantearse la cadena de suministro.

Según Bloomberg, OpenAI explora levantar entre 8.000 y 10.000 millones de dólares para construir una red propia de fundición de chips a medida, con interés de G42 (Abu Dabi) y SoftBank (propietaria de ARM). La idea sería impulsar aceleradores específicos que alimenten ChatGPT y otros modelos, reduciendo dependencia de terceros y asegurando disponibilidad.

En paralelo, The Wall Street Journal informó —según personas familiarizadas— de conversaciones para recaudar entre cinco y siete billones de dólares destinados a ampliar drásticamente la capacidad de fabricación de semiconductores para IA. En ese relato aparecen fondos soberanos de los EAU, Masayoshi Son (SoftBank) y representantes de TSMC, el mayor puro‑play de foundry del mundo y socio clave de Nvidia, Apple, Intel o AMD. No hay confirmación pública de acuerdos cerrados a esa escala.

La cifra contrasta con movimientos ya anunciados: la administración Biden comunicó una inversión de 5.000 millones de dólares en I+D para tecnologías de semiconductores en Estados Unidos, y TSMC comprometió 40.000 millones de dólares en su fábrica de Arizona, una de las mayores inversiones extranjeras en el país. Además del empuje económico, entran en juego consideraciones geopolíticas por el posible peso de capital extranjero en una industria crítica.

Este telón de fondo ayuda a entender por qué iniciativas como la de wafer.space generan tanto interés: la demanda de silicio crece y la cadena de suministro de vanguardia está tensionada; abrir vías ordenadas para tecnología madura como GF180MCU no solo es útil para educación y prototipado, también es una válvula de escape realista para pymes y equipos de I+D que necesitan iterar sin esperar nodos punteros.

Recursos enlazados y señales del ecosistema

En los materiales revisados aparecen enlazados recursos que ayudan a contextualizar el ecosistema. Por un lado, el Directorio de AESEMI —asociación española del semiconductor— que aglutina actores de la cadena de valor local; está disponible como PDF en este enlace. Para equipos en España, entender quién hace qué es clave para cerrar el círculo (IP, empaquetado, test, etc.).

También se enlaza una publicación de la OMPI (WIPO), accesible en wipo.int. En el material original aparecía un bloque de datos binarios —el típico encabezado “PK” de un ZIP o ePub— que no aporta contenido legible dentro del artículo, pero sirve para recordar que la propiedad intelectual y las mejores prácticas de publicación forman parte del día a día cuando pensamos en IPs, licencias y documentación técnica de chips.

Desde el frente normativo aparece un PDF de EUR‑Lex en portugués (formato oficial de la UE) accesible en esta URL. Aunque no se detalla su contenido en el extracto, es un recordatorio de que la regulación europea —ya sea en ayudas, estándares o guías— condiciona el marco en que operan empresas y consorcios del semiconductor.

Además, se observa un pequeño bloque de interfaz con la etiqueta “Members / Online”. Este tipo de elementos UI suele indicar que la información proviene o se contrasta en comunidades activas (foros, hubs o secciones de miembros), donde se comparte experiencia práctica y soporte. Para quien se lance a un shuttle, tener comunidad a mano acelera la curva de aprendizaje.

Un apunte sobre contenido no relacionado en los resultados

Entre los fragmentos recopilados se coló una reseña de una panadería en Nebraska, próxima a Lisa Radial Cafe. El texto —primero traducido y luego en inglés— elogia bollos gigantes (por ejemplo, el de frambuesa), barras de tarta de cerezas y una barrita de tahini con butterscotch que “se deshace en la boca”, con un guiño a apoyar negocios locales. Es un buen ejemplo de cómo, en búsquedas amplias, pueden aparecer resultados ruidosos o desconectados del tema principal.

Más allá de la anécdota gastronómica, lo relevante para nuestra intención de búsqueda es separar las fuentes técnicas o de industria (wafer.space, PDKs, RISC‑V, análisis de capacidad) de los resultados que no aportan contexto. Un filtrado fino de fuentes es clave cuando se toma una decisión de fabricar un prototipo: fechas límite, requisitos de PDK, herramientas compatibles y expectativas de entrega pesan más que cualquier otro ruido.

La iniciativa de wafer.space enlaza muy bien con el auge de RISC‑V y las herramientas abiertas, y lo hace en un momento en que la industria vive tensiones de oferta en los nodos de alto rendimiento por la demanda de IA. Para equipos con ganas de aprender haciendo, y para pymes que necesitan iterar en hardware real, un shuttle con PDK abierto es una manera sensata de acercar el silicio a la mesa sin tener que competir por wafers en procesos punteros ni asumir costes inasumibles.