- La SOT-MRAM logra 0,35 ns y 156 fJ sin campo auxiliar, manteniendo E/kBT≈70 y TMR≈170%.

- El tungsteno, por su alta eficiencia de torque de espín, reduce la energía de escritura y acelera la conmutación.

- STT-MRAM ya se comercializa en entornos aeroespaciales con alta resistencia, -40 a 125 ºC y 45 ns de acceso.

- La combinación de SOT, materiales pesados y rutas multiferroicas acerca la MRAM a reemplazar SRAM en ciertos niveles.

La memoria SOT-MRAM con capa de tungsteno se ha colado en el debate de alto nivel sobre el futuro de la computación por una razón clara: promete unir velocidad de vértigo, no volatilidad y un consumo energético bajísimo en el mismo chip. En plena era de la IA y el IoT, donde cada miliwatio cuenta, esta tecnología magnetorresistiva apunta a redefinir tanto la RAM de alto rendimiento como el almacenamiento no volátil.

Más allá del titular, lo que de verdad está cambiando el juego son avances concretos: celdas que escriben en 0,35 nanosegundos sin campo auxiliar, potencias de escritura de apenas 156 fJ y mejoras del 35% frente a generaciones previas de SOT. Todo ello manteniendo estabilidad térmica y una relación TMR muy alta, ingredientes clave para llevar la MRAM del laboratorio a la fábrica de 300 mm y, después, al portátil, al móvil o al centro de datos.

Qué es la SOT-MRAM y por qué todo el mundo habla de ella

La SOT-MRAM (Spin-Orbit Torque MRAM) es una variante de la MRAM que emplea torques de órbita-espín generados en capas metálicas pesadas para conmutar el estado magnético de una “capa libre” dentro de una unión de túnel magnética (MTJ). A diferencia de la DRAM y la SRAM, no necesita refresco; y frente a la flash, escribe rápido, sin altos voltajes y con resistencia prácticamente ilimitada.

En una MTJ típica conviven una capa ferromagnética fija (referencia), una barrera aislante ultrafina y una capa ferromagnética libre cuya orientación podemos cambiar. Si ambas capas están alineadas, la resistencia es menor; si quedan antiparalelas, la resistencia aumenta. Esa diferencia se mide en lectura para codificar 0/1, de forma no destructiva y muy veloz.

La SOT-MRAM sitúa la corriente de escritura en un plano paralelo a la celda, usando el efecto Hall de espín en materiales como tungsteno, tantalio o platino para inyectar momento angular en la capa libre. ¿La ventaja? Velocidades altísimas y menos desgaste, además de separar físicamente los caminos de lectura y escritura, algo que mejora la fiabilidad del conjunto.

Física en dos pinceladas: espín, MTJ y las dos rutas de conmutación (STT vs SOT)

El espín del electrón puede imaginarse como una pequeña brújula cuántica que apunta “arriba” o “abajo”. La magnetorresistencia de túnel surge porque los electrones atraviesan la barrera aislante con distinta probabilidad según la alineación relativa de ambas capas ferromagnéticas. Esa variación de resistencia es la base de la lectura de las celdas MRAM.

En STT-MRAM (Spin Transfer Torque), la corriente fluye a través de la MTJ y transfiere torque de espín para reorientar la capa libre. Es la opción más madura comercialmente, muy extendida en microcontroladores y sistemas embebidos. En SOT-MRAM, la corriente circula por una capa metálica adyacente; mediante efecto spin Hall se genera una corriente de espín que conmuta la capa libre. La SOT suele ser más rápida y menos intrusiva en la MTJ, con un futuro brillante como candidata a reemplazar SRAM en cachés.

Se han explorado, además, soluciones complementarias como dispositivos multiferroicos donde campos eléctricos ayudan a fijar o invertir magnetizaciones, y diseños “canted” (inclinados) que facilitan la escritura sin necesidad de campo auxiliar externo, simplificando el circuito y mejorando la eficiencia.

El salto de Tohoku: 0,35 ns, 156 fJ y escritura sin campo auxiliar

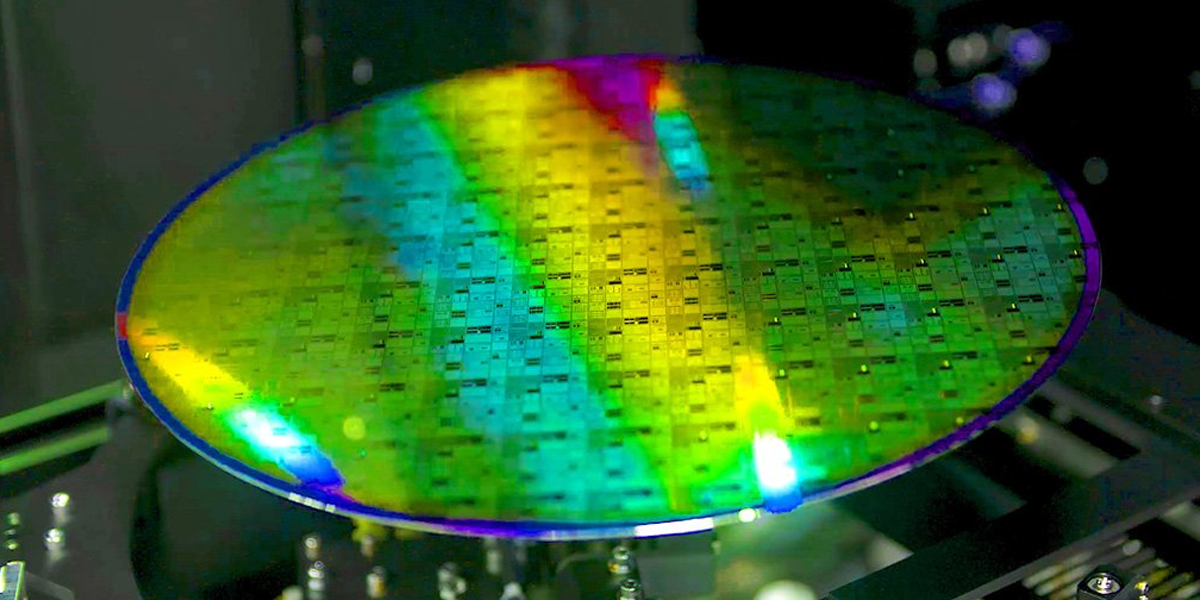

Un equipo de la Universidad de Tohoku ha demostrado una SOT-MRAM inclinada capaz de escribir en 0,35 nanosegundos sin emplear campo magnético externo. La clave está en un diseño “canted” con un ángulo de 75° y su optimización mediante simulación micromagnética y proceso de oblea de 300 mm, apto para escalar a fabricación industrial.

La optimización del ángulo y de la anisotropía de la capa libre ha permitido reducir la potencia de escritura hasta 156 femtojulios, un 35% menos que tecnologías SOT previas comparables, manteniendo un factor de estabilidad térmica E/kBT de 70 (estabilidad frente a fluctuaciones térmicas) y una relación TMR muy alta (del 170%). Dicho de otra manera: velocidad tope, consumo ínfimo y robustez.

Estos parámetros despejan tres grandes barreras: rendimiento, eficiencia y compatibilidad con un flujo de fabricación de 300 mm. Con ello se abre la puerta a su uso en centros de datos, desarrollo de IA, IoT, smartphones y sistemas embebidos exigentes, donde la combinación de no volatilidad y baja energía es oro puro.

Todo esto se alinea con un objetivo que el propio equipo expresó: adaptar la MRAM a una sociedad acelerada por la IA y el Internet de las Cosas, priorizando reducir la energía de escritura sin renunciar a las velocidades ultrarrápidas que demanda el hardware actual.

Qué aporta la capa de tungsteno en SOT-MRAM

En dispositivos SOT, la capa metálica pesada que genera el torque de órbita-espín es crucial. El tungsteno (especialmente en su fase β) destaca por un ángulo Hall de espín elevado, lo que se traduce en mayor eficiencia para convertir corriente de carga en corriente de espín. En cristiano: menos energía para cambiar el bit y conmutaciones más ágiles.

Junto al tungsteno, se emplean con frecuencia metales como tantalio o platino. De hecho, investigaciones académicas han mostrado mejoras al incorporar láminas nanométricas de platino bajo capas magnéticas, facilitando la conmutación y reduciendo consumo en operaciones de escritura. En todos los casos, la idea es la misma: materiales con fuerte acoplamiento espín-órbita que inyectan espín de manera eficaz en la capa libre.

La elección del metal pesado impacta en parámetros críticos: corriente de escritura (y por tanto potencia), fiabilidad a alta velocidad, compatibilidad con el apilado de la MTJ y con el BEOL del proceso CMOS. El tungsteno brilla por su eficiencia de SOT, pero la industria también valora su integración en procesos avanzados, algo clave si pensamos en nodos de vanguardia.

Conviene remarcar que los avances de Tohoku en celdas inclinadas se centran en la arquitectura y la ingeniería de anisotropías, mientras otras líneas, como las basadas en láminas de platino o en aproximaciones multiferroicas, exploran caminos complementarios. Todo suma a un objetivo común: menos energía por bit, más velocidad y procesos compatibles con producción masiva.

MRAM y STT-MRAM hoy: productos reales, radiación y entornos extremos

Mientras SOT-MRAM afina su salto a gran escala, la STT-MRAM ya está en el mercado. Hay dispositivos de 64 Mb y 1 Gb orientados a aplicaciones aeroespaciales y espaciales con encapsulados cerámicos herméticos (CLGA/CBGA) y variantes RAD-HARD, RAD-Tolerant y sin endurecimiento específico. Son memorias con acceso verdaderamente aleatorio de lectura y escritura, alta resistencia al flujo magnético (menos necesidad de apantallado) y un perfil de potencia excelente.

En entornos duros, estos componentes garantizan retención de datos superior a 10 años entre -40 y +125 °C, con tensiones típicas de 2,7 a 3,6 V y tiempos de acceso mínimos de alrededor de 45 ns en el rango militar. Es decir, no solo no se inmutan ante la radiación, sino que además rinden con total solvencia en condiciones térmicas exigentes.

La evolución reciente ha multiplicado densidades: un salto desde 16 Mb hasta 64 Mb en el mismo formato, y hasta 1 Gb (32M x 32) con tecnología pMTJ STT-MRAM de 22 nm. Se habla de mejoras en densidad por bit en el orden de varios miles de Mb/mm² frente a generaciones anteriores, lo que indica una senda de escalado que ya es tangible.

Fabricantes y proveedores de alta fiabilidad resaltan que la combinación de bajo consumo, resistencia prácticamente infinita, alto rendimiento y escalabilidad convierte esta MRAM en una alternativa óptima en defensa, aeroespacial, automoción y sistemas embebidos críticos, donde la no volatilidad añade una capa extra de seguridad frente a apagones o fallos.

Comparativas esenciales: MRAM frente a SRAM, DRAM y Flash

La MRAM mezcla virtudes de varias tecnologías: no es volátil como la flash, acelera lecturas y escrituras casi al nivel de la SRAM y ofrece densidades más cercanas a la DRAM. Frente a esta última, evita el refresco (que en DRAM ocurre en torno a miles de veces por segundo), reduciendo consumo en reposo y complejidad de control.

En velocidad, se han documentado accesos en el orden de los 2 ns en MRAM de laboratorio, superando a DRAM de procesos más modernos. Comparada con flash, la diferencia en escritura es abismal: no hay necesidad de pulsos de 10 V con bombas de carga lentas ni degradación por ciclos, por lo que la vida útil es muy superior.

Valores típicos: para hacerse una foto del mapa de memorias hoy:

| Comparativa | MRAM | SRAM | DRAM | Flash |

|---|---|---|---|---|

| Volatilidad | No | Sí | Sí | No |

| Velocidad | Alta | Muy alta | Alta | Baja en escritura |

| Consumo | Bajo | Alto | Medio | Muy bajo en reposo |

Nota: la MRAM destaca por resistencia al desgaste, manteniendo millones/billones de ciclos de escritura sin degradación apreciable, algo fuera del alcance de la flash convencional.

STT-MRAM frente a otras no volátiles: números que importan

Dentro de la familia MRAM, la STT-MRAM presenta ventajas medibles frente a alternativas no volátiles como FRAM, NVSRAM o Toggle MRAM. En tiempos, ciclos y retención, los rangos típicos son los que siguen:

| Punto | STT-MRAM | FRAM | NVSRAM | Toggle MRAM |

|---|---|---|---|---|

| Tipo | No volátil | No volátil | No volátil | No volátil |

| Escritura | Sobrescribir | Sobrescribir | Sobrescribir | Sobrescribir |

| Latencia de escritura | ~25 ns | ~150 ns | ~25 ns | ~35 ns |

| Ciclos R/W | ~1e13 | ~1e14 | ~1e7 | ~1e13 |

| Retención | >20 años | ~10 años | ~20 años | >20 años |

Si la comparamos con EEPROM, flash, SRAM y FRAM, la STT-MRAM ofrece escritura por sobrescritura y sin bombas de carga, con durabilidad muy superior a EEPROM/flash, y sin necesidad de batería como ciertas SRAM con respaldo:

| Punto | STT-MRAM | EEPROM | Flash | SRAM | FRAM |

|---|---|---|---|---|---|

| Tipo | No volátil | No volátil | No volátil | Volátil | No volátil |

| Método escritura | Sobrescribir | Borrar+Escribir | Borrar+Escribir | Sobrescribir | Sobrescribir |

| Escritura típica | ~25 ns | ~10 μs | ~10 μs | ~5 ns | ~150 ns |

| Ciclos R/W | ~1e13 | ~1e6 | ~1e5 | Ilimitado | ~1e14 |

| Bomba de carga | No | Sí | Sí | No | No |

| Batería respaldo | No | No | No | En algunas | No |

Desafíos técnicos: escalado, corrientes y half-select

No todo es perfecto. La fabricación de celdas MRAM exige procesos nanométricos precisos y apilados complejos. En diseños clásicos, la corriente necesaria para escribir era alta y el fenómeno half-select (interferencia en celdas vecinas) limitaba la miniaturización a nodos en torno a 180 nm; variantes con “toggling” empujaron hacia ~90 nm.

Para competir en coste por bit con DRAM/flash, la MRAM debe avanzar hacia nodos más pequeños (históricamente, el listón de 65 nm marcaba un objetivo), y eso ha motivado el salto a STT primero y, ahora, a SOT con capas pesadas como el tungsteno. La SOT-MRAM ayuda a reducir corriente, separar caminos R/W y ganar velocidad, tres piezas del mismo puzle.

También pesa el factor económico: el coste por bit y la densidad útil cuando se empacan grandes arrays. Aun así, la llegada de productos STT comerciales y la madurez de los procesos de 300 mm son señales de que el ecosistema avanza en la dirección adecuada.

El objetivo inmediato es bajar la energía por bit sin sacrificar margen de estabilidad térmica ni TMR, y hacerlo en un flujo CMOS estándar compatible con el back-end de metal de los nodos punteros. La capa de tungsteno y su alta eficiencia de torque es un aliado natural en este camino.

Línea temporal y maduración del mercado

La historia viene de lejos. Desde la memoria de núcleos de ferrita en los años 50, pasando por el descubrimiento de magnetorresistencias en películas delgadas (IBM, 1989) y la oleada de colaboraciones (IBM-Infineon, 2000; NVE con Cypress, 2002), la MRAM ha ido escalando hitos con prototipos de 128 KiB y 1–16 Mibit en procesos de 180–150 nm a mediados de los 2000.

En 2004–2006 vimos a TSMC, NEC, Toshiba y Renesas mostrar prototipos más rápidos (hasta 200 Mbit/s con 34 ns de ciclo y 1,8 V), récords de celdas a 2 GHz y la aparición de barreras de MgO que mejoraban la escritura. Aunque hubo compañías que se apartaron, el campo siguió vivo, con Freescale comercializando chips de 4 Mibit por aquella época.

La irrupción de la STT-MRAM cambió las reglas: Sony enseñó el primer prototipo STT de laboratorio en 2005; y en 2018, Intel anunció fabricación en volumen de MRAM, dejando claro que la tecnología ya no era solo promesa. Desde entonces, el foco está en llevar SOT-MRAM a gran escala como alternativa real a ciertas SRAM.

En cuanto a usos, el abanico es enorme: militar y aeroespacial, smartcards, móviles, cámaras, PCs, estaciones base, reemplazo de SRAM con batería y memorias especiales para registradores tipo “caja negra”. La visión de “memoria universal” —una sola tecnología para cubrir varios roles— no es descabellada.

Nuevas rutas: multiferroicos y campo eléctrico para escribir

Además de SOT, hay frentes disruptivos que miran a la magnetización por campo eléctrico. Investigadores han presentado estructuras multiferroicas heterogéneas con capas finas —por ejemplo, integrando vanadio entre materiales ferroeléctricos y piezoeléctricos— que estabilizan direcciones de magnetización y permiten invertirlas aplicando corriente eléctrica, reduciendo aún más la energía de conmutación.

Estas propuestas demuestran inversión de la dirección magnética estable sin alimentación continua y apuntan a MRAM aún más duraderas y frugales en energía. Quedan cuestiones por resolver, como la degradación de la eficiencia de conmutación con el tiempo, pero el potencial para informática de alto rendimiento y bajo consumo es evidente.

En paralelo, otros trabajos han mostrado que incorporar una lámina nanométrica de platino bajo las capas magnéticas mejora la dinámica de conmutación, apoyando la idea de que la ingeniería fina de interfaces y materiales pesados (W, Ta, Pt) es uno de los aceleradores más claros hacia productos comerciales SOT de nueva generación.

Aplicaciones clave: de la SRAM a la IA, el IoT y la nube

¿Puede la SOT-MRAM sustituir a la SRAM? En rendimiento bruto, la SRAM sigue mandando; pero SOT-MRAM compensa con no volatilidad, menor energía y escalabilidad razonable. Para cachés grandes, NVM de alta velocidad o memoria cercana a la computación (near-memory computing), el equilibrio empieza a favorecer a SOT en ciertos niveles de la jerarquía.

En automoción, la MRAM ya demuestra ventajas: lectura rapidísima, consumo ultrabajo y alta densidad frente a eFlash/eSRAM, empujando la transición hacia vehículos más inteligentes. En móviles y wearables, simplifica diseños al consolidar subsistemas de memoria, recortando consumo y alargando batería sin sacrificar rendimiento.

En PCs y sistemas embebidos, la MRAM puede actuar como caché no volátil, sustituir NOR/SRAM en firmware y, con el tiempo, incluso acercarse a cubrir escenarios tradicionalmente reservados a DRAM o PSRAM cuando la latencia absoluta no sea el factor limitante número uno.

Para centros de datos e IA, la promesa de una tecnología que no traga energía en reposo, con escrituras ultrarrápidas y resistencia extrema, se traduce en TCO más bajo y huella de carbono reducida. Si sumamos la posibilidad de operar sin campo auxiliar, la ecuación operativa se vuelve muy atractiva.

Mirando el conjunto de avances —celdas inclinadas sin campo, capas de tungsteno/platino para SOT eficiente, y aproximaciones multiferroicas— la MRAM va ganando terreno como pilar de la electrónica de alto rendimiento y bajo consumo. El siguiente paso es consolidar estas piezas en nodos de producción con yields competitivos.

La fotografía actual es la de una tecnología que, desde variantes STT comerciales en aeroespacial y embebido hasta prototipos SOT de récord, encaja perfectamente con la hoja de ruta de IA e IoT. Si el coste por bit y el escalado acompañan, veremos SOT-MRAM con capa de tungsteno y afines integradas cada vez más cerca del cómputo, incluso dentro de SoCs de propósito general.

Todo apunta a que la combinación de velocidad (0,35 ns), energía de escritura ínfima (156 fJ), estabilidad térmica elevada (E/kBT~70) y TMR alta (~170%) hará viable su adopción masiva, siempre que el ecosistema fab lo soporte con procesos de 300 mm y compatibilidad CMOS impecable.

Sin destapar champán antes de tiempo, el camino está trazado: STT-MRAM ya resuelve hoy problemas reales en mercados críticos; SOT-MRAM, apoyada en capas de tungsteno y otras ingenierías de materiales, afina lo necesario para plantar cara a la SRAM en determinadas capas de memoria; y las vías multiferroicas ofrecen una carta extra para recortar aún más la energía por bit. La memoria magnetorresistiva se consolida como candidata seria a ser ese comodín que la computación moderna necesitaba.