- La oblea a 2 nm ronda 30.000 $ y el diseño por chip llega a 725 M $.

- TSMC prevé 30.000 obleas/mes en 2025 y más tape-outs que en 5 nm.

- Los primeros clientes N2 (2026–2027) serán Apple, AMD, Qualcomm y otros.

- Sub-2 nm (1,6–1,4 nm) podrían costar 45.000–50.000 $ por oblea.

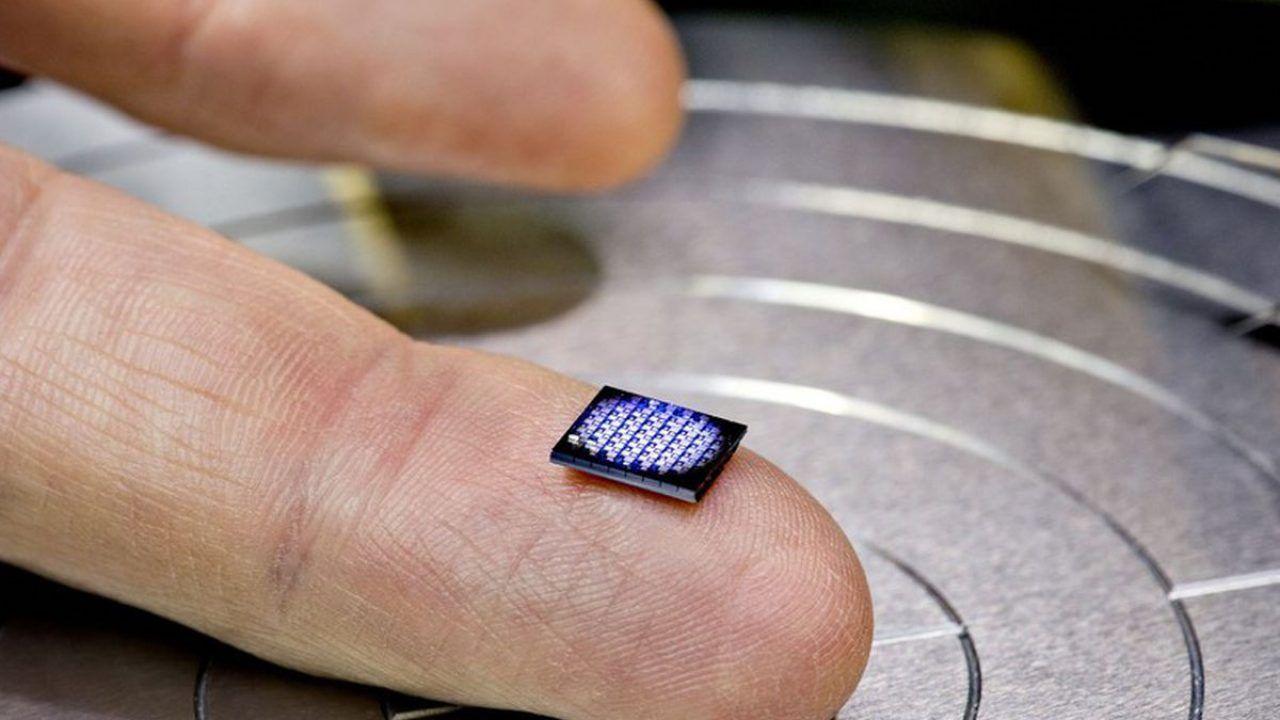

La industria de los semiconductores está entrando en un momento decisivo en el que la miniaturización extrema convive con una subida de costes sin precedentes. El salto a los 2 nm marca un antes y un después no solo por la complejidad técnica, sino porque el precio de diseñar y fabricar chips de vanguardia se ha disparado a cifras históricas.

TSMC, líder mundial en fabricación, ya ha puesto cifras a este nuevo escalón: unos 30.000 dólares por oblea a 2 nm, con proyecciones que sitúan los procesos sub-2 nm (1,6 nm y 1,4 nm) entre 45.000 y 50.000 dólares. Y aunque suene abrumador, la demanda de IA, móviles premium y centros de datos cloud empuja con fuerza, dejando claro que jugar en esta liga es cosa de gigantes.

Por qué el salto a 2 nm dispara la factura

Dar el salto a 2 nm no es simplemente «hacerlo más pequeño». Supone introducir cambios estructurales como el BSPDN (Backside Power Delivery Network), es decir, la entrega de energía por la cara posterior del transistor, además de seguir reduciendo dimensiones sin perder el equilibrio potencia/rendimiento/densidad y, a ser posible, conteniendo los costes.

La fabricación en nodos de vanguardia exige cadenas productivas con más de 2.000 pasos, márgenes de error minúsculos y una infraestructura que muy pocos operadores dominan. TSMC ha invertido miles de millones en nuevas plantas en Hsinchu y Kaohsiung, algo imprescindible para escalar capacidad y que también presiona al alza el coste por oblea.

Más allá del precio por oblea, el reto está en lograr un rendimiento (yield) suficientemente alto. La industria apunta a umbrales mínimos del 70% para la rentabilidad en 2 nm, aunque los márgenes reales solo se consolidan cuando el rendimiento se estabiliza y supera el 80%, algo que no suele ocurrir en los primeros meses de producción.

Cuánto cuesta una oblea y cuánto cuesta un diseño

TSMC ha confirmado que la oblea en N2 (2 nm) se sitúa en torno a 30.000 dólares. Para ponerlo en contexto, en 2020 una oblea de 5 nm costaba 16.988 dólares y una de 7 nm rondaba los 9.346 dólares. Dependiendo de la fuente, el diferencial entre 5 nm y 2 nm se mueve del 66% al 76%, una subida notable incluso para los estándares de vanguardia.

El futuro a menor escala pinta aún más caro: para los nodos sub-2 nm, como 1,6 nm y 1,4 nm, se han barajado cifras entre 45.000 y 50.000 dólares por oblea. A esto se suma la visión de TSMC de que el auge de la IA crecerá a un 40% anual a partir de 2024, lo que explica por qué la industria está dispuesta a pagar esta prima de acceso.

Pero la gran losa no es solo la oblea. Diseñar un chip puntero a 2 nm puede rondar los 725 millones de dólares antes de pisar producción en volumen. Esa cifra incluye IP, verificación, prototipos y validación, entre otros bloques, y refleja una barrera de entrada que encaja con la frase de un proveedor de TSMC: «aquí no se trata de correr, sino de saber más».

TSMC prevé alcanzar a finales de 2025 una capacidad cercana a 30.000 obleas al mes en 2 nm, y calcula que la adopción inicial multiplicará por cuatro los diseños tape-out frente a los primeros años de 5 nm. Si esa tracción se confirma, N2 se consolidará como la nueva frontera competitiva del silicio.

De 28 nm a 2 nm: la escalada documentada por IBS

International Business Strategies (IBS) ha cuantificado cómo han crecido los costes de diseño al avanzar de nodo. En 2010, diseñar a 28 nm costaba unos 48 millones; en 22 nm subió a 63 millones (+31,25%); y en 16 nm escaló a 90 millones (+42,85%). El gran salto llegó con 7 nm por la adopción de EUV, que elevó el coste hasta 249 millones (+76,66%) frente a 16 nm.

De ahí en adelante, el incremento siguió: a 5 nm, el diseño pasó a 449 millones (+80,32%) desde 7 nm; en 3 nm rondó los 581 millones (+29,39%) frente a 5 nm; y en 2 nm alcanza los 725 millones (+24,78%) frente a 3 nm. Si se compara 5 nm con 2 nm, la diferencia supera el 61% en apenas dos años.

IBS desglosa el esfuerzo en siete etapas clave que inflan el presupuesto de principio a fin. No es un único costo; es una cadena de actividades que se encarecen a la vez que la complejidad del nodo.

- Cualificación de IP: selección y validación de bloques reutilizables críticos.

- Arquitectura: definición de la plataforma, partición y objetivos PPA.

- Verificación: cobertura funcional y formal a nivel de sistema y bloques.

- Implementación física: floorplanning, colocación, enrutado y cierre de timing.

- Software: firmware, drivers y toolchains ajustados al silicio.

- Prototipos: emulación/FPGA y primeras corridas para depuración.

- Validación final: pruebas de silicio, caracterización y certificaciones.

A esta lista hay que añadir la economía de las herramientas. Las licencias EDA de nivel enterprise cuestan varios millones al año; algunas fuentes señalan que un desarrollo a 7 nm puede requerir más de 1.500 ingenieros y rondar los mil millones si se computa toda la I+D asociada. Fotomáscaras que en 7 nm costaban unos 15 millones siguen encareciéndose a cada nodo, y la metrología y test también se disparan.

Para compensar, los equipos están metiendo IA en el flujo de diseño: desde la disposición y cableado de SRAM, hasta la optimización lógica. Proveedores como Synopsys, Cadence y Ansys lideran esta integración de aceleradores que recortan tiempos y reducen iteraciones, conteniendo la factura total del proyecto.

Clientes que ya se mueven y quién se queda al margen

La lista de empresas que preparan su salto al nodo N2 de TSMC entre 2026 y 2027 habla por sí sola. Solo los gigantes pueden entrar en la fase inicial de este nodo y asumir los costes asociados.

- Apple: familia M6 y los A20/A20 Pro para la generación de iPhone 18.

- Qualcomm: Snapdragon 8 Elite 3.

- MediaTek: Dimensity 9600, planteado para finales de 2025.

- AMD: servidores EPYC Venice y Medusa con tape-out completado.

- Fujitsu: CPUs orientadas a IA.

- Microsoft: acelerador MAIA 300.

- AWS: Trainium 4.

- Google: TPU v8p/e.

Llama la atención la ausencia de NVIDIA en la primera ola de N2. La compañía opta por seguir con 3 nm y variantes optimizadas para Blackwell Ultra y Vera Rubin a corto plazo, a la espera de que 2 nm madure y ofrezca un mejor rendimiento por dólar.

En paralelo, algunos analistas apuntan a que NVIDIA podría adoptar 2 nm en futuras GPUs de alto rendimiento para centros de datos, mientras que el consumo general seguiría anclado a nodos como 3 nm durante más tiempo por pura economía.

TSMC, Intel y Samsung: carreras paralelas

La posición de TSMC es dominante: acumula alrededor del 60% del mercado de fabricación y llega a 2 nm tras un 2024 sólido. Apple, NVIDIA, AMD, MediaTek y Qualcomm han mostrado interés por su tecnología de integración de 2 nm, reforzando su cartera a medio plazo.

Para Samsung el punto de partida es más delicado. El grupo ha tenido que revaluar su expansión y ajustar plantilla tras un 2023 débil en ingresos, pero mantiene su hoja de ruta para iniciar producción a gran escala en 2 nm. El nodo es una oportunidad para volver a competir de tú a tú en vanguardia.

En el frente de Intel, el vicepresidente de desarrollo de tecnología, Ben Sell, anunció que 18A (aprox. 1,8 nm) alcanzó madurez para producción en 2025, con recursos reasignados desde 20A. El CFO, Dave Zinsser, explicó que se saltan 20A para ahorrar unos 500 millones de dólares, una decisión pragmática en su coyuntura actual.

En los tres casos subyace el mismo dilema: llevar el yield por oblea a niveles sanos lo antes posible. Mientras eso no ocurra, el coste por chip es demasiado volátil y la oferta, limitada, por lo que la priorización recae en IA y data centers antes que en consumo masivo.

Impacto en consumidores y mercados

Los nanómetros dejaron de ser una medida literal de distancia de puerta hace años, y hoy son nombres comerciales que reflejan una categoría tecnológica global: densidad, potencia y rendimiento. Esto dificulta comparar nodos entre fabricantes, pero no cambia lo esencial: los 2 nm serán caros.

Un ejemplo práctico: si una APU de consola fabricada en 6 nm cuesta unos 150 euros, pasar a una APU en 3 nm puede añadir 100 euros por unidad, empujando el precio final al alza. La factura del silicio es uno de los componentes más influyentes en el precio del producto final.

Es previsible que los 2 nm se vean primero en chips profesionales y en dispositivos premium, quedando la adopción masiva para una fase posterior. Al tiempo, todo indica que el precio por transistor seguirá subiendo en nodos punteros, incluso si aumenta la densidad, porque la complejidad y el equipamiento crecen más rápido que el ahorro por escalado.

De hecho, algunas fuentes subrayan que TSMC ha tenido que repercutir los costes de sus propios proveedores y de sus nuevas fábricas en el precio por oblea, reforzando la idea de que el acceso a los nodos más avanzados será cada vez más exclusivo.

Rapidus, Japón y la geopolítica del silicio

Japón quiere un sitio en la vanguardia. Rapidus ha puesto fecha y precio a su apuesta: la producción en masa de 2 nm no llegaría hasta 2027 y el coste sería aproximadamente 10 veces superior al de chips actuales de fabricantes locales. Su objetivo incluye HPC para seguridad nacional y aplicaciones civiles como robótica y vehículos autónomos.

Para hacerlo realidad, Rapidus ha solicitado alrededor de 35.000 millones de dólares para I+D, con apenas 2.000 millones de apoyo gubernamental confirmados por ahora. La financiación restante deberá venir de socios e inversores, en un contexto global donde EE. UU. y Europa también se posicionan con sus propios incentivos.

TSMC, por su parte, diversifica su huella con inversiones en Estados Unidos y Alemania para mitigar riesgos geopolíticos y distribuir mejor los costes. Pero abrir y escalar fábricas fuera de Asia implica capex adicional, adaptación normativa y una logística compleja.

A nivel de sala blanca, producir a 2 nm impone ambientes aún más estrictos: cualquier partícula invalida una oblea. Esto eleva drásticamente los costes en control ambiental, monitorización en tiempo real y metrología avanzada, y obliga a formar a una plantilla escasa y muy especializada.

En paralelo, la IA se ha convertido en una herramienta transversal para acelerar el diseño y reducir errores en etapas críticas. SRAM, colocación y enrutado ya se benefician de algoritmos específicos, y los grandes proveedores EDA consolidan suites que ahorran tiempo e iteraciones, con impacto directo en el coste total de propiedad.

Capacidad, plazos y qué esperar de 2025 a 2027

TSMC prevé producción en masa de 2 nm en la segunda mitad de 2025, con primeras integraciones comerciales a lo largo de 2026. Con una capacidad objetivo cercana a 30.000 obleas mensuales y una oleada de tape-outs que cuadruplicaría los de los primeros 5 nm, el despegue de N2 será visible en el ecosistema.

Las agendas de clientes lo reflejan: Apple (M6, A20/A20 Pro), Qualcomm (Snapdragon 8 Elite 3), MediaTek (Dimensity 9600), AMD (EPYC Venice/Medusa), Fujitsu, Microsoft (MAIA 300), AWS (Trainium 4) y Google (TPU v8p/e) aparecen como primeros candidatos entre 2026 y 2027, con ligeras variaciones posibles según el calendario de cada uno.

Mientras tanto, NVIDIA se mantiene en 3 nm para sus próximas plataformas Blackwell Ultra y Vera Rubin, una señal de prudencia habitual cuando un nodo está en fase inicial y el rendimiento por dólar todavía no compensa el salto inmediato.

Para los nodos que vendrán tras N2, el mercado ya anticipa obleas por encima de los 45.000 dólares en 1,4 nm y cifras similares en 1,6 nm. Todo sugiere que la frontera de costes seguirá subiendo con cada iteración, reforzando la concentración de la vanguardia en manos de pocos actores.

Queda claro que los 2 nm inauguran una fase en la que solo los más grandes pueden competir en el extremo más avanzado, apoyados por inversiones colosales, planificación a largo plazo y una demanda de IA que no afloja. Para el resto, la estrategia pasa por optimizar en nodos maduros, esperar a que mejore el yield y aprovechar el efecto de escala cuando el nodo empiece a estabilizarse.