Existen varios tipos de obleas semiconductoras, o wafers, una de ellas es la MPW, que es muy peculiar, ya que te podría incluso permitir obtener tu propio chip de forma más o menos barata, sin necesidad de tener que contratar servicios extremadamente caros con una foundry, y fabricando en cantidades pequeñas…

¿Qué es un wafer u oblea?

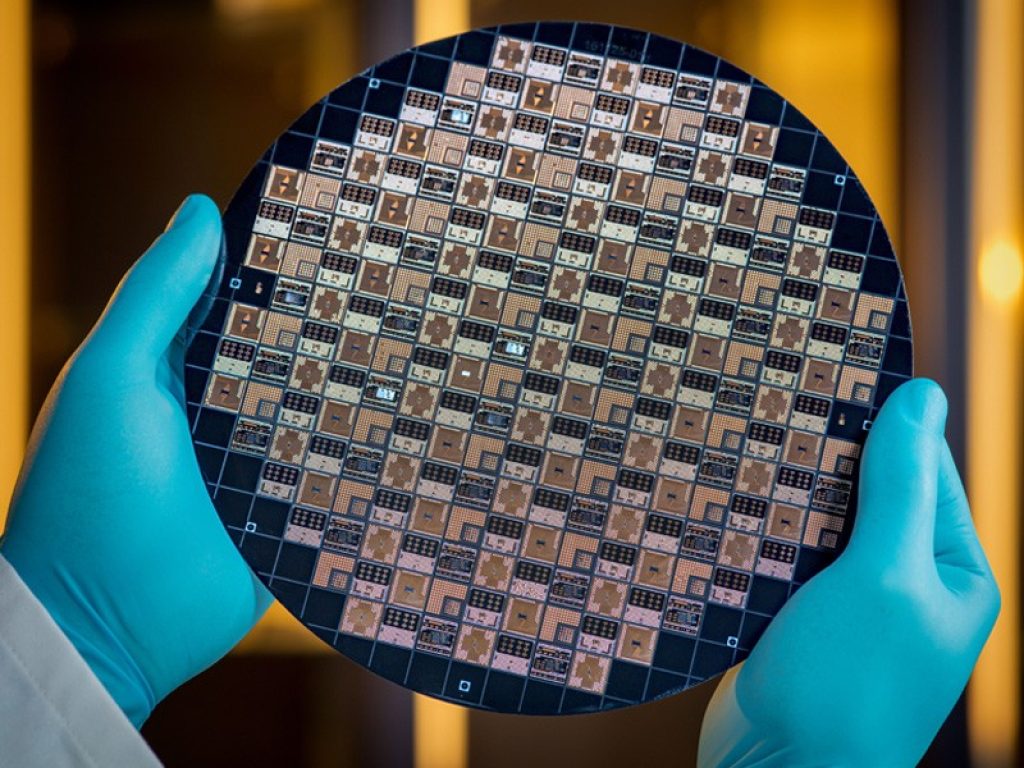

Una oblea o wafer es simplemente una delgada placa de semiconductor con forma circular. Este wafer actúa como un sustrato semiconductor para la creación de dispositivos electrónicos necesarios y las capas de interconexión sucesivas que conforman el chip o circuito integrado. Actualmente, con los nuevos 3D packaging, también puede servir de sustrato para el interposer, entre otras.

Generalmente, los wafers no se fabrican en la misma foundry donde luego se fabricarán los chips. Existen algunas compañías que proveen de este tipo de obleas, o se realizan en salas apartadas de la propia foundry.

El material más comúnmente utilizado para las obleas es el silicio (Si), un semiconductor abundante con propiedades muy adecuadas para la fabricación de chips. Sin embargo, no cualquier tipo de silicio sirve, debe ser altamente puro y tener una estructura cristalina bien definida.

Es por esta razón por la que el silicio de grado metalúrgico (MGS o Metallurgical Grade Silicon), que se utiliza en otras industrias, no se considera lo suficientemente puro para la industria de los semiconductores. Por lo tanto, se requiere un proceso de refinamiento para obtener silicio de alta pureza conocido como EGS (Electronic-Grade Silicon), que es apropiado para la creación de chips. Lo mismo ocurre con otros materiales empleados como sustratos, como puede ser el Ge, GaAs (Arseniuro de Galio), InSe (Indio Selenio), InGaN (Nitruro de Galio-Indio), etc. Se tiene que conseguir una gran pureza.

Además, el silicio debe tener una estructura cristalina monocristalina, lo que significa que los átomos están dispuestos de manera ordenada en la misma dirección. Y existen varias orientaciones para el cristal de este tipo, como puede ser la [100], [010], [111], por ejemplo. Esto se define mediante los llamados índices de Miller. Por ejemplo, los 100 son los preferidos para la industria que se dedica a realizar placas fotovoltáicas, mientras que para la industria de los semiconductores se suelen usar varias orientaciones.

Es importante destacar que, aunque el silicio pueda parecer metálico en algunos aspectos, no es un metal en el sentido convencional. Los metales tienen electrones libres que se mueven fácilmente entre los átomos, lo que les confiere buenas propiedades conductoras. En cambio, el silicio puro en su forma cristalina es casi un aislante, pero esta propiedad se puede modificar mediante un proceso de dopado.

El dopado implica la introducción de pequeñas cantidades de impurezas en el cristal de silicio para alterar sus propiedades conductivas. Dependiendo del tipo de dopaje, el semiconductor puede ser del tipo N o del tipo P. Por ejemplo, el arsénico, el antimonio y el fósforo son dopantes del tipo N para el silicio, mientras que el aluminio o el boro son del tipo P. Y según las cantidades de estos dopantes, el semiconductor puede ser extrínseco (dopado leve) o degenerado (dopado alto)…

Normalmente, la cantidad de dopante suele ser de 1 átomo de dopante por cada miles de átomos de silicio. Es decir, se agrega en cantidades ínfimas. Por ejemplo:

- Dopado leve del cristal: 1 impureza P o N por cada 1.000.000.000 a 1.000.000.000.000.000 átomos de silicio.

- Dopado alto del cristal: 1 impureza P o N por cada 1000 a 10.000 átomos de silicio.

Esto es lo que se conoce como un semiconductor N o semiconductor P, cuando es leve el dopado, o tipo N+ o P+ cuando se trata de un doping mayor, con 1 átomo de dopante por cada 1000 de silicio.

¿Cómo se fabrica un wafer?

Como se puede ver en el vídeo que he dejado, después de obtener el mineral de silicio, que suele provenir de la arena, se somete a una serie de procesos de purificación. La meta es alcanzar un nivel de pureza de aproximadamente el 99.9999999% para que el silicio sea adecuado para la producción de obleas (EGS). Una vez logrado este nivel de pureza, los fragmentos de silicio se introducen en un crisol y se funden, iniciando el proceso que ves en el vídeo superior.

Este método se denomina Float-Zone o Czochralski, gracias al que es posible crear un lingote o cilindro de silicio monocristalino de una forma barata y rápida. La creación de un cristal monocristalino directamente en el laboratorio es un proceso costoso y lento, por lo que generalmente se comienza con un cristal semilla producido en el laboratorio y se utiliza el proceso de crecimiento Czochralski para hacer crecer el cristal con la misma orientación que la semilla. En este proceso, el cristal semilla se sumerge en el crisol con silicio fundido, se le dan vueltas, se eleva y se ajustan las temperaturas.

El resultado es el crecimiento de un lingote cilíndrico de cristal monocristalino. Ese proceso puede compararse con el proceso de hacer algodón de azúcar, como lo que puedes ver en las ferias. Se introduce el palo, y mediante el giro el algodón de azúcar se va adhiriendo en capas alrededor del palo hasta aumentar el volumen. Es por eso que los wafers no son cuadrados ni de otras geometrías, solo circulares.

Una vez obtenido el lingote, pasa por una serie de etapas adicionales para obtener el wafer u oblea final en la que puedan producirse chips. Por ahora, con un enorme y pesado lingote no se puede hacer mucho. Los pasos siguientes son:

- Se permite que se enfríe totalmente tras el proceso de crecimiento, generalmente colgado mediante unas grúas.

- Se cortan las puntas, ya que tienen formas de cono, y esto no sirve para la fabricación de obleas uniformes.

- Se utiliza una sierra para dividir el lingote resultante de cortar las puntas en obleas delgadas, que tendrán el diámetro requerido.

- Las obleas se someten a un proceso de pulido para lograr una superficie perfectamente plana que servirá como base para la fabricación de los chips.

- Además, se someten a procesos de limpieza para eliminar partículas no deseadas y asegurar la pureza del material.

Una vez la oblea ha pasado todos estos pasos, puede ser llevada a la foundry para fabricar los chips o dispositivos MEMS, etc. Esta oblea, antes de realizar el proceso de fabricación, será una oblea virgen.

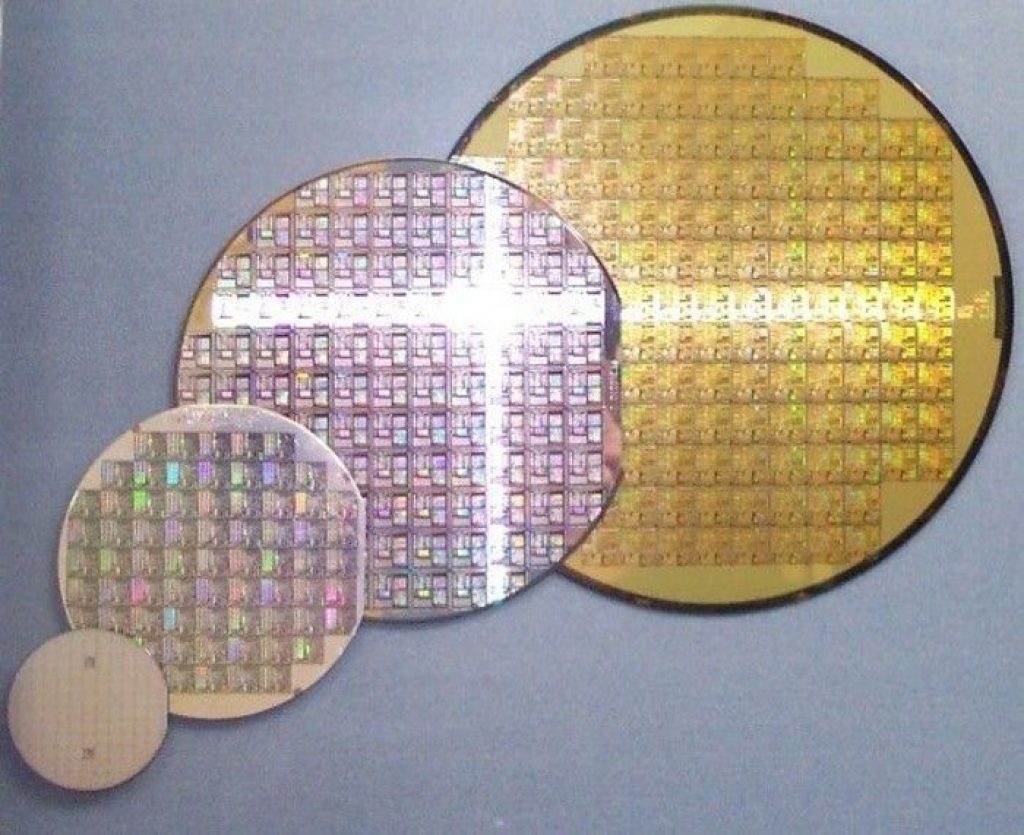

Tamaños de las obleas semiconductoras

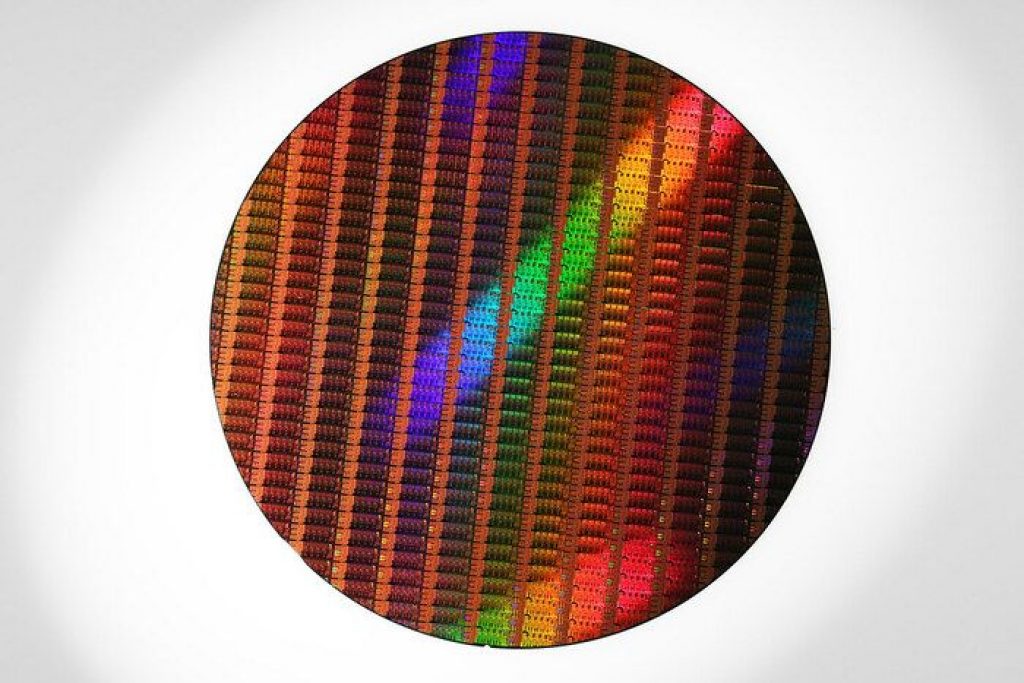

A lo largo de la historia, se han utilizado diferentes tamaños de obleas, desde las más pequeñas hasta las más grandes en la actualidad. Esto es debido al avance de la tecnología y de las máquinas de crecimiento, que actualmente son bastante descomunales y admiten generar lingotes muy largos, pesados y de diámetros muy grandes.

En la actualidad, las fábricas de vanguardia emplean obleas de 300 mm de diámetro, que equivalen a 11.8 pulgadas, aunque a menudo se redondea y se denominan obleas de 12 pulgadas. En el pasado, se propuso el uso de obleas de 450 mm, pero esta opción no se ha adoptado debido a que las ventajas no son lo suficientemente significativas en comparación con las obleas de 300 mm como para justificar el costo de adaptar toda la maquinaria a este diámetro.

También hay que decir, que algunos de estos tamaños no han sido desechados por completo, por ejemplo, todavía puede haber foundries o fábricas de chips que usen obleas de 200 mm, con nodos de fabricación o procesos que podrían parecer obsoletos para chips como las CPUs o GPUs, pero que siguen siendo suficientes para otras aplicaciones, como los chips de los coches, chips más simples, etc. Por ejemplo, podemos ver fábricas aún de 130 nm, 65 nm, 40 nm, etc.

| Diámetro de la oblea en milímetros (y pulgadas) | Grosor de la oblea en micrones | Año de uso | Peso en gramos de una oblea | Chips por oblea (si son de 100mm2) |

|---|---|---|---|---|

| 25 mm (1”) | 1960 | |||

| 51 mm (2”) | 275 μm | 1969 | 9 | |

| 76 mm (3”) | 375 μm | 1972 | 29 | |

| 100 mm (4”) | 525 μm | 1976 | 10 g | 56 |

| 125 mm (4.9”) | 625 μm | 1981 | 95 | |

| 150 mm (6″) | 675 μm | 1983 | 144 | |

| 200 mm (8″) | 725 μm | 1992 | 53 g | 269 |

| 300 mm (12″) | 775 μm | 1999 | 125 g | 640 |

| 450 mm (17.7”) (propuesto) | 925 μm | – | 342 g | 1490 |

| 675 mm (26.6”) (teórico) | Desconocido | – | Desconocido | 3427 |

En la última columna se indica la cantidad aproximada de chips que se pueden producir en una oblea de ese tamaño, considerando que el chip tiene un área de 100 mm cuadrados. Sin embargo, es importante mencionar que 100 mm² es un valor pequeño para los chips más avanzados, como las CPU o GPU. Por ejemplo, la NVIDIA GeForce RTX 4090 tiene un tamaño de 608 mm², y un procesador Intel Core de 13ª Generación alcanza los 257 mm². Por lo tanto, en el caso de las CPUs, se estima que se pueden producir alrededor de 300 chips por oblea, mientras que en el caso de las GPUs, considerando este tamaño, la cantidad sería de aproximadamente 100 unidades por oblea.

Partes de un wafer

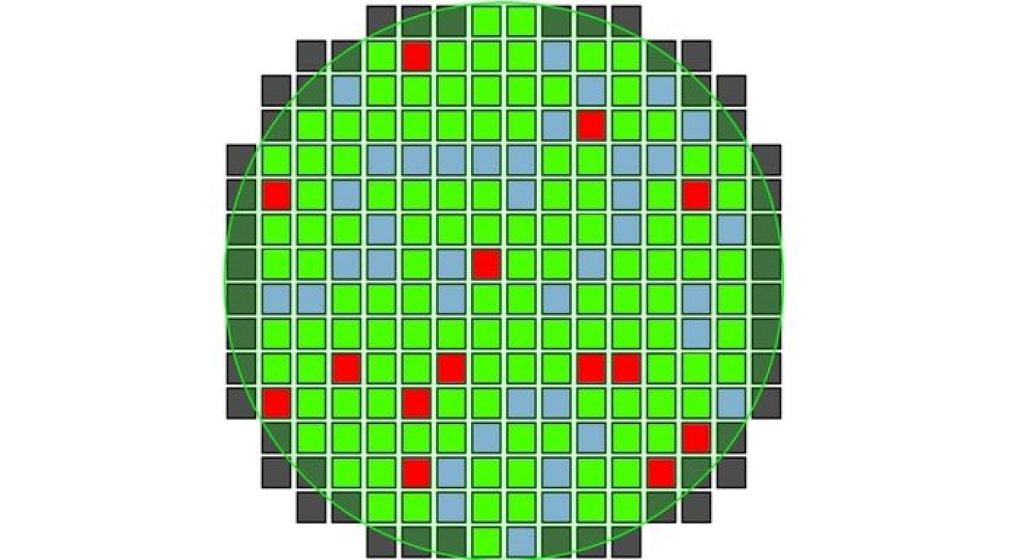

Un wafer, cuando sale virgen de los primeros procesos de creación, no tiene partes específicas, pero cuando entra en la foundry y comienza su «parcelación» para fabricar cada die o chip, entonces se pueden distinguir entre:

- Chips del borde (Edge Die): estos chips no están completamente desarrollados y se encuentran en el borde de la oblea, por lo que parte podría estar fuera. Se consideran pérdidas en la producción. Cuanto más grande sea la oblea, menor será la pérdida debida a este problema. En la anterior imagen los puedes ver marcados en gris oscuro.

- Líneas de Marcado (Scribe Lines): son líneas de separación que se encuentran entre los diferentes chips en la oblea. Estas áreas se utilizan para realizar cortes con una sierra u otro método de separación de chips, evitando dañar partes funcionales. Se pueden ver en la anterior imagen como líneas blancas que separan los distintos chips producidos.

- Chip o Dado (Die): también conocido como troquel, se refiere al propio circuito integrado contenido en la oblea. Serían todos los que ves en verde, gris claro y rojo. No obstante, hay que decir que debido al yield, no todos serán servibles al 100%. Por ejemplo, los grises pueden ser parcialmente funcionales, los rojos no funcionan en absoluto, y los verdes sí que se pueden vender. Por tanto, habrá que aplicar técnicas conocidas como binning.

- Zona Plana o Chaflán (Flat Zone): algunas obleas tienen un borde plano o chaflán. Anteriormente, este corte se utilizaba para determinar la orientación de la estructura cristalina del silicio en la oblea. Sin embargo, en la actualidad, este enfoque rara vez se utiliza, simplemente se identifica la orientación del lote de obleas, y se evitan cortes que puedan dar como resultado rendimientos inferiores o posibles roturas de la oblea.

- TEG (Grupo de Elementos de Prueba): estos son circuitos integrados diferentes a los que se pretenden fabricar en la oblea y suelen estar distribuidos en varias unidades a lo largo de la superficie de la misma. Estos chips se utilizan para llevar a cabo pruebas y verificar que todo funcione correctamente. Sin embargo, posteriormente se descartan y solo se conservan los demás chips funcionales.

Tipos de obleas

Si atendemos a los tipos de wafers u obleas vírgenes que existen, nos podemos topar con varios tipos principales, como:

- Sin dopar (intrínsecas): son obleas fabricadas con procesos como FZ o Float-Zone, y que no contienen dopantes, es decir, son del material semiconductor base.

- Dopadas: son obleas en las que se ha introducido impurezas o dopantes, como indicamos anteriormente. Se agrega el dopante a la mezcla en el crisol, junto con el Silicio fundido. De este modo se consiguen obleas con sustrato P o N. Las de tipo P tienen huecos cargados positivamente en exceso, y las de tipo N tienen electrones cargados negativamente en exceso. Y, como he mencionado anteriormente, según la cantidad de dopantes, puede ser degenerado o extrínseco.

- Otros tipos: también hay casos especiales de obleas SOI (Silicon On Insulator) como las PD-SOI y FD-SOI, SON (Silicon On Nothing), etc. Estas suelen usarse para casos más específicos donde sea necesario estas mejoras. Por ejemplo, IBM y AMD han sido dos históricos que han usado la tecnología SOI para sus chips, entre otros.

Usos de un wafer

Por otro lado, también hay que conocer los usos de estas obleas o wafers vírgenes, y que, como ya hemos adelantado, entre otras cosas, sirven para:

- Se pueden usar las obleas vírgenes para investigación en laboratorios o para mostrar en sectores educativos.

- Se utiliza en la fabricación de dispositivos semiconductores, que incluyen transistores, diodos, sensores y otros componentes cruciales.

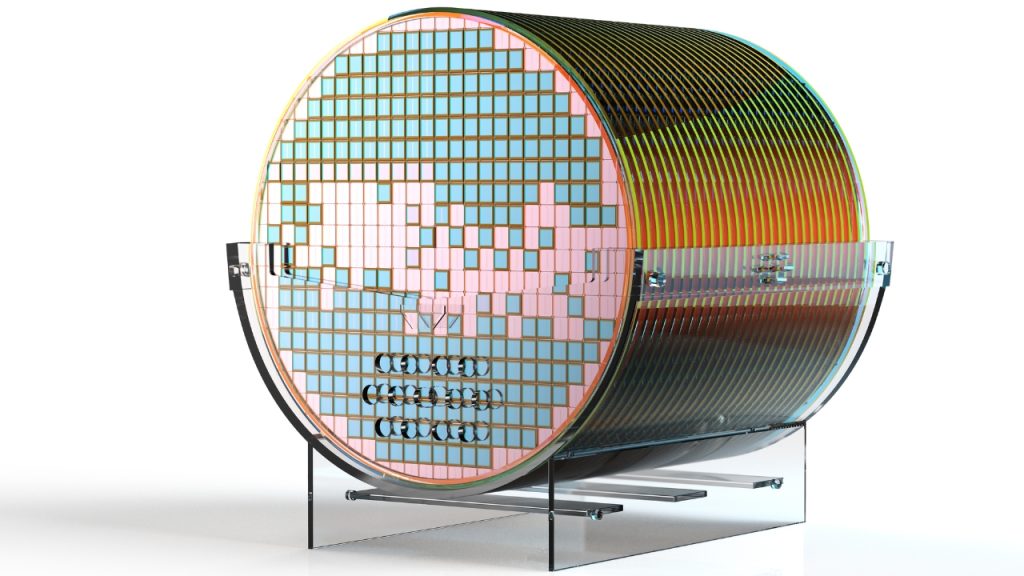

- Se emplea en la creación de chips utilizados en aparatos de electrónica. En algunos casos, como el de los SoW/WSI, como Cerebras, puede contener un solo chips por oblea, ya que es de un tamaño descomunal.

- También se utiliza en la fabricación de elementos ópticos y optoelectrónicos, como láseres, LEDs, sensores de imagen IR y CIS, entre otros.

- Es esencial en la producción de sistemas microelectromecánicos (MEMS), que son dispositivos pequeños y precisos utilizados en diversas aplicaciones.

- Contribuye a la fabricación de células solares para paneles solares, incluyendo células de silicio amorfo, monocristalino, telururo de cadmio, perovskita, y más.

- Se emplea en la fabricación de materiales de recubrimiento especiales utilizados en la industria aeroespacial y otros campos de alta tecnología.

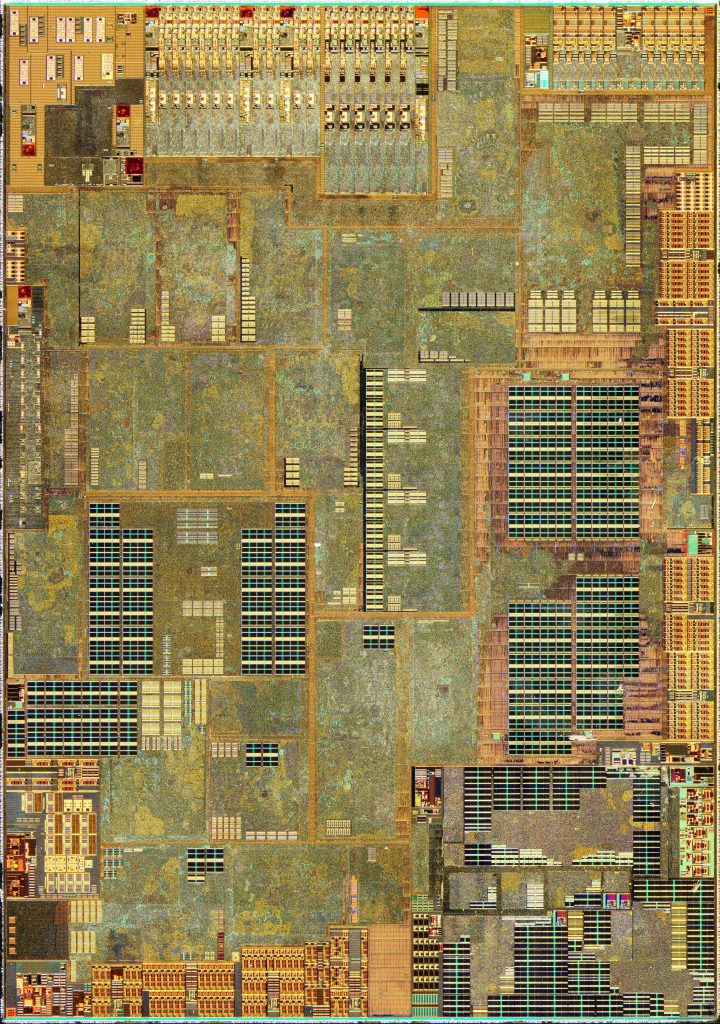

Cómo se fabrica un chip

Como se puede apreciar en el vídeo, los chips se fabrican en masa en cada oblea, y luego se produce un proceso para separarlos, empaquetarlos y testarlos. La verdad es que es bastante complejo, pero en este vídeo puedes conocer algunos detalles para hacerte una idea más clara.

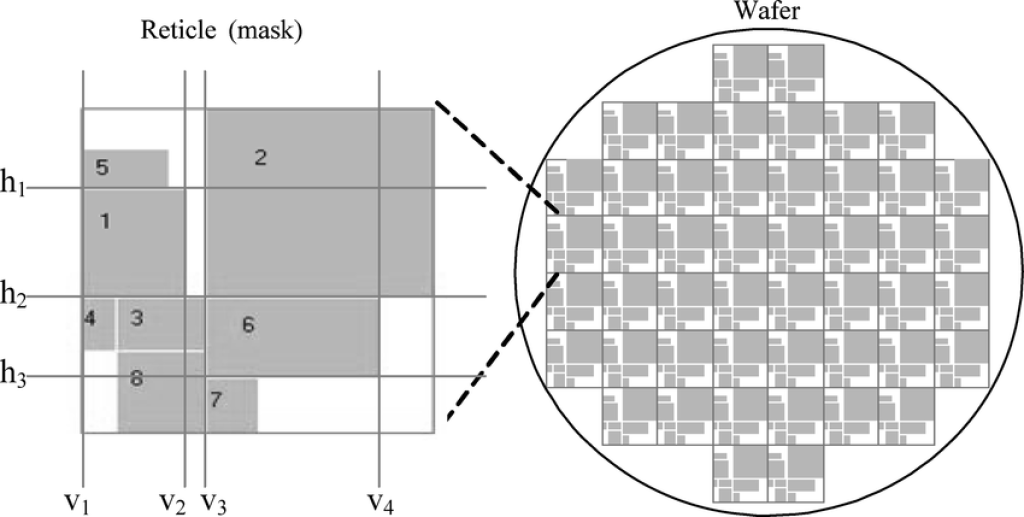

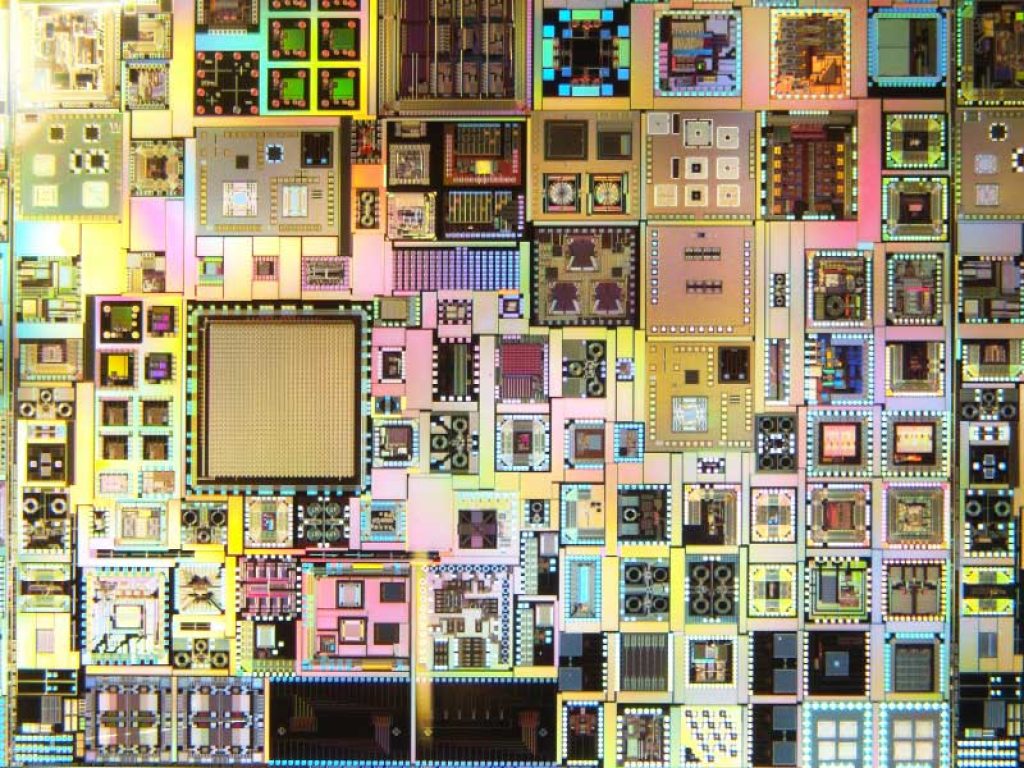

¿Qué es MPW?

Debes saber, que es el tema principal de este artículo, que existen unas obleas denominadas MPW (Multi-Project Wafer). Como su nombre indica, no se usan para fabricar un solo chip idéntico, y replicado decenas o cientos de veces, como es habitual. Por ejemplo, cuando Intel fabrica sus Core, por cada oblea puede producir unos 100 de estos chips idénticos..

En un MPW eso no es así, sino que se fabrican multitud de chips diferentes unos de otros. Por tanto, podría haber más de un centenar de chips, pero pertenecen a distintos diseñadores. De esta forma, se aprovecha el wafer para producir chips para instituciones que no quieren fabricar en masa, para universidades, para aquellos que no cuentan con una foundry y necesitan implementar un chip físico, etc.

Por tanto, es un método de lo más práctico para fabricar tu propio chip y que te lo envíen a casa, sí, así es… No obstante, algunos de estas industrias o servicios MPW, no incluyen en el precio la prueba de chips, así que te darán unas muestras y si funcionan o no es cosa tuya.

Seguramente sabías que existían modelos IDM (Integrated Design and Manufacturer), como puede ser Intel y Samsung, que diseñan y fabrican sus propios chips. Además de empresas fabless sin fábricas que solo diseñan, como NVIDIA, AMD, Apple, Qualcomm, Mediatek, Arm, etc. Y, por último, los servicios de fundición o foundries, que solo fabrican los chips de clientes fabless. Ahora ya sabes que hay algo más: el MPW.

Ventajas y desventajas del MPW

Como suele ser habitual con todo, el MPW tiene sus ventajas y desventajas. Entre las ventajass tenemos que destacar:

- Coste compartido: una de las principales ventajas de MPW es la reducción de costes. Los clientes comparten los gastos de fabricación de la oblea, lo que hace que sea más asequible para proyectos con presupuestos limitados.

- Acceso a tecnologías avanzadas: MPW a menudo ofrece acceso a tecnologías de fabricación avanzadas que pueden ser costosas si se realizan en proyectos individuales. Esto permite a las empresas más pequeñas y startups aprovechar las últimas innovaciones, o que incluso lo hagan estudiantes, universidades, y particulares.

Por otro lado, también hay desventajas:

- Menos control: en un MPW, no tienes el control total sobre la oblea. Los tiempos de fabricación y prioridades pueden estar sujetos a las necesidades de otros participantes. Muchas veces ni siquiera se incluye proceso de testaje de los chips fabricados, por lo que no sabes si las unidades que te llegan son todas funcionales.

- Confidencialidad: dado que múltiples proyectos están en la misma oblea, existe el riesgo de que los diseños de otros participantes puedan ser vulnerables a la ingeniería inversa o la filtración de información confidencial.

- Limitaciones en el diseño: debes adaptar tu diseño a las reglas y restricciones de fabricación del proceso MPW, lo que podría limitar ciertas características o diseños personalizados. Es decir, hay menor flexibilidad.

- Competencia por los recursos: puede haber competencia por recursos limitados, como tiempo de fabricación y capacidad de obleas, lo que puede afectar los plazos de entrega.

Diseño para MPW

Como se aprecia en el vídeo anterior, para fabricar un chip se necesita un proceso que conta de varias etapas, y se necesitan herramientas de software como los entornos EDA, entre otros programas. Además, existen PDKs (Process Design Kit), como por ejemplo Skywater PDK con herramientas de código abierto y para nodos de 130 nm.

Para que lo comprendas, el PDK es un conjunto de archivos utilizados en la industria de semiconductores para modelar un proceso de fabricación destinado a las herramientas de diseño utilizadas en la creación de un circuito integrado. El PDK es creado por la fundición que define una variación tecnológica específica para sus procesos. Luego se proporciona a sus clientes para su uso en el proceso de diseño. Los clientes pueden mejorar el PDK, adaptándolo a sus estilos de diseño y mercados específicos.

Los diseñadores utilizan el PDK para diseñar, simular, dibujar y verificar el diseño antes de entregarlo a la foundry para producir los chips. Los datos en el PDK son específicos para un nodo o proceso particular, por ejemplo, el PDK Skywater es para 130nm, y no valdría para otros nodos. Para eso, hay que usar el PDK adecuado para cada nodo.

Para que este proceso sea posible, generalmente, los PDKs incluyen:

- Biblioteca con primitivas:

- Símbolos

- Parámetros de dispositivos

- PCells (parameterized cell)

- Herramientas para verificación:

- Comprobación de reglas de diseño

- Layout vs Schematic

- Comprobación de reglas de antena y eléctricas

- Extracción física

- Datos de la tecnología:

- Layers o capas, nombres de capas, etc.

- Colores, atributos, etc.

- Restricciones del proceso.

- Reglas eléctricas

- Archivos de reglas:

- LEF (Library Echange Format), para representar el layout físico en un formato ASCII.

- Formatos de reglas dependientes de la herramienta.

- Simulación de componentes integrados, como por ejemplo SPICE o similares.

- Manual

- Requisitos de las reglas para el nodo o proceso

Además, un PDK también debería incluir bibliotecas de células estándar empleadas por la Foundry, por el propio proveedor de la biblioteca, o desarrolladas internamente por la compañía diseñadora o fabless. Estos deben estar en LEF, símbolos, archivos .lib, y datos del layout GDSII, que será el que sea entregado a la foundry para que fabriquen dicho chip…

Foundries MPW

Para finalizar, si estás interesado en conocer algunas industrias o fundiciones que se dediquen a crear MPW, y las cuales admiten contratar sus servicios para fabricar chips sin necesidad de hacerlo en masa, aquí te muestro algunas destacadas:

- Global Foundries (GF), ex fábricas de AMD.

- IHP, con todos los nodos disponibles.

- TSMC para 65nm, 40nm, 28nm y 16nm.

- UMC para procesos UMC L180, L110 y L65.

- X-FAB para nodos XH018 y XT018.

- SMIC.

- Smart Photonics para dispositivos de fotónica.

- AIM Photonics para fotónica.

- Skywater, con herramientas de código abierto para 130nm.

- Tower Semiconductor.

- ADVMF.

- Lionix International, para fotónica y MEMS.

- GSME.

Algunas de estas foundries están en Europa, y seguramente actualicen los procesos en un futuro. Ten en cuenta que los nodos más punteros están reservados para la fabricación en masa de las grandes compañías, y son extremadamente caros. Por eso se usan nodos más obsoletos…