- La 3D NAND escala densidad apilando celdas y sumando bits por celda con SLC→MLC→TLC→QLC (y PLC en el horizonte).

- Sus ventajas (capacidad, menor latencia interna y eficiencia) compensan la mayor complejidad y coste de fabricación.

- Las hojas de ruta proyectan cientos y hasta 1000 capas y más I/O, con visiones distintas entre fabricantes.

- El controlador y el firmware son decisivos para rendimiento, resistencia y coste total en cada caso de uso.

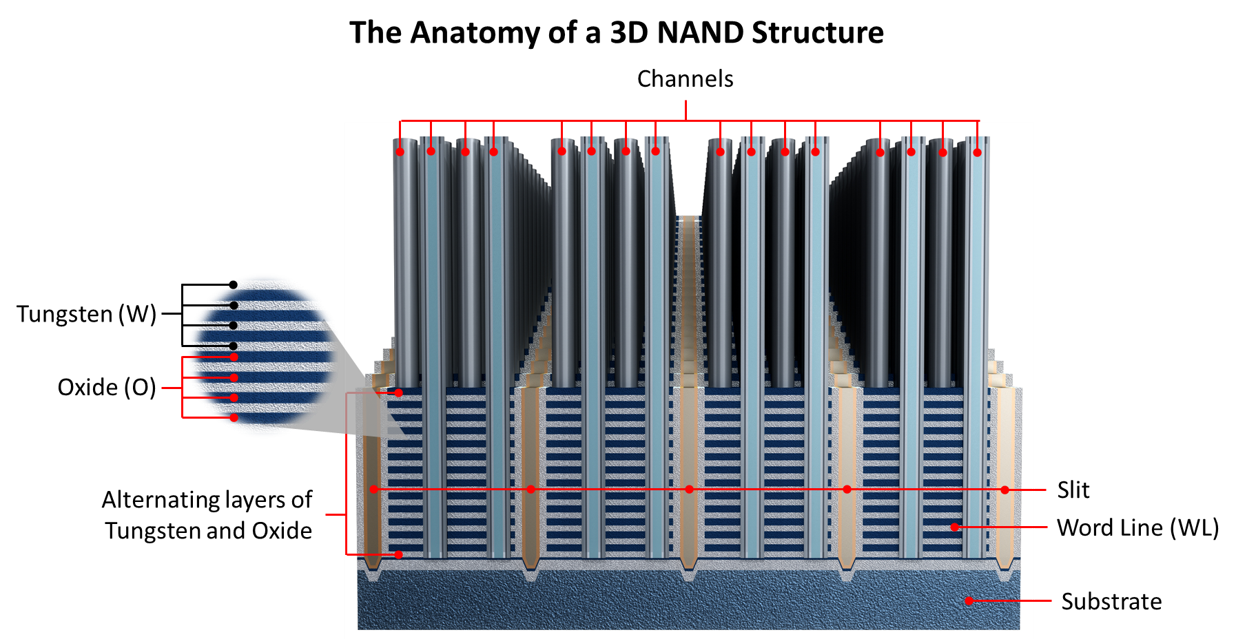

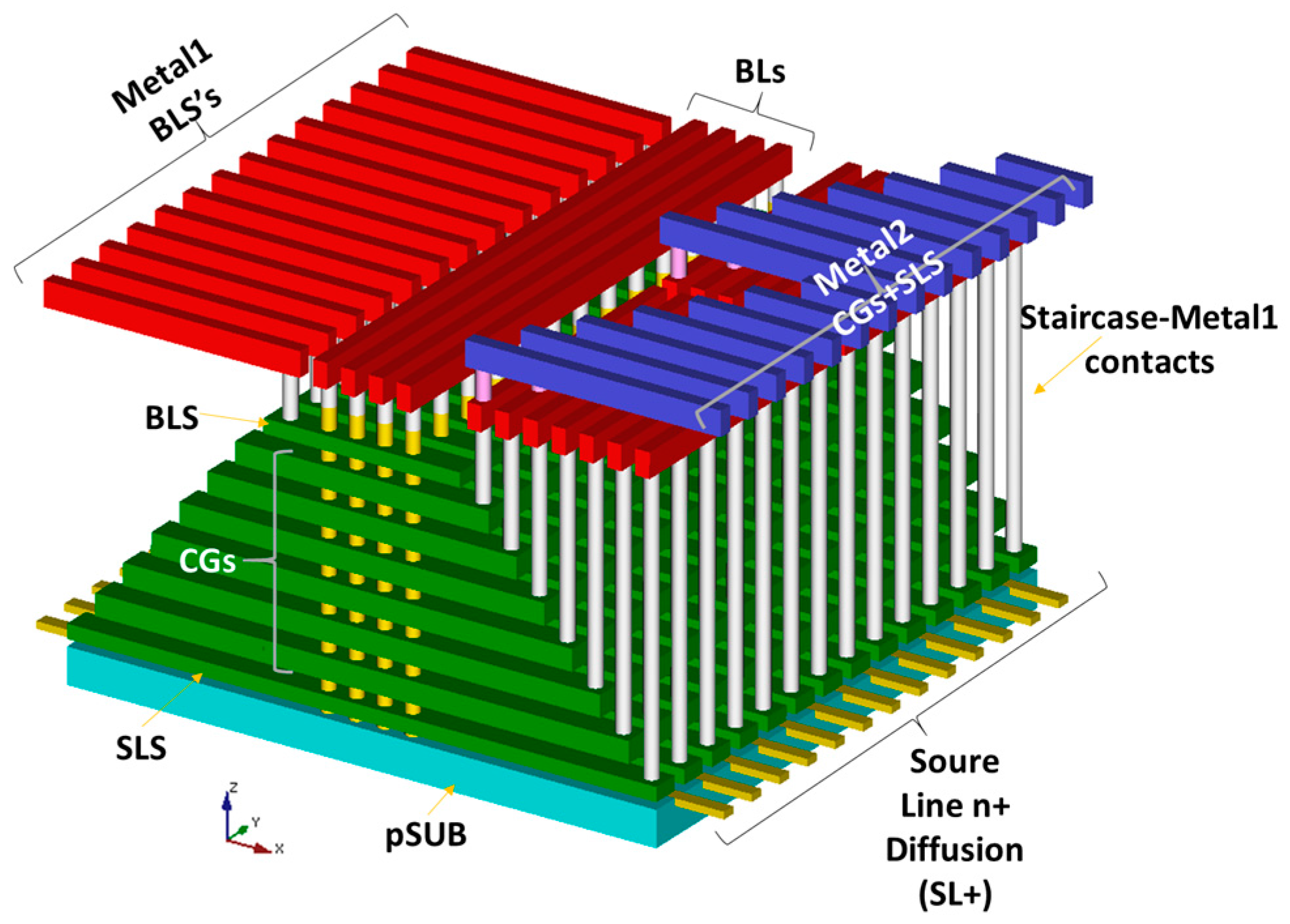

La memoria 3D NAND se ha convertido en el eje del almacenamiento moderno, desde los SSD de consumo hasta las cabinas empresariales. Su truco consiste en apilar celdas verticalmente para incrementar la densidad sin sacrificar estabilidad, algo que el diseño plano ya no podía ofrecer por límites físicos y de interferencias. Esta idea de “subir plantas” en lugar de “ensanchar la parcela” ha sido la llave para escalar capacidades y reducir el coste por byte.

En la conversación actual aparecen dos cifras que llaman la atención: “capas 500” y velocidades de “4800 MT/s”. Aunque los datos públicos más concretos del sector hablan de hojas de ruta ambiciosas hacia cientos y hasta 1000 capas y de mejoras constantes en el I/O por chip, lo relevante es entender qué hace posible estos saltos, qué compromisos implican y cómo afectan a rendimiento, coste y fiabilidad. Con ese enfoque, vamos a desglosar a fondo qué es la 3D NAND, cómo funciona, por qué escala, qué ventajas/inconvenientes presenta y qué dibuja el mapa competitivo de aquí en adelante.

Inconvenientes y compromisos

No todo es gratis: levantar estructuras 3D incrementa la complejidad de fabricación. Los procesos requieren más etapas, más control de contaminación y más precisión en grabado y deposición; un desliz en cualquiera de ellas puede arruinar el rendimiento del lote y encarecer el troquel. Aun con ese sobrecoste, la densidad extra hace que el coste por byte baje de forma neta a medida que madura cada generación.

Además, elevar bits por celda implica gestionar ventanas de voltaje estrechas. La electrónica de control tiene que trabajar más y mejor: más calibraciones, más ECC, más gestión térmica y de desgaste, y estrategias de firmware como wear leveling, SLC caching o read disturb management. Esa orquesta invisible es la que marca la experiencia real que percibe el usuario.

Fiabilidad frente a 2D NAND y arquitecturas híbridas

En términos generales, una implementación moderna de 3D NAND ofrece mejor rendimiento, eficiencia y resistencia que la 2D NAND clásica. También existen arquitecturas que apilan “capas” de 2D MLC en configuraciones especiales que pueden competir en ciertos casos, de modo que conviene evaluar el sistema completo y no solo la etiqueta del chip. La fiabilidad final depende del binning de memoria, del controlador y del software que gobierna todo.

Coste: cómo se abarata cada gigabyte

El coste de una oblea se relaciona principalmente con su área, no con “lo que hay dentro”, por lo que el coste por byte depende de cuántos bits quepan en cada chip. Para abaratar se combinan tres palancas: shrink del proceso hasta donde compense, más bits por celda (SLC→MLC→TLC→QLC, y exploración de PLC) y, sobre todo, crecimiento en vertical con 3D NAND. La clave es el equilibrio entre rendimiento, fiabilidad y coste total de propiedad.

El “shrink” puro chocó con límites: al reducir demasiado, aumentan las corrientes de fuga y las tasas de error, y se encarece el control de variabilidad. La 3D NAND permitió mantener nodos más cómodos, con celdas menos extremas, apoyándose en el apilado para multiplicar densidad y amortiguar problemas eléctricos. Es uno de los motivos por los que el salto a 3D supuso un antes y un después.

Rendimiento, latencia y el papel del controlador

A igual generación, la 3D NAND beneficia la latencia interna al acortar trayectos y optimizar la topología. Sin embargo, la velocidad que ve el usuario depende tanto o más del controlador: su arquitectura, colas de E/S, cachés, algoritmos de programación, ECC y gestión de energía. Un buen controlador “saca petróleo” de memorias más densas, y uno mediocre puede hacer lo contrario.

Algunos fabricantes destacan controladores de bajo consumo y alto rendimiento para maximizar las ventajas de 3D NAND. Por ejemplo, hay unidades como la KingSpec NE2280 que presumen de controladores de potencia ultrabaja, lo que ayuda a reducir calor y a sostener velocidades en cargas reales. Más allá de nombres concretos, lo importante es la calidad de la implementación: firmware maduro, buen mapeo lógico y políticas de escritura inteligentes.

Aplicaciones: del portátil a la hiperescala

La combinación de alta densidad, eficiencia y latencias contenidas ha abierto la puerta a usos muy variados. Desde ordenadores compactos de alto rendimiento y automoción conectada hasta cloud y despliegues a hiperescala, la 3D NAND aporta el balance de velocidad/coste/fiabilidad que necesitan estas cargas. Su versatilidad explica el auge de los SSD frente a los discos mecánicos en casi todos los segmentos.

Hojas de ruta: más capas y más bits por celda

En el frente competitivo, los fabricantes de memorias proyectan incrementos sustanciales de densidad año a año. Una de las rutas públicas más agresivas habla de llegar en torno a las 1000 capas en el horizonte cercano con una progresión media aproximada de 1,33× anual, además de migrar de TLC a QLC y explorar PLC (5 bits por celda). Este plan busca mantener el descenso del coste/GB y ampliar capacidades sin disparar el área por chip.

No todos los socios de la industria comparten el mismo ritmo. En colaboraciones como la de Kioxia con Western Digital se han expuesto visiones distintas: WD remarca el alto capex y que la caída de costes va más lenta de lo que sugiere el simple aumento de capas, abogando por una rampa más pausada. Kioxia, por su parte, empuja por densidad para disputar liderazgo a Samsung en NAND, acelerando el desarrollo de generaciones con más apilado.

Capas “500” y velocidades “4800 MT/s” en contexto

El interés por hitos como “500 capas” o cifras de “4800 MT/s” refleja dónde aspira a estar la industria en rendimiento y densidad. De cara a nuevas generaciones, elevar capas es el camino natural, y el aumento de la velocidad de I/O por chip (expresada en MT/s o Gb/s según interfaz) también progresa gracias a mejoras de señal, controladores más rápidos y buses más eficientes. Conviene recordar que la experiencia real del SSD depende tanto del flash como del controlador, el protocolo y la controladora host.

Cuando se alcanzan grandes saltos de densidad, los fabricantes ajustan el equilibrio entre ventanas de voltaje, esquemas de ECC y paralelismo interno. Si se materializan hitos intermedios (por ejemplo, entornos de varias centenas de capas antes de llegar a cuatro cifras), será clave acompañarlos con controladores y firmwares capaces de sostener altas tasas de transferencia de forma sostenida. Las métricas de MT/s de la interfaz del chip son una parte de la ecuación; la otra es cómo se agregan canales y dies dentro de la unidad.

Cómo capitalizan los proveedores de almacenamiento empresarial

Los grandes fabricantes de sistemas han construido catálogos completos sobre 3D NAND para distintas necesidades. Hay cabinas all-flash de alto rendimiento basadas en TLC para cargas Tier 0/1 (como FlashArray//X), soluciones optimizadas a capacidad apoyadas en QLC con coste por TB muy ajustado (como FlashArray//C) y plataformas escalables de archivos y objetos (como FlashBlade). La elección de TLC/QLC, firmware y topología interna condiciona IOPS, latencia y durabilidad percibida.

La moraleja para el comprador es clara: no basta con mirar el tipo de flash. Lo determinante es el conjunto: arquitectura, controladores, software de datos y servicios que rodean a la cabina o al SSD; de ahí que soluciones con QLC bien diseñadas compitan de tú a tú con sistemas híbridos o incluso con algunos TLC en TCO. Y este razonamiento se traslada igual al mercado de consumo, donde el modelo concreto del controlador y su firmware marcan diferencias.

Ventanas de oportunidad y límites prácticos

A nivel de ingeniería, cada nueva “generación de capas” abre margen de densidad, pero también aumenta la sensibilidad a variaciones y exige mejores técnicas de corrección de errores. El éxito comercial depende de equilibrar inversión (capex), rendimiento de fabricación (yield) y demanda de mercado, por eso hay fabricantes que prefieren ir más rápido y otros que ajustan el paso para mantener costes bajo control. La tecnología se estabiliza cuando los precios reflejan esa madurez y la producción está optimizada.

También veremos más diversidad en bits por celda según uso. SLC o pseudo‑SLC seguirán siendo útiles como caché o para cargas de ultra-baja latencia, TLC como caballo de batalla generalista y QLC/PLC donde prime capacidad y lectura intensiva, con controladores cada vez más listos para compensar los puntos flojos de las celdas más densas. Esa segmentación permitirá ajustar producto a caso de uso y presupuesto.