- Relación núcleo: Tiempo = (NI × CPI)/f y Performance = (f × IPC)/NI, con IPC/CPI como palancas clave.

- Escalabilidad real: Amdahl y Gustafson delimitan el speed-up; la eficiencia cae si crece el overhead.

- Memoria manda: hit/miss, DDR y ancho de banda afectan el CPI tanto como la frecuencia.

- Método WPA: ruta crítica, hilos (Ready/Running/Waiting), DPC/ISR y prioridades explican los cuellos.

Cuando buscas todas las fórmulas para calcular el rendimiento de una CPU, lo ideal es tenerlas bien explicadas, con contexto y casos prácticos, no solo un listado suelto de ecuaciones. Esta guía reúne y reescribe de forma clara y amplia las métricas, fórmulas, matices y técnicas de análisis profesional (incluyendo el uso de Windows Performance Analyzer) que suelen aparecer dispersas en muchas fuentes.

Aquí vas a encontrar desde las unidades clásicas (IPS, IPC, CPI y FLOPS) hasta la relación exacta entre tiempo de ejecución y rendimiento, las leyes de Amdahl y Gustafson, memoria y ancho de banda, e incluso cómo estudiar interferencias de hilos y DPC/ISR con WPA. Además, se incluye el cálculo de consumo energético de la CPU (C·V²·F), herramientas para medirlo y recomendaciones para mejorar eficiencia y rendimiento de forma práctica.

Unidades y métricas básicas: IPS, IPC, CPI, FLOPS y frecuencia

Lo primero es tener en cuenta cuáles son las unidades más esenciales que vamos a manejar:

- IPS (Instrucciones por segundo) mide cuántas instrucciones ejecuta el procesador en un segundo (habitualmente se usa MIPS, millones de IPS). Es una métrica útil para tener una idea global del throughput, aunque no capta bien complejidad de instrucciones ni diferencias de microarquitectura. Ejemplos históricos y modernos muestran la brecha entre diseños y épocas, y con overclock puede variar.

- IPC (Instrucciones por ciclo) indica cuántas instrucciones de media realiza la CPU por cada ciclo de reloj. Es clave para entender la eficiencia por ciclo independientemente de la frecuencia. Comparar IPC exige usar el mismo programa o benchmark en máquinas distintas, porque el recuento y el tipo de instrucciones dependen del software.

- CPI (Ciclos por instrucción) es la inversa conceptual del IPC: cuántos ciclos tarda en promedio cada instrucción. El CPI cambia según el tipo de instrucción y la microarquitectura (por ejemplo, un load puede requerir más ciclos que un jump), así que se suele calcular como media ponderada por clases de instrucciones.

- FLOPS (Operaciones en coma flotante por segundo) cuantifica el cálculo en punto flotante, crítico en HPC, IA y ciencia. Se distingue precisión simple (SP) y doble (DP) y se habla también de eficiencia energética como FLOPS/W. Conviene diferenciar FLOPS nativos de FLOPS normalizados cuando se comparan plataformas heterogéneas.

- Frecuencia (Hz) marca el ritmo del reloj, pero no es sinónimo directo de rendimiento. El mito de los MHz: hoy una CPU con menos frecuencia puede superar a otra más rápida por paralelismo, mejor IPC y microarquitecturas más eficientes. Además, la profundidad del pipeline y la lógica crítica condicionan la frecuencia alcanzable.

Fórmulas esenciales: tiempo de ejecución, rendimiento, IPC, CPI, IPS y FLOPS

Algunas fórmulas esenciales para calcular/medir el rendimiento de un procesador que debes conocer son:

- Tiempo de ejecución: una forma estándar de expresarlo es Tiempo = NI × CPI × T, donde NI es el número de instrucciones del programa, CPI el promedio de ciclos por instrucción y T el periodo de reloj (T = 1/frecuencia). Equivalente: Tiempo = (NI × CPI) / Frecuencia. Hardware y compilador suelen atacar CPI y frecuencia; NI depende del software.

- Rendimiento es la inversa del tiempo: Performance = 1 / Tiempo. Reescribiendo, Performance = (Frecuencia × IPC) / NI. Esto deja claro el triángulo de compromisos: subir frecuencia e IPC y/o bajar NI (mejor algoritmo, mejor compilación) eleva el rendimiento.

- Tiempo de CPU en sistemas con varios procesadores se expresa sumando tiempos de hilos o usando agregaciones que contemplan P procesadores. En paralelo, la porción realmente paralelizable y el overhead de coordinación limitan el beneficio (ver Ley de Amdahl y de Gustafson más abajo).

- IPC efectivo para un programa concreto se obtiene del promedio real de instrucciones por ciclo observado durante su ejecución; para comparativas, usa el mismo benchmark en ambas máquinas para que NI y mezcla de instrucciones sean comparables.

- CPI medio ponderado suele calcularse como Σ (CPI_i × peso_i), donde cada CPI_i corresponde a una clase de instrucción y peso_i es la fracción de esa clase en el programa. Esta visión por clases permite ver dónde optimizar (por ejemplo, loads lentos o divisiones costosas).

- IPS (Instrucciones por segundo) a menudo se aproxima como IPS ≈ Frecuencia × IPC. Ojo con pipelines, dependencias, predicción y vaciados de cauce: en la práctica, bursts y penalizaciones pueden alejarte de la cifra teórica.

- FLOPS en un sistema simple se estima como Frecuencia × operaciones flotantes por ciclo (según el ancho vectorial y unidades FPU), y en paralelo como FLOPS totales ≈ Σ FLOPS de cada procesador. Diferencia si trabajas en SP o DP y recuerda la distinción entre FLOPS nativos y normalizados.

Escalabilidad: Ley de Amdahl, Ley de Gustafson, speed-up, eficiencia e isoeficiencia

Otras fórmulas importantes para el cálculo del rendimiento de los ordenadores, eficiencia, etc.:

- Ley de Amdahl modela la ganancia al acelerar una parte del sistema. Si una fracción f del tiempo no se beneficia de la mejora, el speed-up máximo queda acotado por 1/f. En paralelo, con fracción paralelizable p, el límite típico se expresa como S(N) = 1 / ((1 − p) + p/N). Mejorar el cuello de botella (reducir la parte secuencial efectiva) es lo que más paga.

- Aplicación al pipeline: segmentar reduce latencias por instrucción en steady state, pero burbujeos, riesgos de datos y fallos de predicción añaden penalizaciones que limitan el speed-up ideal. Profundizar pipeline eleva frecuencia pero también penalizaciones por vaciado.

- Ley de Gustafson adopta otra óptica: al crecer el problema con el número de procesadores, S(N) ≈ N − α (N − 1), donde α aproxima la fracción secuencial al escalar la carga. Subraya que el reparto de carga y el overhead marcan la eficiencia real.

- Eficiencia se define como E = S(N) / N. Al aumentar N, E tiende a bajar por coordinación, memoria compartida y desequilibrios. La isoeficiencia busca cómo hacer crecer el tamaño del problema n para mantener E constante al aumentar p (procesadores), absorbiendo el overhead.

Memoria, caches, ancho de banda y almacenamiento: el otro 50% del rendimiento

Además de los cálculos para el procesamiento, también es importante el rendimiento de las memorias, cuyas fórmulas más importantes son:

- La jerarquía de memoria condiciona el CPI: un acceso a caché puede costar 1 ciclo, mientras que a RAM cientos de ciclos. Las tasas de fallo/acierto importan tanto o más que el ancho de banda y la latencia brutos. Mejor hit-rate equivale a menos penalizaciones y menos energía gastada en ir a memoria.

- Definiciones clave: Miss rate = nº de fallos / nº total de accesos y Hit rate = nº de aciertos / nº total de accesos. Subir el tamaño de la caché de instrucciones o datos y mejorar la localidad de tu código incrementan el hit-rate y reducen CPI.

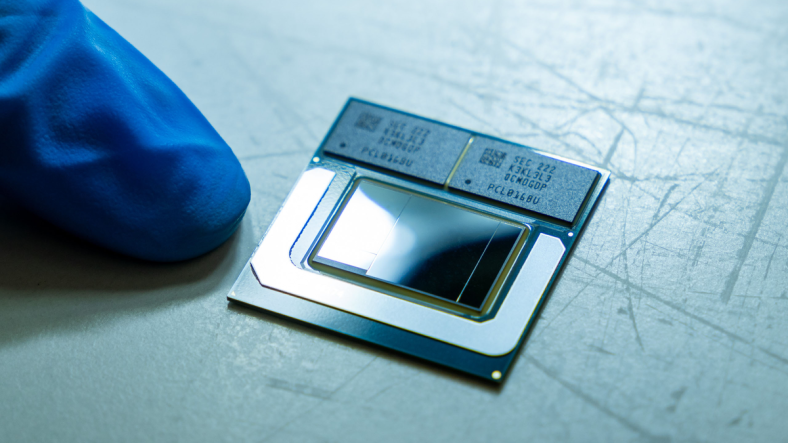

- DDR y frecuencia efectiva: las memorias DDR realizan 2 transferencias por ciclo del controlador, por eso DDR4-3200 equivale a 1600 MHz de memclk. El ancho de banda teórico por módulo se aproxima como memclk × 2 × ancho_bus (bits) × nº de canales, y se expresa en bytes/s (divide por 8). Ejemplo clásico de DDR4-3200, bus 64-bit, Dual Channel: 1.600.000.000 × 2 × 64 × 2 = 409.600.000.000 bits/s ≈ 51,2 GB/s.

- Latencia rotacional en HDD (cuando el cabezal ya está en la pista): se estima como 0,5 rotación / (RPM/60). Para 7200 RPM: 0,5 / (7200/60) ≈ 4,16 ms. Buffers y caches del disco pueden amortiguar parte del tiempo de acceso, pero no eliminan la naturaleza mecánica del retraso.

- Demanda de memoria y cómputo: en cargas HPC se analiza la intensidad operativa (FLOP/byte), relacionando instrucciones de coma flotante y movimiento de datos. Una baja intensidad delata limitación por memoria; una alta, limitación por cómputo. Optimizar layouts y accesos secuenciales puede cambiar por completo el perfil de rendimiento.

Consumo y eficiencia: TDP, potencia dinámica y herramientas

Por otro lado, también tenemos las cuestiones del consumo y eficiencia:

- TDP no es consumo real: es objetivo térmico/diseño. El consumo varía con carga, voltaje y frecuencia efectivos. Bajo cargas ligeras, el consumo medio real suele ser muy inferior al TDP.

- Potencia dinámica aproximada: P = C · V² · F. C es la capacitancia conmutada, V el voltaje y F la frecuencia. Subir voltaje penaliza cuadráticamente; de ahí que el overclock con overvolt cause saltos grandes de consumo y calor. Además de la parte dinámica, hay fugas (leakage) que crecen con temperatura y proceso.