- Sandisk y SK hynix trabajan en HBF: ancho de banda tipo HBM y 8–16× más capacidad.

- Basada en BiCS y ensamblaje CBA, con hoja de ruta: muestras en 2026 y productos en 2027.

- Ecosistema y estándar: consejo asesor, premio 2025 y foco en métricas reproducibles.

- Lecciones de consumo: claridad de especificación y pruebas oficiales para evitar polémicas.

Sandisk y SK hynix han sellado una alianza estratégica para impulsar una nueva categoría de memoria: la Flash de Alto Ancho de Banda (HBF). Esta propuesta nace con vocación de servir a la ola de cargas de trabajo de inteligencia artificial, donde mover y alimentar datos sin cuellos de botella se ha convertido en el nuevo deporte de élite del hardware.

La colaboración está orientada a definir una especificación común, consensuar requisitos técnicos y construir un ecosistema alrededor de HBF, de modo que se facilite su adopción desde centros de datos masivos hasta despliegues en el edge. La ambición es clara: combinar gran capacidad, un ancho de banda al nivel de las memorias de alto rendimiento y un coste competitivo.

Qué es HBF y por qué llega ahora

HBF persigue ofrecer un ancho de banda comparable al de HBM (High Bandwidth Memory) con una capacidad entre 8 y 16 veces mayor, según han adelantado las compañías, y hacerlo a un precio que encaje en despliegues de IA a gran escala. Esto responde a la creciente demanda de memorias escalables y a la altura de las aplicaciones de IA que mueven datos descomunales en tiempos mínimos;

Desde SK hynix, el Dr. Hyun Ahn incidió en que estandarizar HBF facilitará su adopción y desatará el potencial de la IA y otras cargas basadas en datos. En el fondo, el reto ya no es sólo computar más, sino alimentar a los aceleradores con datos a la velocidad adecuada y sin penalizar la densidad ni disparar los costes.

En la jerarquía de memoria tradicional, la caché y la RAM han sido los puntos rápidos (y caros), mientras el almacenamiento persistente actuaba como gran depósito más lento. La experiencia muestra que cuanto más crítico es un dato, más cerca y más rápido debe estar: de ahí que la RAM sostenga volúmenes que se usan activamente o se prevé reutilizar, evitando golpes de latencia al volver a leer del disco.

Aprender más sobre tipos de memoria RAM puede ayudar a entender mejor cómo se integran estas tecnologías en la estructura general de un sistema.

De qué tecnologías parte HBF: BiCS y CBA

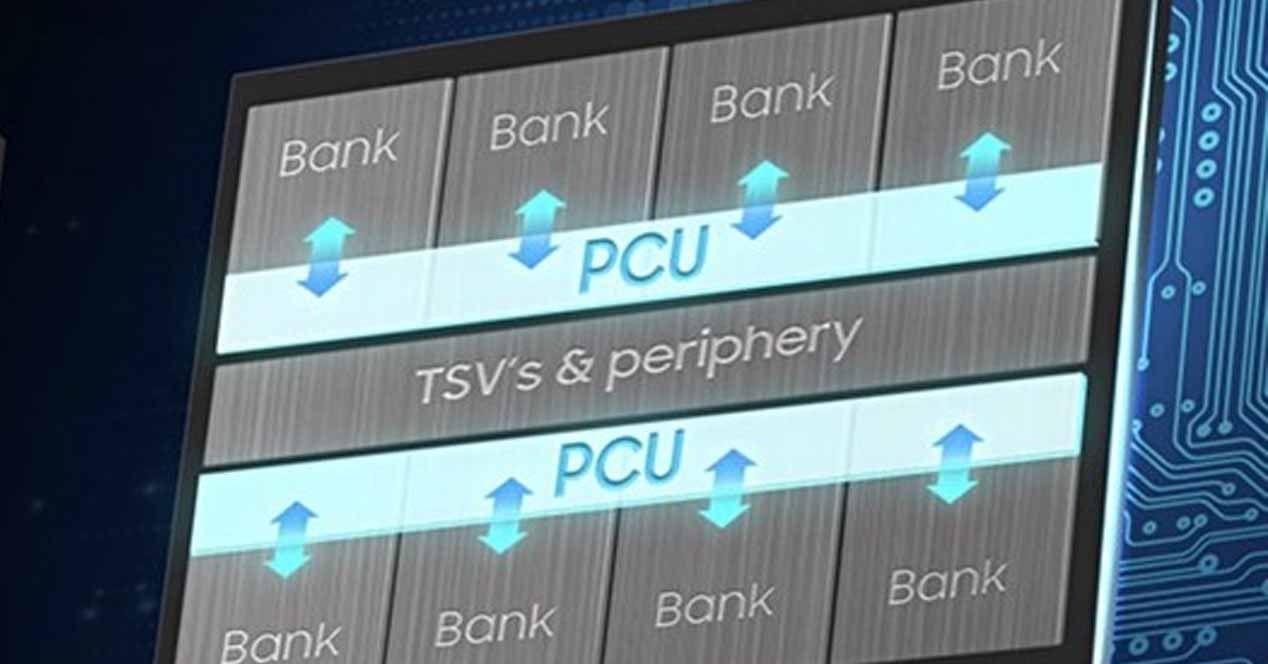

HBF se apoya en la tecnología BiCS de Sandisk (su NAND apilada en 3D) y en una técnica de ensamblaje propia denominada CBA, desarrollada junto con SK hynix. Esta combinación busca maximizar el paralelismo interno y las interfaces para que el subsistema flash entregue un caudal sostenido elevado sin sacrificar la densidad total en el paquete.

La clave no sólo está en la célula de memoria, sino en cómo se empaquetan los dies, cómo se enrutan las señales y cómo se escala el número de canales. El ensamblaje avanzado (CBA) apunta a apilar y conectar múltiples matrices con un presupuesto térmico y de integridad de señal bien controlado, condiciones necesarias para alcanzar los niveles de ancho de banda de HBM.

Para profundizar en el funcionamiento de las memorias modernas, puede ser útil consultar el glosario de memoria RAM.

Rendimiento objetivo: HBM en ancho de banda, multiplicador en capacidad

La promesa de HBF se resume en tres ejes: ancho de banda estilo HBM, capacidad 8-16× superior y coste contenido. En términos prácticos, esto permitirá entrenar e inferir modelos con contextos más grandes, bases vectoriales más extendidas y lotes de inferencia menos constreñidos por el tamaño del conjunto activo.

¿Por qué no solo HBM? Porque HBM, aun siendo líder en ancho de banda, se ve limitada en capacidad total y presenta costes y complejidades de integración elevados (interposers, stacks, packaging especializado). HBF intenta tomar lo mejor del mundo flash (densidad y coste) y empujar esos atributos hacia una liga mucho más alta de ancho de banda, cerrando el hueco entre DRAM/HBM y almacenamiento persistente.

Para comprender el papel del almacenamiento en la arquitectura actual, puede consultarse diferencias entre disco duro y memoria RAM.

La IA y el empuje de la memoria: contexto útil para entender HBF

Las aplicaciones de IA han tensionado toda la pirámide de memoria: los modelos crecen, los contextos se alargan, los conjuntos de datos explotan y la ventana de servicio exige latencias y caudales que el “disco” tradicional no puede ofrecer. Aquí es donde encajan soluciones que acercan grandes volúmenes de datos al cómputo con el máximo throughput posible.

Recordatorio rápido: DDR y la carrera por la eficiencia. La memoria DDR duplicó el flujo por ciclo (subida y bajada), lo que explica por qué una DDR4 “3200” opera a 1600 MHz reales. Con el tiempo, la industria bajó voltajes (de ~2,5 V a ~1,05 V en DDR4) y mejoró el rendimiento y la eficiencia térmica, preparando el camino para módulos más rápidos y estables.

Este conocimiento es relevante porque HBF no busca competir en latencia con DRAM, sino complementarla en capacidad y caudal. Acerca “grandes lagos” de datos al ritmo que exigen los aceleradores modernos. Se integra en una arquitectura que combina cachés, DRAM/HBM y almacenamiento en distintas capas.

Lecciones de la industria: estándares, transparencia y cómo contarlo

Una advertencia importante del ámbito de consumo es la confusión que genera la falta de claridad en las especificaciones. En hilos de discusión sobre memorias en foros se vieron debates y desencuentros por diferencias entre memorias UFS 2.0 y 2.1, con usuarios midiendo su rendimiento con apps como Androbench y obteniendo lecturas secuenciales variadas.

Casos de “random write” con valores muy dispares, hasta que una actualización de firmware o software mejoró los resultados significativamente. Esto evidenció la importancia de definir claramente y comunicar las especificaciones.

Además, algunos usuarios identificaron proveedores y revisaron marcas y versiones basándose en códigos o herramientas, contrastando rendimientos en diferentes pruebas. Se detectaron diferencias en lectura y escritura, influenciadas por firmware, y en algunos casos, se confirmaron con benchmarks oficiales.

Este escenario enseña la importancia de la estandarización y la transparencia en la comunicación sobre especificaciones de memoria. HBF debe definir claramente qué significa “cumplir la especificación”: caudales sostenidos, latencias máximas, topologías, condiciones de prueba, para evitar interpretaciones erróneas y garantizar confianza tanto en fabricantes como en usuarios.

Dónde encaja HBF: centros de datos y edge

En centros de datos, HBF puede funcionar como un “tier caliente” de alta capacidad para cargas como entrenamiento, índices vectoriales o lakes de features, que necesitan varios cientos de GB/s. Aunque no reemplaza a la DRAM/HBM, permite reducir los traslados desde almacenamiento más lento y ampliar la capacidad sin elevar excesivamente el coste por GB.

En aplicaciones edge, con limitaciones térmicas y presupuestarias, HBF posibilitará modelos más grandes en sitio (o mayor número de modelos en paralelo), sin necesidad de rediseñar cajas para refrigerar stacks HBM. Esto favorece inferencias con menor latencia y mayor privacidad, así como una mayor resiliencia ante cortes de red.

Reconocimiento y próximos hitos

El premio en Future of Memory and Storage 2025 valida la propuesta y su potencial transformador. Con primeras demostraciones en la segunda mitad de 2026 y dispositivos con HBF para 2027, los siguientes pasos incluyen demos públicas con métricas parametrizadas, kits de desarrollo y publicación de la especificación para su adopción por terceros.

El Consejo Asesor Técnico de Sandisk aporta una capa adicional de confianza: asesores internos y externos verificarán el cumplimiento de los objetivos de rendimiento y estabilidad, asegurando que en la práctica se logre la repetibilidad y el rendimiento convertido en experiencia real en campo.

Con todo lo anterior, HBF surge como una pieza clave para desatorar uno de los principales cuellos de botella en la IA: la memoria. Si cumple sus promesas de ancho de banda comparable a HBM, capacidad 8-16 veces superior, costos contenidos y estandarización transparente, facilitará que los aceleradores estén más tiempo activos en cálculo y que las arquitecturas de datos sean más simples y eficientes, tanto en centros de datos como en el edge.