Seguro que has escuchado hablar de big.LITTLE en el mundo ARM. Y también has visto este término para referirse a los nuevos procesadores como los de Intel que usan dos tipos de núcleos P-Core y E-Core. Pues bien, lo cierto es que big.LITTLE es una marca de tecnología patentada por Arm, pero el término correcto que se debería emplear para otros chips es el de multinúcleo heterogéneo, que es el tema que vamos a tratar en este tutorial.

Quizás también te interese conocer:

¿Qué es multinúcleo heterogéneo?

Mientras que los sistemas multinúcleo homogéneo son aquellos que implementan varios núcleos idénticos, en el caso de los multinúcleo heterogéneo pueden implementar dos o más tipos de núcleos diferentes. Generalmente con la misma ISA, aunque podría haber algunas diferencias respecto a las instrucciones que tolera cada núcleo.

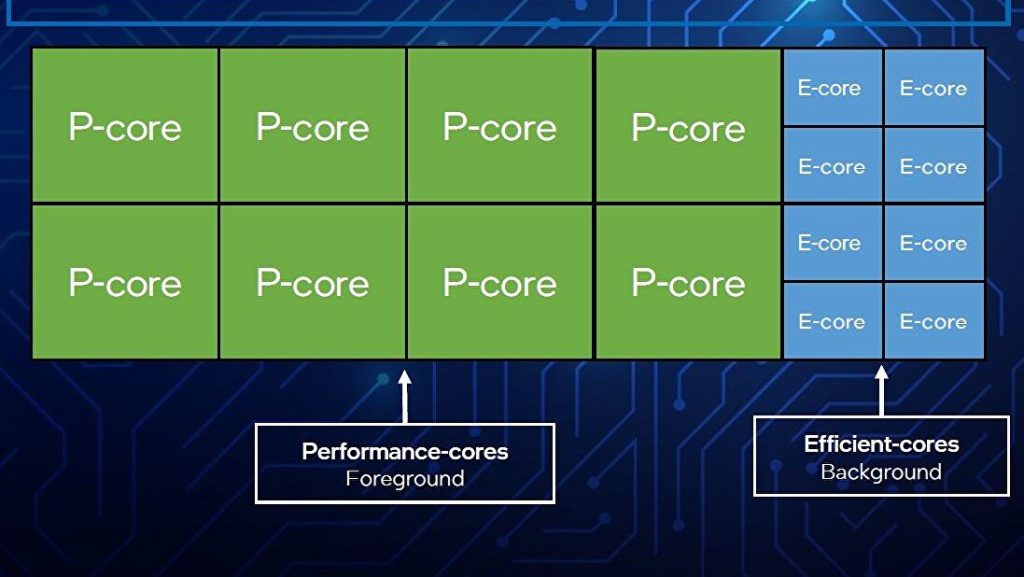

Como se puede apreciar en la imagen anterior, que es un diagrama de una microarquitectura Intel Alder Lake híbrida, tenemos 8 P-Core y 8 E-Core. Es decir, tenemos 8 núcleos de alto rendimiento, con un mayor consumo y mayor superficie del chip ocupada dada su mayor complejidad, y por otro lado tenemos otros 8 núcleos más eficientes energéticamente, más pequeños y con un rendimiento inferior. De esta forma, el sistema operativo podría entregar cargas de trabajo a unos u otros en función de las necesidades de cada momento. Por ejemplo, cuando no es necesario un alto rendimiento, puede hacer uso de los E-Core para reducir el consumo.

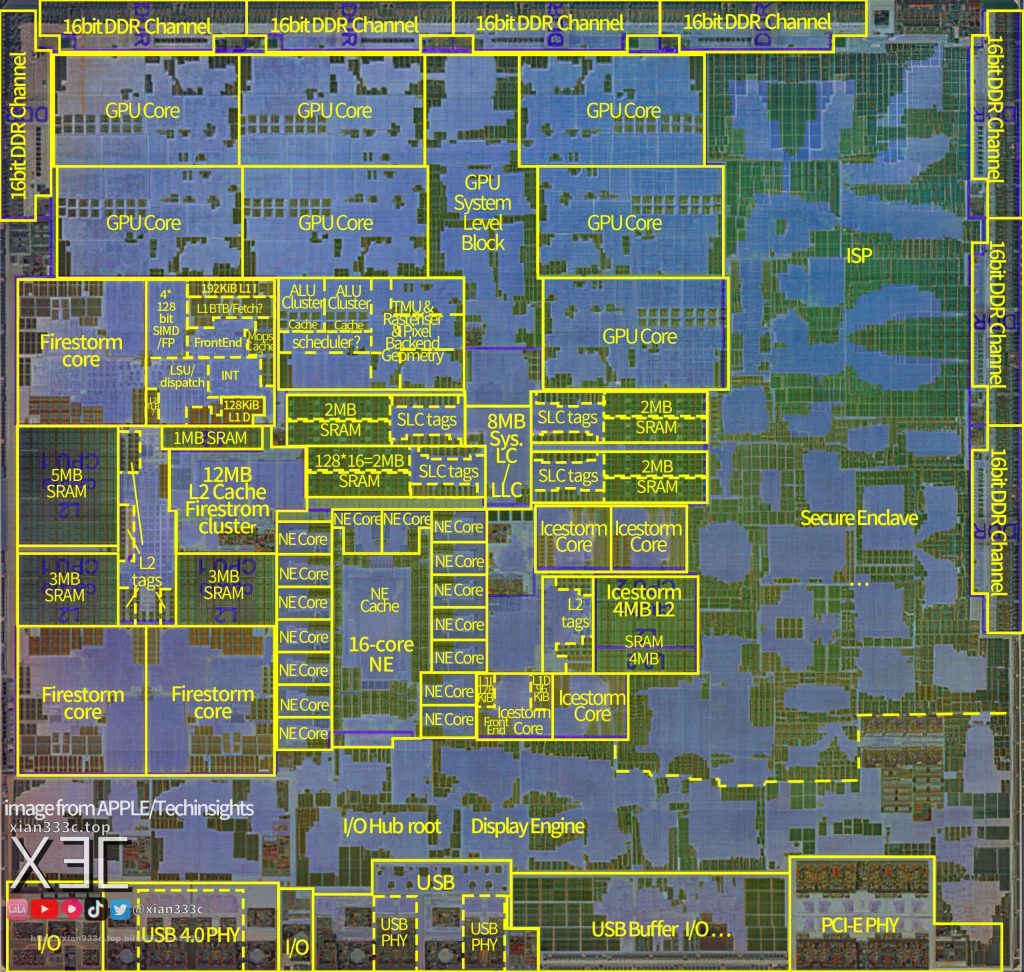

Como se puede apreciar en la siguiente imagen de un dieshot del Alder Lake de Intel, en este chip podemos ver los 8 núcleos P-Core con un tamaño considerablemente mayor y que usan la microarquitectura Golden Cove, comparados con los E-Core que son más pequeños y que se basan en la microarquitectura Gracemont.

AMD parecía dispuesta a usar multinúcleo heterogéneo en su microarquitectura Zen 5, para los futuros Ryzen 8000 Series. Sin embargo, parece que se adelanta, con una segunda actualización para los chips de portátiles Zen 4 con núcleos Zen 4c para los Ryzen 7000 Series. Por su parte, Intel desde el lanzamiento de Alder Lake (12ª Gen), parece que seguirá haciendo uso de ellos en futuros lanzamientos…

Otros, entre ellos AMD, que usará los núcleos Zen 4 y Zen 4c para su primera arquitectura híbrida o de multinúcleo heterogéneo, también siguen los mismos pasos. O incluso Apple Silicon, con sus A-Series y M-Series, que ya sabes que combinan varios núcleos de alto rendimiento y varios eficientes. En el caso de Apple, a los de alto rendimiento les denomina Firestorm, mientras a los eficientes les llama Icestorm, como se puede ver a continuación:

Sin embargo, ni fue Apple ni Intel la pionera en este tipo de arquitecturas heterogéneas. Fue la compañía ARM la que creó primeramente este tipo de implementaciones, y a la que le han seguido el resto. De hecho, la compañía Arm patentó la marca big.LITTLE para referirse a este tipo de diseños híbridos y por eso es la que muchos emplean como término para referirse a las demás, aunque erróneamente…

¿Qué es big.LITTLE?

Arm fue la primera en usar este concepto al que patentó como big.LITTLE, pero no es más que una arquitectura de multinúcleo heterogéneo. Recientemente, Arm ha anunciado otra marca denominada DynamIQ, que es el sucesor de big.LITTLE, y que trae algunas ventajas respecto a ésta.

En ambos casos, los núcleos de mayor rendimiento y los de menor rendimiento se agrupan en grupos conocidos como clusters. El termino big hace referencia a los núcleos de alto rendimiento de tamaño superior, pero implementados generalmente en menor número, y LITTLE hace referencia a los eficientes, que generalmente son más numerosos.

Hay que destacar algunas particularidades de big.LITTEL, ya que son importantes:

- No se puede elegir usar todos los clusters al mismo tiempo a nivel de software. No obstante, actualmente sí que se puede, ya que se ha sustituido el Clustered Switching con el Global Task Scheduler en el kernel del sistema operativo. Y esto permite usar todos a la vez si la carga de trabajo es muy alta.

- Esta tecnología es totalmente compatible con SMP scheduling y DVFS (Dynamic Voltage & Frecuency Scaling) para mejorar la eficiencia según la carga de trabajo en casa momento. Es decir, puede elegir entre núcleos eficientes o de alto rendimiento, pero también puede ajustar el voltaje y la frecuencia de reloj necesaria en cada momento.

- El escalado dinámico o throttling se puede hacer de forma independiente en cada clusters elegido en el momento.

- Según la propia Arm, el ahorro energético y de batería en estos diseños multinúcleo heterogéneo puede llegar al 75%, aunque en la práctica no es del todo así.

- El código fuente del software a nivel usuario no se necesita alterar para que los programas puedan aprovechar esta arquitectura, ya que el kernel del sistema operativo es el que se encarga de esto. Tampoco los usuarios tienen que hacer nada para elegir los núcleos adecuados en cada momento, todo se hará de forma automática según la carga de trabajo de casa momento.

En cuanto a DynamIQ, presentado por Arm en 2017 como sucesor de big.LITTLE, es muy similar, solo que con algunas mejoras en cuanto a la flexibilidad y escalabilidad. Por ejemplo, con DynamIQ se puede usar hasta 8 núcleos por cada cluster, ya que antes estaba limitado a 4. Además, se podría usar hasta un total de 32 clusters por cada chip, lo que da mucho juego a la hora de implementar núcleos diferentes. También se han mejorado las velocidades de la memoria cache L2, se ha pulido el throttling para mayor precisión, etc.

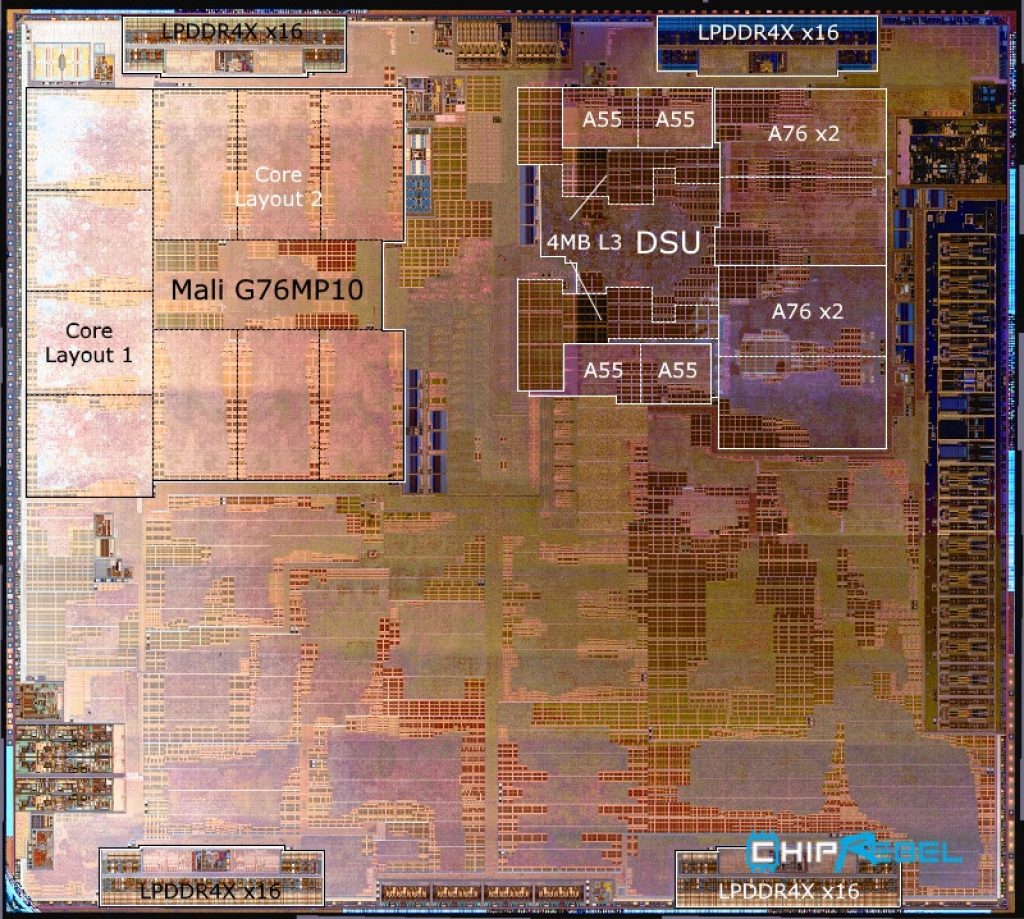

No obstante, no todo son ventajas en cuanto a DynamIQ, ya que es totalmente incompatible con los núcleos Arm diseñados anteriormente. Solo se podrá usar por tanto en los Cortex-A75 y Cortex-A55 en adelante. Es decir, el primer diseño que se podría basar en DynamIQ sería usar un cluster de Cortex-A75 para los núcleos de alto rendimiento, y un cluster Cortex-A55 para los núcleos eficientes.

Además, podría haber más clusters, como he dicho. Por ejemplo, mientras que en muchos SoCs actuales como los de MediaTek Helio, HiSilicon Kirin, Samsung Exynos, etc., se están usando solo dos clusters, Qualcomm para su Snapdragon 888 usa tres clusters, es decir, tres niveles diferentes de núcleos: unos de alto rendimiento, otros eficientes, y un tercero que estaría entre los dos anteriores, es decir, con algo más de rendimiento que los eficientes, pero con mayor eficiencia que los de alto rendimiento.

Ventajas de la arquitectura de multinúcleo heterogéneo

Antes de nada tienes que entender algo. En las arquitecturas multinúcleo no heterogéneo, donde todos los núcleos son de alto rendimiento, cuando se aplica una carga de trabajo, el planificador podrá activar un núcleo para que se ponga a trabajar en un proceso que se necesita ejecutar. Pero este núcleo activo tendrá un consumo alto, aunque la tarea no requiera de tanto rendimiento.

Mientras tanto, en la multinúcleo heterogéno, no es necesario despertar a esos núcleos de alto rendimiento si la tarea a ejecutar no necesita de tanto rendimiento. En su lugar, se activa un núcleo eficiente que realizará la tarea. Esto se traduce en menor temperatura a disipar, menor consumo, y también un menor consumo de batería, es decir, mayor autonomía en los dispositivos que dependen de una batería como los portátiles o los móviles.

Dicho de otro modo, las cargas de trabajo más bajas son las que suelen provocar que le consumo aumente de forma notable, ya que podrían ser asumidas por núcleos eficientes. Eso es lo que trata de hacer esta arquitectura híbrida. Y en en cuenta que muchas veces estamos haciendo uso de cargas poco pesadas, como cuando navegas por Internet, cuando ejecutas una aplicación ofimática, consultas el correo, etc.

Esto puede que no sea un problema demasiado relevante en un procesador para un PC de sobremesa, que está constantemente conectado a la red. Sin embargo, sí que lo es en un equipo portátil o en dispositivos móviles, donde la autonomía depende de la gestión que le hardware haga de ella. No obstante, los núcleos heterogéneos también pueden ayudar a reducir el consumo en los PCs de sobremesa y también en equipos HPC.

Además, ten en cuenta que en los dispositivos móviles, cuando el smartphone o tablet están en modo IDLE, es decir, que no están siendo usados por el usuario, este tipo de hibridaciones se vuelve aún más interesante, ya que no se tienen que despertar a núcleos de alto rendimiento cuando se realizan algunos procesos en segundo plano, como la gestión de notificaciones, comprobación de correos electrónicos, de mensajería instantánea, etc.

Agregar nuevos niveles o clusters adicionales, como en los casos descritos anteriormente, también puede ser inteligente, ya que un cluster intermedio podría hacer que se gane en eficiencia cuando una carga de trabajo es demasiado pesada para un núcleo eficiente, pero demasiado liviana para un núcleo de alto rendimiento. Por tanto, en esos casos se les encargaría a los núcleos intermedios.

Por ejemplo, en vez de los P-Core (big) y los E-Core (LITTLE), podríamos agregar uno medio, para configuraciones que van más allá de la 2+4, 4+8, 8+8, etc., como la del Qualcomm Snapdragon 888 que he citado anteriormente, que sería una 1+3+4, es decir, 1 núcleo de alto rendimiento, 3 núcleos de rendimiento medio (mejor relación rendimiento/consumo), y 4 núcleos eficientes.

Desventajas de los multinúcleo heterogéneo

El gran problema de los multinúcleo heterogéneo es que el sistema operativo debe soportar esta tecnología para poder hacer uso de ella. Por tanto, significa introducir cambios en el código de estos sistemas operativos modernos. Y no es tan sencillo como pueda parecer…

En el caso del kernel Linux, seguro que conocerás los módulos cpufreq que se encarga de gestionar la frecuencia de reloj de la CPU mediante gobernadores, y cpuidle, el otro módulo que se encarga de apagar o encender núcleos de la CPU según la carga de trabajo. Sin embargo, el problema de esto es que funcionan de forma independiente, lo cual es adecuado para PC y HPC, pero no para dispositivos móviles o portátiles, pudiendo generarse conflictos entre ellos y reduciendo su eficiencia.

Por eso, Arm ha introducido un subsistema conocido como EAS (Energy-Aware Scheduling) para sus procesadores que funcionan con el núcleo Linux, como son todos los dispositivos Android, entre otros. Esto hace que ambos módulos trabajen de forma más eficiente, y teniéndose en cuenta, bajando el consumo.

Además, EAS está especialmente diseñado para topologías de multinúcleo heterogéneo como big.LITTLE o DynamIQ, y no funciona con topologías simétricas.

Si nos vamos al lado de los x86, vemos que para el Intel Lakefield no ha habido grandes retoques en el código fuente de Linux para soportar esta arquitectura híbrida. Solo se ha mejorado en áreas de gestión de energía, así como el controlador de escalado de frecuencia. También se han retocado partes del planificador o scheduler del sistema operativo para poder aprovechar estas arquitecturas híbridas.

Evidentemente, conforme se popularicen en el escritorio este tipo de arquitecturas, mejorarán su soporte tanto en Linux como en otros sistemas operativos como Windows 10 y Windows 11, que ya son compatibles también con este tipo de arquitecturas híbridas.

Ten en cuenta que, antes de estos ajustes en los sistemas operativos, el SO era totalmente inconsciente de qué tipo de núcleo de CPU es cada cual, por lo que asignaba las cargas de trabajo a cualquiera de ellos, de forma indistinta. Esto producía problemas de eficiencia y rendimiento importantes. Es decir, el planificador pensará que todos los núcleos son iguales, como hasta hace un tiempo lo eran, y no se adapta a ellos.

Pero esto son cosas que ocurren cuando sale una nueva tecnología de hardware que debe ser soportada por el kernel… Por ejemplo, cuando salieron los primeros procesadores Ryzen, el planificador de Windows no sabía que había núcleos en distintos CCX, y sin darse cuenta podía asignar tareas a núcleos entre los cuales había una gran latencia. Esto se solucionó en las sucesivas actualizaciones del sistema.

Más allá de los ARM

Más allá de los Arm, también hemos visto algunas implementaciones interesantes de este tipo de arquitecturas híbridas o de multinúcleo heterogéneo. Por ejempleo en los Apple Silicon, que aunque se base en la ISA ARM, no usan núcleos IP Cortex-A Series, sino que han desarrollado su propia microarquitectura desde cero.

Más allá de eso, también tenemos que los x86 de Intel y AMD también se han unido a los multinúcleo heterogéneo con sus nuevos lanzamientos. Intel se ha adelantado en este caso, con sus Lakefield, un SoC usado por ejemplo en el Intel Core i5-L16G7 i el Core i3-L13G4 y que tenía un núcleo Sunny Cove (P-Core o Performance-Core) y cuatro núcleos Tremont (E-Core o Efficience-Core). No obstante, el mayor avance sería el Intel Alder Lake, que perfeccionaría a este anticipo que no se puede encontrar actualmente.

Tras el lanzamiento de estos procesadores de Intel, muchos fueron muy críticos, ya que no lo veían adecuado para el PC. De hecho, surgieron algunos problemas con el planificador del kernel del sistema operativo Microsoft Windows, que no sabía muy bien cómo diferenciar a estos núcleos y no hacía un uso óptimo de ellos. No obstante, estos problemas han sido corregidos con nuevas actualizaciones.

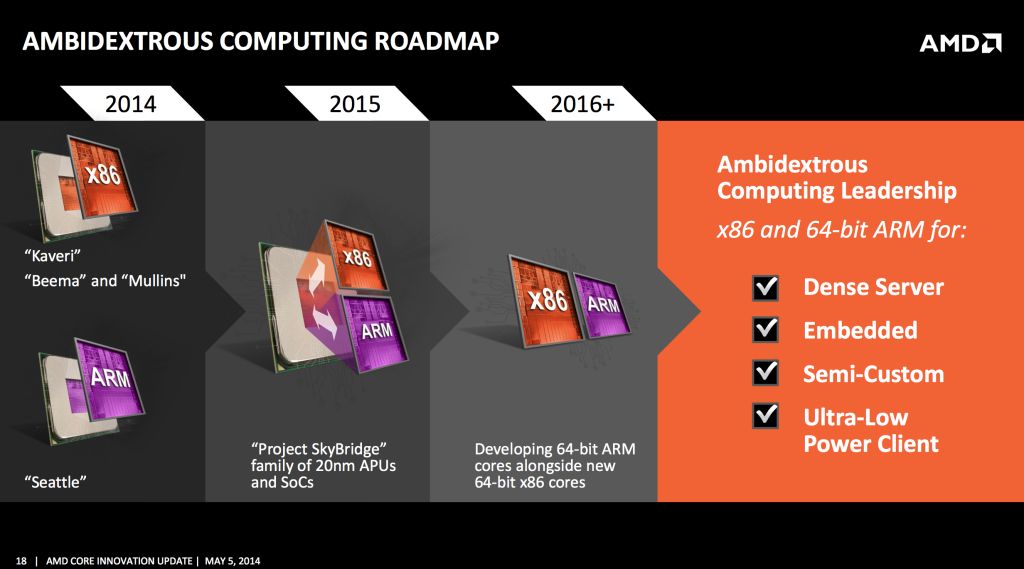

AMD fue más cauta en ese momento y retrasó el lanzamiento de sus núcleos híbridos. De hecho, fue pionera en el uso de la ISA ARM con sus núcleos K12, que finalmente serían cancelados para centrarse en Zen. Ahora, una vez centrada en Zen, ha habido que esperar hasta Zen 4 para ver los primeros diseños de multinúcleo heterogéneo. Se ha destapado recientemente un diseño de AMD Ryzen Phoenix 2, una APU que se estrenará en 2023 y que traería 2 núcleos Zen 4 de alto rendimiento y 4 núcleos eficientes Zen 4c.

Ahora bien, ¿Seguirá esto siendo así? ¿Se verán más futuros diseños de este tipo? ¿Será una moda pasajera? Pues parece que se quedarán entre nosotros por mucho tiempo…

¿Se pueden mezclar distintas ISAs?

Seguramente muchos se estén preguntando si se podrían mezclar núcleos de arquitecturas diferentes, es decir, de ISAs diferentes. Y lo cierto es que sí se puede. De hecho, si te fijas en una APU de AMD o en una iGPU de Intel, mientras la CPU es x86-64, la GPU tiene su propia ISA particular, por lo que se está poniendo en el mismo chip monolítico o en el mismo empaquetado, una ISA diferente.

Pero muchos se preguntarán si sería posible integrar CPUs de diferente ISA. Y la respuesta también es afirmativa. AMD ya estuvo intentando esto con sus SoCs, y que han llegado hasta nuestros días con diseños para sus procesadores al integrar un chip ARM junto con el x86, aunque el ARM esté centrado en la seguridad, ya que se trata de lo que AMD denomina PSP (Platform Security Processor) para los Ryzen Pro, por ejemplo.

Y se puede ir aún más allá, ya que Intel, por ejemplo, ha anunciado que pretende crear chiplets o empaquetados MCM en el futuro con varias ISAs diferentes combinadas, como la ARM, x86 y también RISC-V. De hecho, según la estrategia futura de Intel, la empresa otorgará licencias de IP cores tanto softcore como hardcore para núcleos de CPU para distintas arquitecturas.

Los softcore son núcleos de CPU para ser implementados en un FPGA, y podrían actuar como aceleradores de ciertas tareas específicas o para aportar mayor compatibilidad.

Sin ir más lejos, el procesador que Europa está preparando para la no dependencia tecnológica y que se debe estrenar en el Marenostrum 5 de Barcelona, es un chip que combina por un lado una CPU basada en ARM y también acelerador RISC-V. Y es que, parece que el futuro pasa por la hibridación en muchos sentidos…

En el pasado también hubo algunos intentos de usar varias ISAs en un mismo ordenador. Pero esto lo consiguieron mediante capas de software adicionales que servían de traductores. Un ejemplo de ello lo tenemos en el Transmeta Crusoe y el Efficeon, que eran chips VLIW con unas instrucciones muy largas, de 128-bit, pero que eran compatibles con software x86 gracias a un software denominado Code Morphing escrito por el mismo Linus Torvalds y que se ejecutaba de forma constante y en segundo plano para posibilitar la traducción de las instrucciones de los binarios ejecutables en VLIW.

También hemos visto cómo los Elbrus, los procesadores rusos de los que ahora se ha vuelto a hablar, también hacían algo parecido para soportar software x86 y no quedar marginados en ese sentido. Y también lo hacían con traducciones al vuelo. Sin embargo, ni en el caso del Transmeta ni en el del Elbrus se llegó a implementar un núcleo x86 físico.

En 1994, IBM anuncia el procesador PowerPC 615. Este chip no se fabricó en masa nunca, pero era bastante particular, ya que su principal característica era incorporar un núcleo x86 en el mismo chip que el PowerPC. Es decir, éste fue uno de los primeros prototipos en usar dos ISAs en un mismo procesador.

De esta forma, el PowerPC 615 podía trabajar tanto con binarios compilados para x86 de 32-bit como también para PowerPC de 64-bit. Es decir, admitía los dos repertorios de instrucciones de forma nativa, pudiendo ejecutar más software.

Además, podía trabajar en varios modos:

- Modo x86: el sistema operativo podía elegir el núcleo x86 para ejecutar software para esta ISA de 32-bit.

- Modo PPC 32-bit: este modo permitía ejecutar software con instrucciones PowerPC de 32-bit.

- Modo PPC 64-bit: como el anterior, pero para instrucciones de 64-bit.

- Modo mixto: una especie de mezcla entre los tres anteriores. Este modo mixto podía implicar cambio de contexto en la CPU y una pequeña sobrecarga.

El único sistema operativo que soportó esta CPU PowerPC 615 híbrida fue Minix, y una versión especial del sistema de IBM OS/2.

Pero las particularidades de este chip de IBM no terminaban ahí. Se trataba de un encapsulado de 330 mm cuadrados, con un nodo o proceso de fabricación de 0.35 micras fabricado en las propias fábricas de IBM. En cuanto al empaquetado, y aquí viene lo extraño, era compatible pin a pin con el Intel Pentium, y tenía un rendimiento comparable. Es decir, se podía insertar en una placa base de Intel.

Sin embargo, el PowerPC 615 solo fue un experimento, un prototipo que fue abandonado en parte porque Microsoft Windows nunca llegó a soportar este procesador. Sin embargo, algunos de los ingenieros que trabajaron en el PowerPC 615 saldrían de la compañía para incorporarse al equipo de Transmeeta y aportar su experiencia para el Crusoe.

Sea como sea, ha quedado demostrado que combinar ISAs es posible, aunque no es la mejor solución en todos los casos, al menos en estas épocas donde la tecnología no estaba tan madura como ahora. En la actualidad, podemos esperar diseños interesantes de este tipo, aunque parece que muchos están adoptado la traducción de software dinámica en tiempo de ejecución, con emuladores como Rosetta de Apple para traducir las instrucciones de los binarios x86 de Intel en ARM para Apple Silicon, o lo mismo que estaba tratando de hacer Qualcomm con sus Snapdragon para introducir sus chips también en el mercado de los PCs…