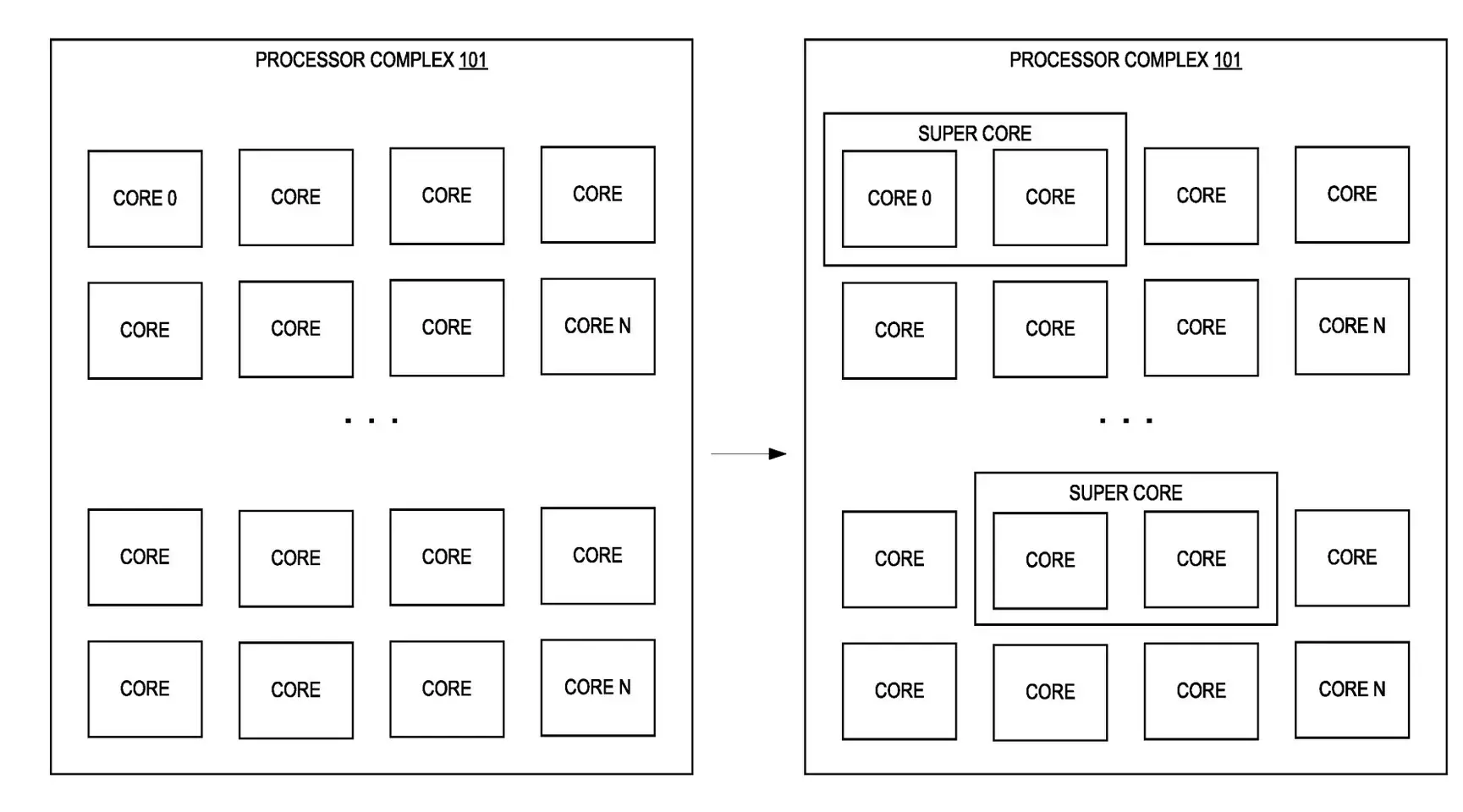

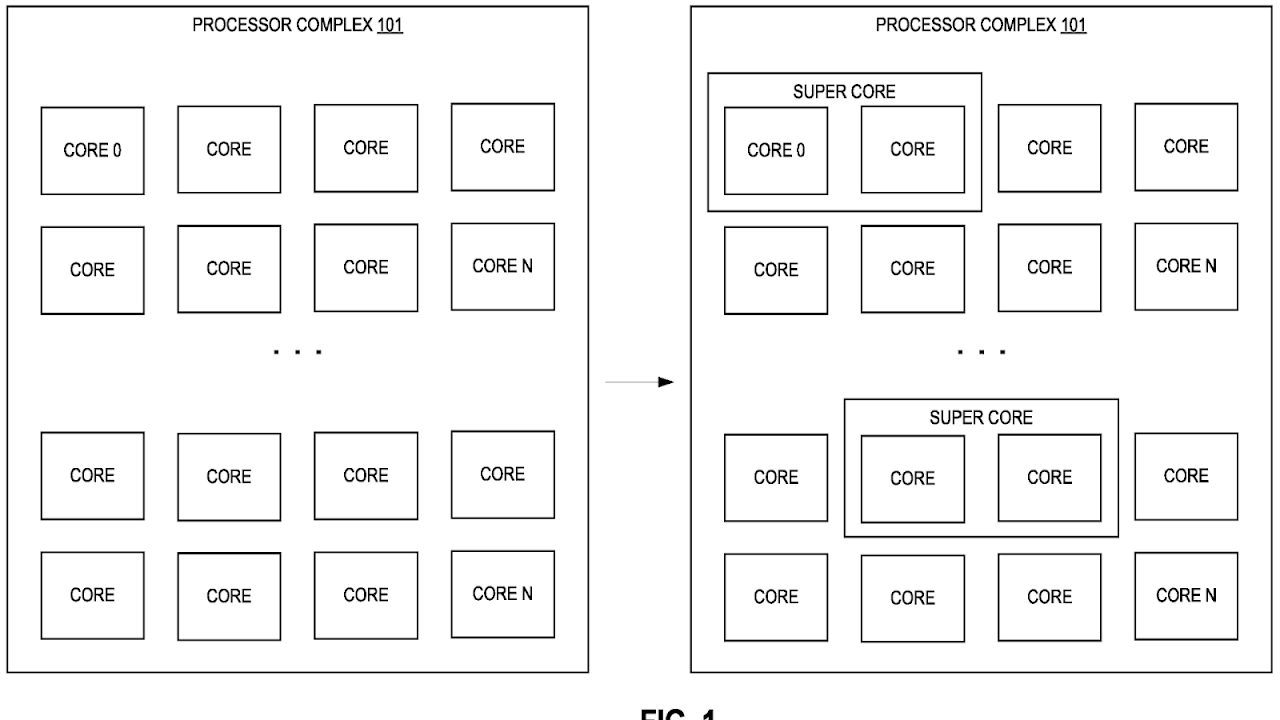

- Patentes de Intel (EP4579444A1 y US20250217157A1) describen SDC, un "supernúcleo" virtual para acelerar un solo hilo.

- Varios núcleos pequeños cooperan dividiendo y reensamblando instrucciones con buffers y mensajería ultrarrápida.

- Objetivo: más IPC y eficiencia sin aumentar voltaje o frecuencia, según detalla la documentación.

- Retos clave: sincronización, coherencia de memoria y soporte de sistemas operativos y compiladores.

Intel ha puesto sobre la mesa una idea que podría cambiar cómo exprimimos el rendimiento por hilo: Software Defined Super Cores (SDC). La propuesta, recogida en documentación de patente, describe la posibilidad de que varios núcleos compactos colaboren como si fueran uno solo para ejecutar un único hilo de trabajo de forma más rápida.

Lejos de apostar únicamente por relojes más altos o por núcleos cada vez más anchos, la compañía explora coordinar recursos existentes para mejorar la eficiencia energética. El planteamiento apunta a crear un “supernúcleo” virtual cuando el software lo necesita y disolverlo después, algo que suena bien sobre el papel, aunque exige soporte del sistema operativo y del compilador para brillar de verdad.

Qué es SDC y qué propone la patente

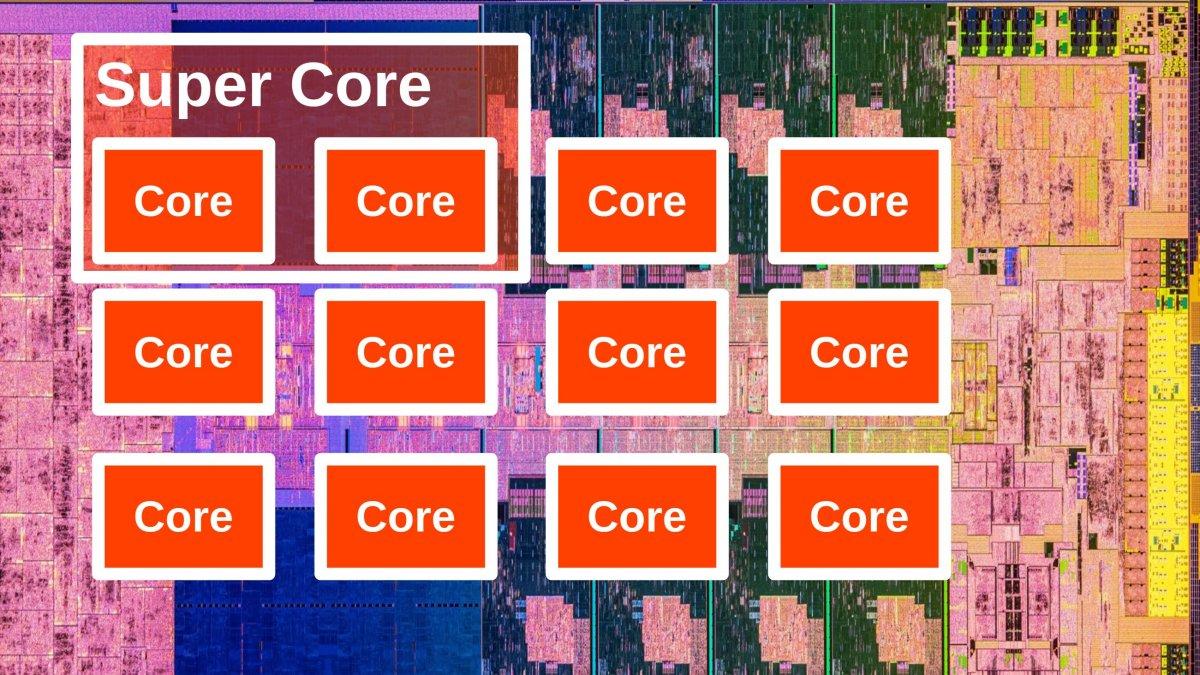

Según las solicitudes EP4579444A1 y US20250217157A1, SDC permitiría que dos o más núcleos ligeros cooperen para ejecutar un solo hilo como si fuesen un núcleo más potente. En vez de diseñar un core gigantesco con retornos decrecientes, la CPU fusionaría dinámicamente núcleos pequeños (como en diseños chiplet) cuando detecta una carga monohilo exigente.

La lógica es sencilla de explicar, aunque compleja de implementar: el procesador divide el flujo de instrucciones en partes, las reparte entre los núcleos colaboradores y, posteriormente, reensambla los resultados preservando el orden del programa. Desde el punto de vista del software, ese conjunto se ve y se comporta como un único core lógico mayor.

Un detalle relevante de la patente es que la cooperación requeriría poco hardware adicional en cada núcleo. La clave está en la orquestación: identificar tramos del código donde compensa paralelizar dentro del mismo hilo (vía marcadores de control de flujo) y garantizar que la ejecución conjunta no rompa la semántica del programa.

La idea encaja especialmente bien con diseños que priorizan densidad y eficiencia como el empaquetado 3D. En escenarios con muchos E-cores, la opción de combinarlos bajo demanda abre la puerta a un rendimiento por hilo más alto sin disparar el coste de área de un gran P-core.

Cómo funciona: división del flujo e interconexión

Para que SDC funcione, los núcleos deben intercambiar datos con latencias muy bajas y mantener una visión coherente de la memoria. La documentación menciona mecanismos como buffers especializados y mensajería rápida entre núcleos para preservar el orden de las instrucciones y la consistencia de los datos.

En la práctica, el flujo de instrucciones se segmenta, se asigna a los núcleos cooperantes y se sincroniza con canales dedicados. Entre los elementos propuestos aparece el denominado Shadow Store Buffer, pensado para asegurar transferencias correctas y observabilidad consistente de las modificaciones entre los participantes.

Esto no es multihilo clásico: el objetivo es que una única hebra se ejecute más deprisa gracias a la cooperación. Si la coordinación es efectiva, la ejecución combinada podría traducirse en un IPC agregado superior, todo ello presentándose al sistema como un solo núcleo lógico.

Otro punto de interés es la activación bajo demanda. La CPU podría entrar en “modo SDC” cuando detecte un tramo monohilo especialmente pesado y volver al modo normal en cuanto deje de ser rentable, optimizando así el uso de recursos sin penalizar otras cargas.

Ventajas, retos y encaje con la hoja de ruta

Sobre el papel, SDC promete tres ganancias claras: más rendimiento por hilo en momentos críticos, mejor utilización de núcleos compactos y potencial para subir el desempeño sin recurrir a más voltaje ni más frecuencia (según recoge la patente). Todo ello puede traducirse en eficiencia por vatio atractiva.

- Escalado dinámico: fusión de núcleos cuando compensa y disolución cuando no.

- Eficiencia: aprovechar silicio existente en vez de crecer en área con un core enorme.

- Transparencia: al software le aparece como un único núcleo ejecutando un hilo.

El reverso de la moneda es conocido: sincronizar múltiples núcleos sin romper el orden del programa es difícil, la comunicación inter-core debe ser ultrarrápida y el sistema operativo, junto con el compilador, necesitan entender y programar bien esta capacidad. Sin ese soporte, el beneficio puede diluirse.

En el ecosistema x86 hay precedentes que ayudan a contextualizar. AMD, por ejemplo, llegó a conectar unidades AVX de 256 bits para ejecutar AVX-512 en generaciones Zen previas, y arquitecturas como Bulldozer compartían bloques entre dos hilos; no obstante, SDC plantea el camino inverso: fusionar núcleos completos con apoyo de software y hardware ligero para acelerar un solo hilo.

De cara al producto, hay quien sitúa esta idea junto a configuraciones con muchos E-cores o en futuras familias como Nova Lake, pero de momento hablamos de documentación técnica y solicitudes de patente. La viabilidad real dependerá de prototipos, de la madurez del microcódigo y de que Windows y Linux integren políticas de asignación que no lastren la experiencia.

Si SDC cuaja, podría ofrecer una vía diferente para estirar el rendimiento monohilo cuando los nodos de proceso o los límites térmicos ponen techo. Si no, quedará como otro intento ambicioso que chocó con la complejidad del software y de la sincronización fina entre núcleos.

La propuesta de Software Defined Super Cores encaja con la tendencia a exprimir mejor los recursos existentes: coordinar núcleos pequeños para parecer uno grande cuando toca, sin disparar consumo ni área. Queda trabajo por delante en hardware, firmware y, sobre todo, en software del sistema, pero el enfoque apunta a una forma distinta de sumar rendimiento por hilo cuando más falta hace.