Los chips necesitan energía eléctrica para funcionar, y entregar ésta no es tan sencillo como pueda parecer en un principio. En los actuales chips avanzados, especialmente la CPU y la GPU, y los SoCs, e incluso los nuevos empaquetados 3D, la entrega de energía supone todo un desafío que te vamos a explicar aquí.

Introducción a la entrega de energía en un procesador

La entrega de energía en un chip se realiza mediante lo que se conoce como PDN (Power Delivery Network), o red de suministro de energía. Esto debe cumplir una serie de requisitos para la tecnología CMOS moderna, y debe entregar la energía de forma eficiente y rápida, además de llegar a todos los puntos donde se necesita.

Para distribuir la señal de reloj se hace algo parecido.

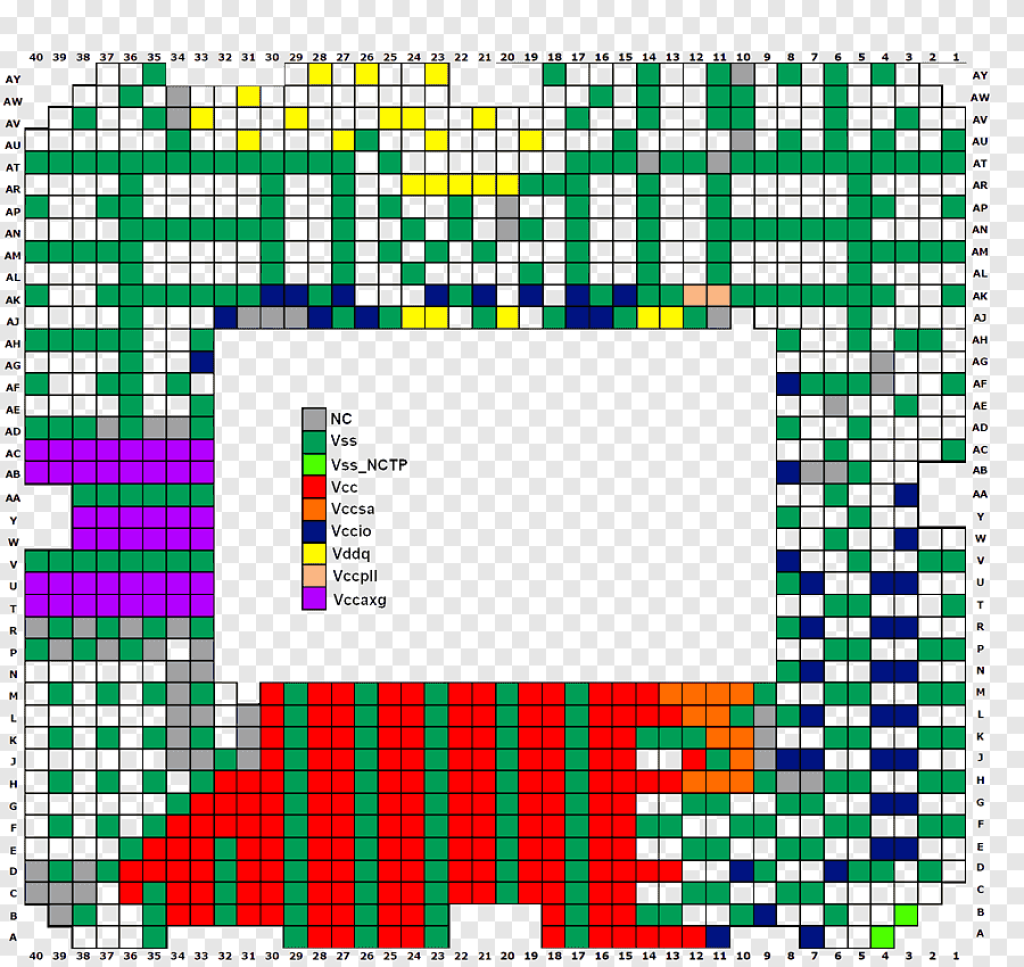

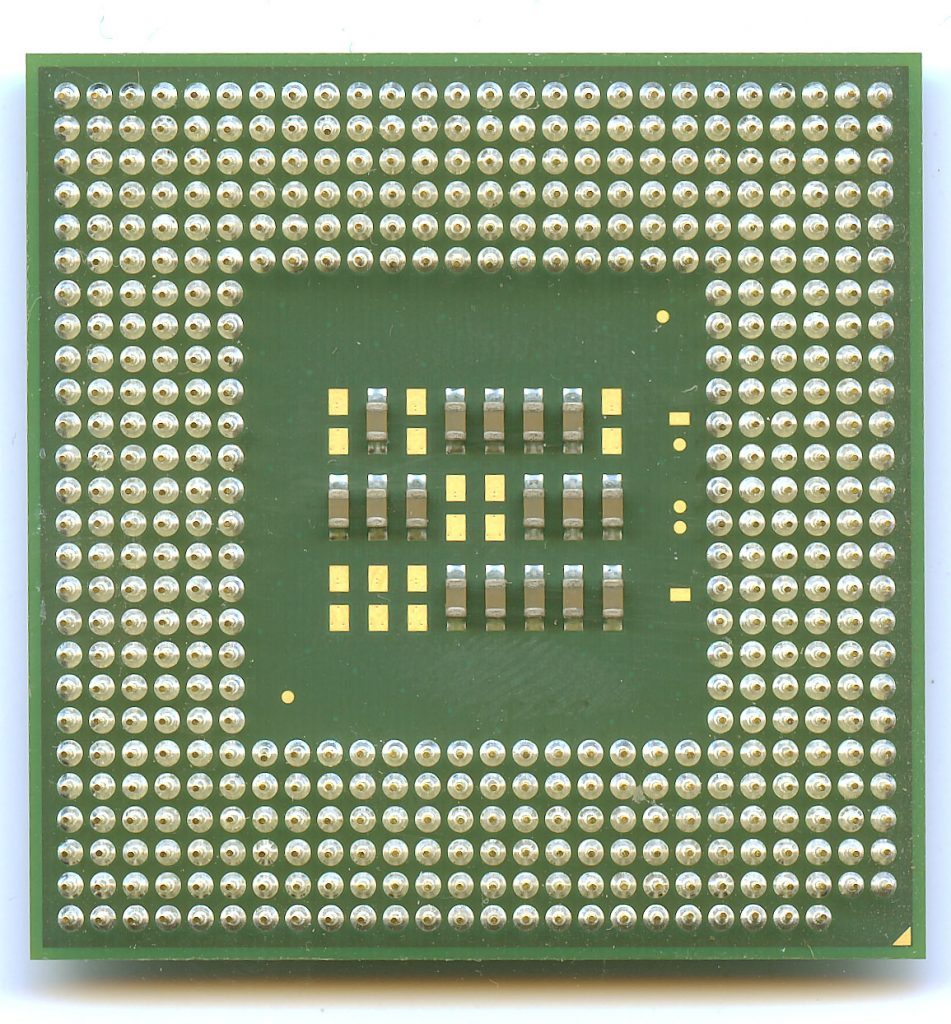

Como se puede ver en la imagen anterior, de un socket LGA 1156 de Intel, la mayoría de los contactos se destinan a suministrar energía (todos los coloreados). El resto son para datos y señal de reloj. Como vemos, existen multitud de entradas para los diferentes voltajes: Vcc, Vss, etc.

Los problemas de entrega de energía para los procesadores avanzados no solo están en los SoCs para dispositivos móviles de 1W, también en las CPUs de 200W o más, pasando por otros aceleradores como el caso del Cerebras CS-1, que es un SoW de 15 kW. Si estos chips quieren dar «alimento» a todos los millones de transistores que hay en el chip y que trabajen a la frecuencia de reloj objetivo, se necesita una red para evitar inestabilidad o que se necesite reducir su frecuencia de trabajo.

La tecnología CMOS con MOSFET suele trabajar en torno a 1V aproximadamente, e incluso existen modelos de FinFET que pueden hacerlo a 0.65V. Pero no te debes dejar engañar por estos valores bajos de voltaje. El consumo de energía del circuito dependerá será proporcional al cuadrado del voltaje. Y también hay que tener en cuenta que se necesitan intensidades de corriente grandes.

Por ejemplo, si tenemos en cuenta un Intel Xeon Cascade Lake, que tiene un TDP de 205W y funciona a 1V, se necesitaría 205 A de intensidad de corriente. Aunque esto sin tener en cuenta que los procesadores pueden hacer throttling o escalar dinámicamente, lo que podría hacer que eventualmente bajen de ese nivel o suban, según la carga de trabajo y rendimiento necesario en cada momento.

La intensidad de se puede calcular mediante la fórmula I = C · V · α · f. Donde I es la intensidad de corriente en amperios (A), C es la capacitancia de carga, V es el voltaje al que trabaja la CPU, α es el factor de actividad y f es la frecuencia de conmutación. El factor de actividad varia entre 1 para muchos procesadores que conmutan dos veces por ciclo de reloj, 0.5 para algunos contadores binarios que conmutan una vez por ciclo, 0.25 para los que lo hacen solo una vez cada dos ciclos, etc. En el caso de una memoria caché, este factor puede ser mucho menor.

¿Cómo se calcula esto? Pues muy sencillo, imagina que tenemos una CPU que trabaja a 1.25v, que la capacitancia es de 0.1 fF, y la frecuencia a la que trabaja de 3 Ghz, con un α=1, entonces nos da como resultado que la corriente es de 0.375μA. Puedes pensar que es una corriente ínfima, de entorno a un tercio de un microamperio. Pero esto hay que multiplicarlo por el número de transistores de ese chip, que vamos a suponer que sea 800 millones, lo que daría como resultado un consumo de 300A.

Generalmente, cuando se entrega la energía necesaria a un chip, es más eficiente usar un voltaje alto y una corriente baja. Cuanto mayor es el voltaje, más pequeña será la intensidad de corriente necesaria, además de necesitar menos interconexiones para distribuir la energía. Por otro lado, las pérdidas resistivas son proporcionales al cuadrado de la corriente, por lo que si se reduce, también habrá menos pérdidas y mejorará la eficiencia energética. Es la misma razón por la que las líneas de alta tensión que recorren largas distancias pueden trabajar a miles de voltios, para pérdidas inferiores.

Sin embargo, aumentar el voltaje y decrementar la intensidad también implica desventajas importantes. Por eso, los diseñadores de chips tienen que buscar un buen compromiso para tratar de usar un voltaje tan alto como sea posible para las líneas a través del sistema, y luego convertirlo en un voltaje tan bajo como sea posible para que sea estable y eficiente.

Anatomía de una PDM

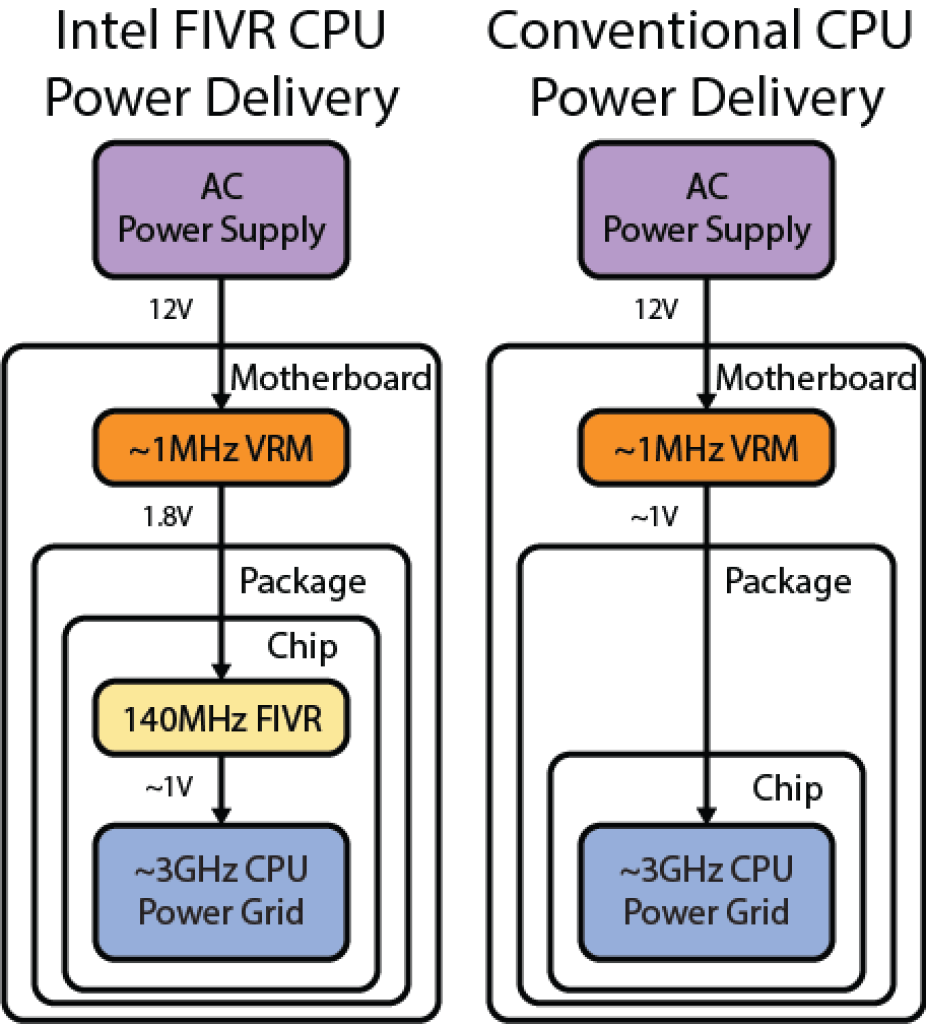

Como se puede apreciar en la imagen anterior, la fuente de alimentación o PSU convertirá los 220V CA en un voltaje de 12V CC que entregará a la placa base (en el caso de los portátiles, las baterías de litio típicas suelen entregar unos 3.7V de CC), pero esta corriente no es adecuada para el procesador.

Por este motivo, antes de entrar en la CPU dicho voltaje, pasa por los conocidos como VRM o módulos de regulación de voltaje para convertirlos en el voltaje deseado, por ejemplo 1V. Además, estos VRM están colocados muy cerca del procesador, generalmente alrededor de él para que la distancia sea la mínima posible para evitar pérdidas.

Una vez llega este voltaje al procesador, una PDN se encargará de abrirse por todas las partes necesarias donde debe entregar la energía. Lo hará a través de los pads o contactos y abriéndose paso por las distintas capas de interconexiones de metal para llegar a los núcleos, memoria caché, etc.

En el caso de algunos sistemas de Intel (solo para servidores), el proceso es ligeramente diferente, ya que se añade una etapa adicional, la FIVR (Full-Integrated Voltage Regulator). Este regulador integrado dentro del propio chip del procesador hará las regulaciones de voltaje y las distribuirá por los diferentes rieles o líneas de alimentación. El FIVR es necesario en estos casos puesto que en las placas base para servidores se suelen usar voltajes de PSU de 12 o 48V, y los VRM pasan este voltaje a 1.8V y luego el FIVR se encargará de convertir este voltaje a lo deseado, según las necesidades de una línea de alimentación en particular.

Una ventaja del FIVR es que el voltaje entregado al procesador desde los VRM es aproximadamente el doble que en los sistemas convencionales, y esto reduce la corriente necesaria en casi un factor de dos, lo que hará que se necesiten menos pines de alimentación, etc. No obstante, no es lo más eficiente, ya que el FIVR pierde algo de eficiencia.

Reducir la cantidad de contactos para la entrega de energía te puede parecer una chorrada, pero no solo influye en abaratar costes, y es que uno de los problemas con los que se enfrentan ahora muchos diseñadores de CPU es la cantidad de conexiones necesarias. Por ejemplo, aquí tienes una muestra de cómo han crecido últimamente en la línea Intel Xeon:

Intel Xeon Sapphire Rapids (socket LGA 4677 contactos) comparado con el tamaño del socket para el Sierra Forest (LGA 7529 contactos).

Las condiciones dinámicas lo ponen aún más complicado

Como bien sabes, los procesadores modernos no siempre mantienen un mismo voltaje y una misma frecuencia de reloj, sino que pueden hacer lo que se conoce como escalado dinámico (DVFS), adaptándose a las condiciones de carga de cada momento. El estado de energía TDP, tampoco será estable, ya que también puede variar según las condiciones. Y no solo eso, además no todas las partes tendrán el mismo estado de energía en cada momento, puede haber núcleos funcionando a una frecuencia-voltaje inferior, otros a mayor, algunos pueden estar totalmente apagados, etc. Todo esto no hace más que complicar la situación de entrega de energía.

Por otro lado, no todos los transistores de un mismo núcleo estarán funcionando. Puede que de un ciclo a otro cambie el número drásticamente, lo que también cambiará la demanda de energía de forma drástica. Por ejemplo, cuando se realizan operaciones con enteros se necesitarán menos transistores activos que cuando se usan operaciones complejas como las AVX512, donde se dispara el consumo al necesitarse unidades de ejecución más complejas. En esos momentos, se puede hacer que el voltaje baje (caída), debido a la mayor demanda de corriente o consumo.

Cuando se piensa en chips para dispositivos de bajo consumo, como los dispositivos móviles, el reto puede ser incluso más complejo, ya que hay que optimizar aún más la eficiencia, por ejemplo, funcionando en forma de ráfaga, para entregar el máximo rendimiento solo en periodos de tiempo muy cortos.

Por otro lado, hay que destacar que los reguladores de voltaje, sean VRM o FIVR, son mucho más lentos que los picos de corriente transistores causados por la actividad de conmutación de los transistores. Por ejemplo, podemos toparnos con un periodo para estos reguladores de 0.32 ms, lo que significa demasiado tiempo. Teniendo en cuenta que la CPU tuviese 3.2 Ghz de frecuencia de reloj, eso significaría esperar 1000 ciclos de reloj. Y los hay más lentos… Es cierto que algunos nuevos reguladores LDO (Low-DropOut) son muy rápidos, pero no diejan de tener sus problemas también, como la ineficiencia, en algunos casos cuando se requieren cambios grandes de voltaje, como los de >10% del voltaje total.

Sin tener en cuenta esto, se podrían generar fallos, caídas de voltaje importantes e incluso el apagón total. Y, como ocurre en Fórmula 1, no todo es tratar de poner o quitar, la cosa no es tan simple, hay que buscar siempre un compromiso. Un pequeño cambio puede afectar a muchas otras cosas, aunque corrija el problema por el que se realizó dicho cambio.

Lo que han hecho algunos es crear técnicas para tratar de paliar estos problemas. Muchos usan combinaciones de técnicas. Por ejemplo, AMD desarrolló un sistema de frecuencia de reloj adaptable que hacía que la frecuencia de reloj bajase cuando se producían caídas de voltaje, y así no generar el fallo o inestabilidad.

Los condensadores de desacoplamiento al rescate

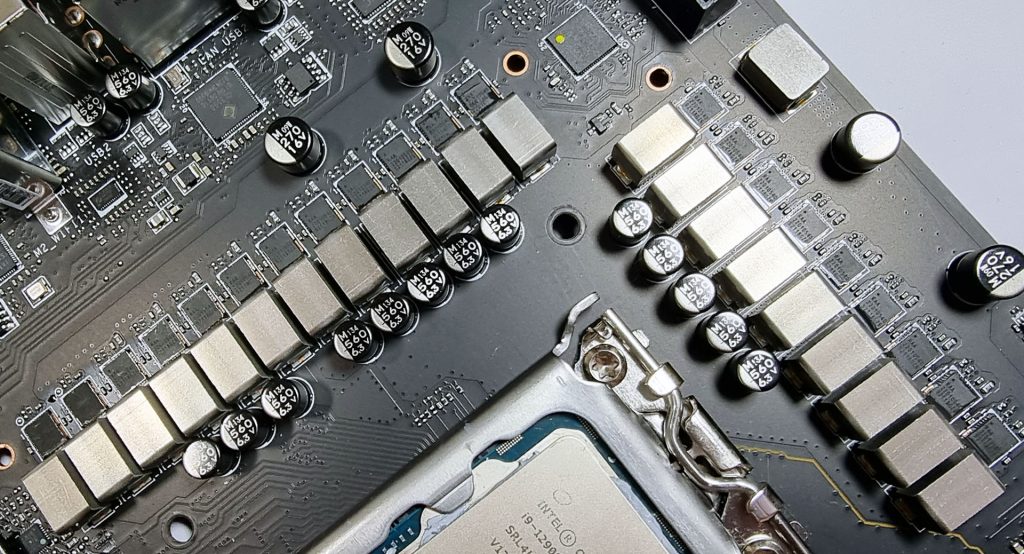

Para solucionar el desajuste entre los picos de corriente transitorios y la latencia de los reguladores de tensión, las placas base usan condensadores de derivación o desacoplamiento. Estos condensadores actúan como depósitos de energía eléctrica, agregando así reservas para cuando sea necesario entregar. Es decir, son una especie de parche mientras los VRM empiezan a responder.

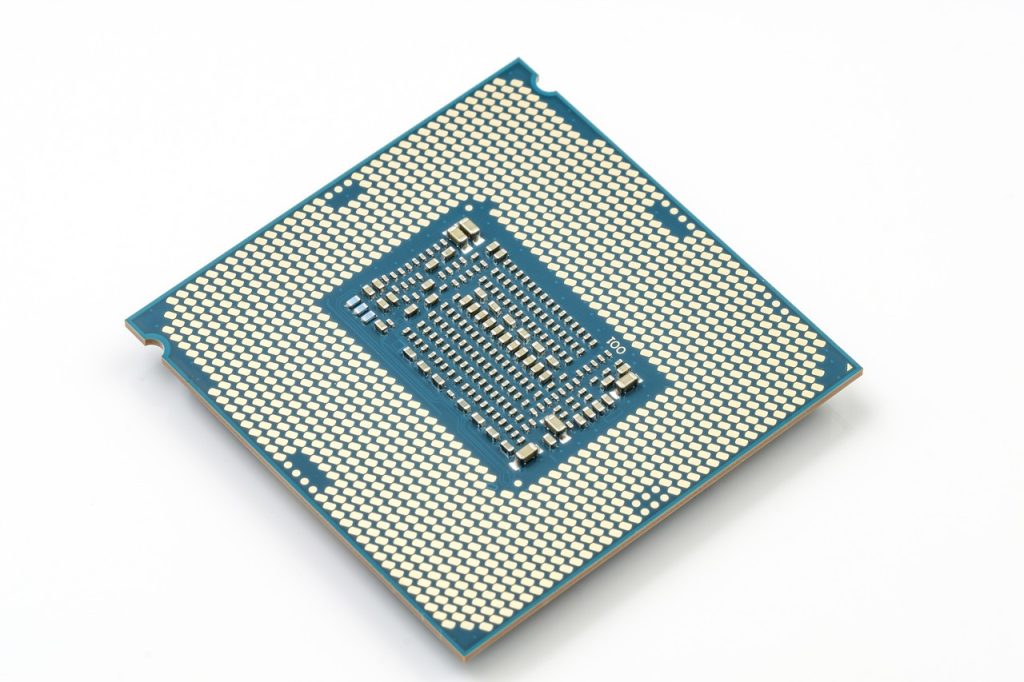

Por eso verás que alrededor de la CPU o del socket de la placa base, hay una buena cantidad de condensadores para aportar este suministro de reserva. Además, en el propio empaquetado del procesador, también suele haber condensadores más pequeños tipo SMT, como se puede apreciar en la imagen (estos aún más cercanos a los circuitos activos para brindar una respuesta más rápida a los cambios transitorios):

Gracias a la proximidad de estos condensadores con respecto a las áreas cruciales del procesador, pueden amortiguar ese ruido y mejorar la capacidad de entrega de energía rápida. No obstante, estos condensadores no son perfectos, también tienen fugas, y no son los ideales. Además, pueden suponer un problema para su emplazamiento su el área del empaquetado está muy congestionada.

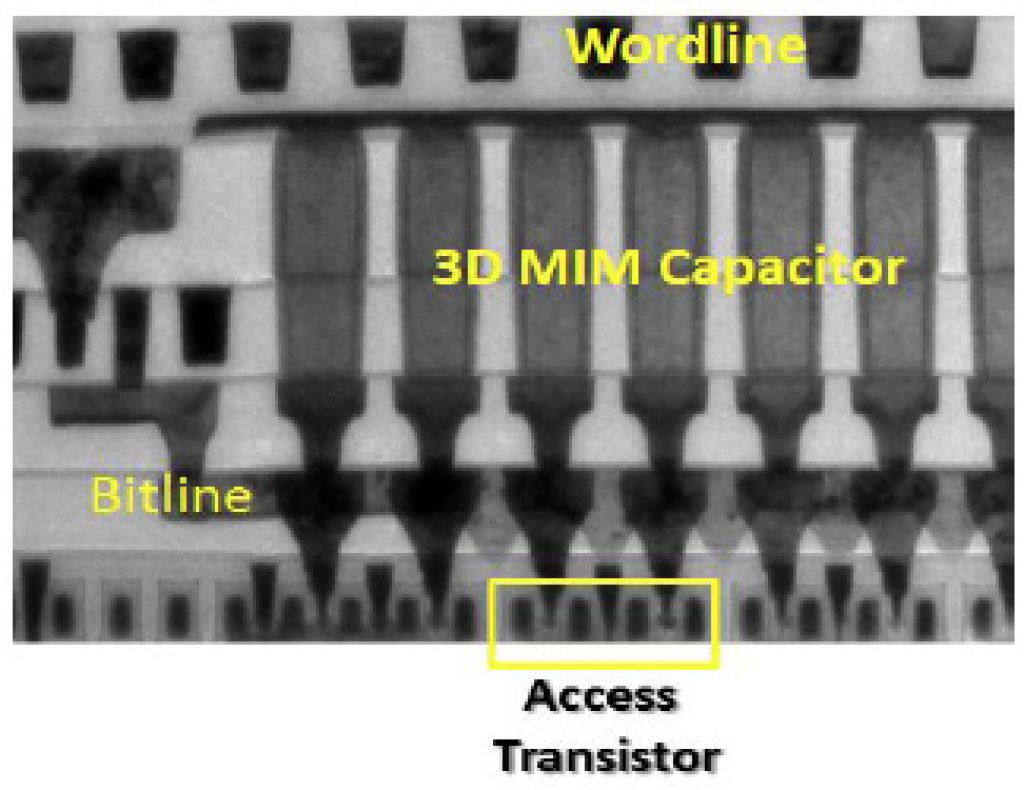

Por eso, otro enfoque para aportar soluciones es crear estructuras de condensadores dentro del propio chip, usando MIM (Metal-Insulator-Metal) o MOM (Metal-Oxide-Metal) e incluso condensadores de trinchera profunda, que se puede crear fácilmente por los mismo métodos que los transistores semiconductores del chip, por lo que no implicaría hacer modificaciones en el proceso de fabricación. Es decir, crear una especie de jerarquía de varios niveles para tratar que no falte la entrega de energía al procesador, algo similar a la jerarquía de memoria, pero con la energía…

Como se puede ver en la imagen anterior, un condensador MIM no es más que dos capas metálicas paralelas con un dieléctrico o aislante entre medias. Este dieléctrico suele ser de alta constante K. Según el tamaño de estas trincheras se pueden conseguir más o menos capacidad. Generalmente, estos condensadores se forman en capas metálicas muy bajas, en torno a la M2-M4. Es decir, casi justo por encima de los transistores, aunque también los hay en capas superiores. Estos los puedes ver en muchos diseños, como en los chips Intel 22FFL, los AMD Zen para sus CCX, etc.

Estos MIM suelen ser superiores a los condensadores de desacoplo que se instalan fuera del chip, pero aumentan el coste de fabricación debido a la necesidad de emplear más fotomáscaras y más etapas durante la fabricación.

Por otro lado, la idea tras los MOM es similar, la de generar líneas paralelas metálica separadas por un aislante (óxido de silicio), pero en este caso se encuentran giradas 90º, es decir, en vez de estar en vertical, se forman horizontalmente.

Y, por último, los condensadores de trinchera profunda son otra de las opciones disponibles, aunque son menos comunes, ya que grabar trincheras profundas y estrechas en un chip puede ser un coste importante, e incluso el empleo de doble patrón en muchos casos para el grabado. No obstante, fueron usados por varios procesadores como los fabricados con proceso SOI 32nm de IBM, hasta el SOI 14nm, como en el IBM z12. Otro ejemplo es el de TSMC, que también los ha creado para algunos diseños desde 2019.

Conclusión

Para finalizar, tras todo lo dicho, como ves, la entrega de energía no es nada fácil. Y de ella va a depender en gran medida el rendimiento, la eficiencia y el coste del procesador. Por tanto, no hay que tomársela a la ligera. En el pasado también hubo estos mismos problemas con la distribución de la señal de reloj, ya que cualquier retraso puede hacer que una unidad o biestable tome un valor que no sea el correcto, produciendo fallos. Sin embargo, solucionar estos problemas de frecuencia supuso la creación de árboles de distribución, aunque esto es otra historia que quizás te cuente en otro artículo…

Son muchos los retos a sortear, desde usar un voltaje lo más alto posible para la entrega y que se reduzcan las pérdidas por corrientes elevadas, hasta usar un voltaje muy bajo y estable una vez dentro del chip para la lógica CMOS, etc.

Al mismo tiempo, la corriente necesaria para alimentar el chip cambia constantemente como hemos mencionado, debido al sistema DVFS o a las diferentes instrucciones que se ejecutan en el procesador. Por ejemplo, no es lo mismo cuando se está realizando operaciones aritméticas o lógicas con enteros simples que cuando se están usando complejas FPUs para SIMD, como pueden ser las AVX o similares. Por esto, el sistema PDN siempre tiene que dar lo que se necesita en cada momento, evitando así inestabilidad o fallos.

Además, esta entrega de energía está estrechamente relacionada también con el proceso de fabricación empleado, entre otros factores. Por lo que los desarrolladores deben tener en cuenta demasiadas variables…