- Electron E1 redefine la arquitectura tradicional de CPUs para sistemas embebidos gracias a su modelo de flujo de datos espacial.

- El compilador effcc permite mapear el código a una red de tiles, mejorando la eficiencia energética respecto a ARM Cortex y otros competidores, especialmente en tareas repetitivas y operaciones de machine learning.

- Sectores como IoT, aeroespacial, defensa o wearables pueden beneficiarse de esta tecnología, aunque su éxito dependerá de la madurez del compilador y la aceptación de los desarrolladores.

El panorama tecnológico está cambiando de forma acelerada, especialmente cuando hablamos de dispositivos que necesitan autonomía, eficiencia y una operativa fiable durante años sin apenas acceso a fuentes de energía. En este contexto, surge un nombre que empieza a resonar con fuerza en los círculos de innovación: Electron E1, el procesador revolucionario de Efficient Computer, una startup que pretende reescribir las reglas del mercado de CPUs para sistemas embebidos.

No estamos ante una evolución incremental de los microcontroladores tradicionales; lo que Efficient Computer pone sobre la mesa es un cambio radical de paradigma. El Electron E1 busca solucionar los límites físicos y conceptuales que arrastran los chips diseñados hace décadas, para abrir la puerta a nuevas aplicaciones donde la eficiencia energética y la flexibilidad sean primordiales. ¿Cómo lo logran? Analizamos en profundidad la arquitectura, el funcionamiento, los argumentos técnicos y las expectativas que está generando.

¿Por qué surge la necesidad de CPU como el Electron E1?

Cada vez más, se requieren CPUs capaces de estar años operando en condiciones extremas, lugares de difícil acceso o donde la alimentación mediante baterías es la única alternativa. Pensemos en sensores remotos, dispositivos IoT o wearables que no pueden depender de recargas frecuentes.

Las arquitecturas clásicas presentan cuellos de botella energéticos. Los diseños tipo von Neumann, que llevan décadas dominando la industria, están optimizados para el flujo secuencial de instrucciones: extraen una instrucción de la memoria, la procesan, escriben los resultados y repiten el ciclo. Aunque esto ha dado lugar a mejoras sostenidas en rendimiento, implica un desperdicio considerable de energía en operaciones accesorias como la gestión de memoria y las tareas de predicción de ramas.

El salto disruptivo de Efficient Computer: la arquitectura Electron E1

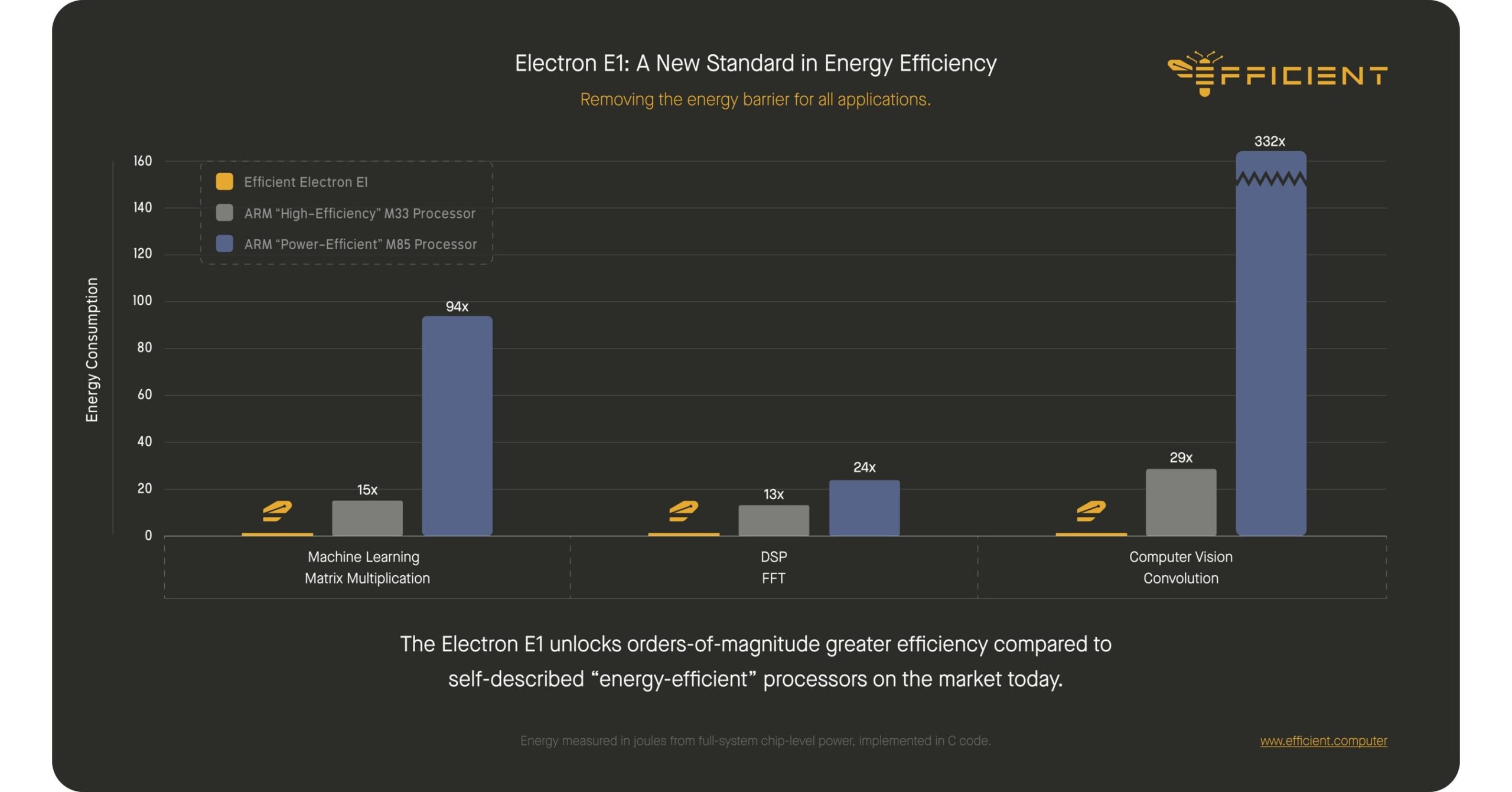

Cansados de estos desperdicios, los fundadores de Efficient Computer decidieron rediseñar la CPU generalista desde cero. El resultado es Electron E1: una CPU programable en C —y también soporta C++ y Rust— que, según sus propios benchmarks, consigue entre 10 y 100 veces mayor eficiencia energética en tareas típicas de sistemas embebidos, como transformadas rápidas de Fourier, convoluciones para machine learning o visión artificial, comparado con procesadores ARM de bajo consumo.

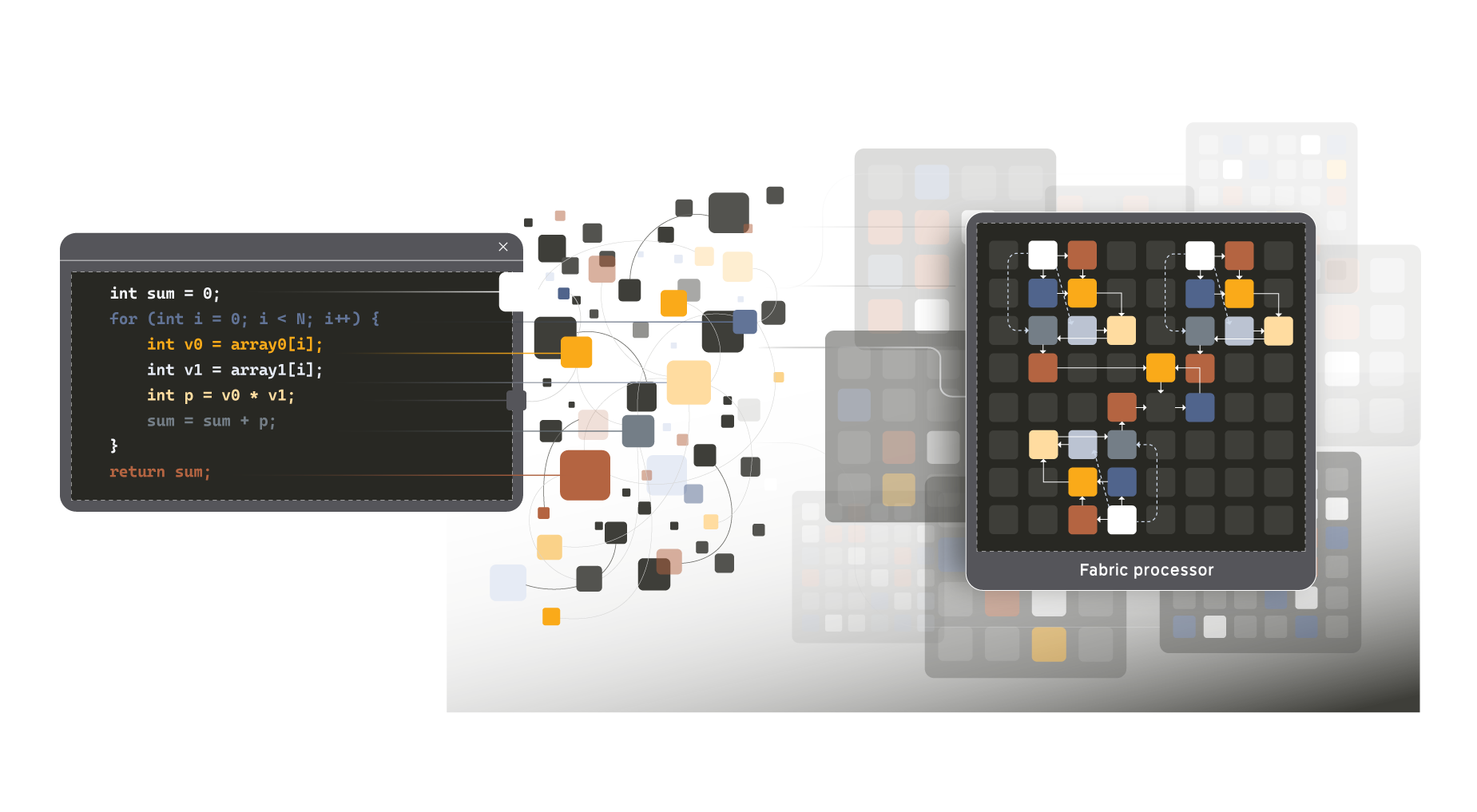

¿Dónde está el truco? La clave es una arquitectura de flujo de datos espacializada, que reemplaza el paradigma de flujo de control tradicional. En vez de ejecutar instrucciones una a una desde memoria, el E1 distribuye espacialmente las instrucciones sobre un entramado de “tiles” (básicamente pequeños núcleos de ejecución) conectados entre sí por una red programable de interconexión.

Funcionamiento interno: del flujo de control al flujo de datos espacial

La gran innovación del Electron E1 radica en cómo se organizan y procesan los programas. En un procesador convencional, la secuencia de instrucciones determina el flujo del programa. Pero en el E1, el compilador (llamado effcc) toma el código fuente y crea un mapa estático de qué “tile” resuelve cada operación. El dato fluye físicamente de tile en tile según ese plan, sin que sea necesario estar constantemente extrayendo instrucciones de la memoria ni empleando lógica compleja de predicción de ramas.

Esto elimina casi por completo el coste energético de la gestión de instrucciones y la reorganización dinámica del flujo de datos. Cada tile funciona como un procesador muy simplificado que activa su operación cuando llegan todos los datos que necesita, y los resultados se envían instantáneamente al siguiente tile en la secuencia programada.

En casos donde el flujo del programa ramifica (if/else, bucles “while”, etc.), el entramado de tiles se configura para que la información siga el camino adecuado. La red soporta bucles con retroalimentación mediante rutas que se activan de manera eficiente, permitiendo una mayor flexibilidad que muchas arquitecturas anteriores.

Comparativa frente a otras arquitecturas y procesadores tradicionales

Existen dataflow-style architectures en el mercado, como las TPUs de Google o el Inferentia de Amazon, pero suelen estar limitadas a operaciones específicas (por ejemplo, matrices, convoluciones o ciertas redes neuronales) y no ofrecen una flexibilidad generalista.

El Electron E1, en cambio, puede ejecutar cualquier flujo de datos arbitrario que un programa requiera. De hecho, uno de sus grandes hitos es haber resuelto el soporte a loops arbitrarios gracias a su red de interconexión programable, manteniendo la capacidad de cálculo general y el soporte para distintos lenguajes de alto nivel.

Según Efficient Computer, el E1 supera en eficiencia energética a procesadores ARM en tareas como multiplicación de matrices, transformada rápida de Fourier y convoluciones de visión por computador. Estas comparativas suelen hacerse frente a modelos Cortex M33, M85 y A5, todos ellos conocidos por su bajo consumo y su uso masivo en sistemas embebidos.

El papel fundamental del compilador effcc

La eficiencia no proviene sólo del hardware, sino de la sinergia con una herramienta clave: el compilador effcc. Este software se apoya en Clang como frontend e interpreta código en C, C++ y Rust, transformando el programa en un gráfico de datos donde se asigna cada operación a un tile concreto.

El compilador resuelve de forma estática (en tiempo de compilación) todos los posibles conflictos de ejecución, rutas de datos y secuencias, sin que haya necesidad de lógica de control costosa en tiempo de ejecución. Si la carga de trabajo es mayor que el chip, el compilador divide el gráfico en fragmentos y el hardware los va cargando dinámicamente conforme avanza la ejecución, manteniendo un pequeño caché de configuraciones por tile para optimizar bucles o patrones repetitivos.

Diferencias con arquitecturas VLIW, DSP y procesadores tradicionales

No hay cachés, tampoco existe un program counter ni un planificador global. La ejecución se basa exclusivamente en la llegada de los datos necesarios a cada tile y su procesamiento inmediato. Por tanto, el Electron E1 no es ni un VLIW, ni un DSP, ni simplemente otro microcontrolador con pipeline clásico; es una estructura de hardware que encarna el flujo de datos de una forma extremadamente eficiente.

Esta aproximación elimina buena parte del consumo energético que, en los procesadores tradicionales, se emplea simplemente en mover datos sin llegar a procesarlos. En sistemas embebidos, donde el consumo por operación es crítico, esta diferencia es determinante.

Ventajas: eficiencia energética y flexibilidad

El mayor argumento del Electron E1 es su rendimiento energético. La métrica clave es “operaciones por joule”, desplazando el foco de rendimiento por ciclo hacia cuánto trabajo útil se realiza por unidad de energía (clave en dispositivos alimentados por baterías o energía ambiental).

Efficient Computer asegura mejoras de entre 10 y 100 veces en eficiencia frente a los principales núcleos ARM para sistemas embebidos. Pero más allá del marketing, lo cierto es que ya se ha mostrado silicio funcional, kits para desarrolladores y benchmarks internos, lo que sugiere un producto real, con potencial de transformación para sectores como aeroespacial, defensa, sensorización industrial, wearables y sistemas espaciales, donde la robustez y el bajo mantenimiento son parámetros innegociables.

Desafíos y preguntas abiertas

No todo es sencillo en el mundo del Electron E1. Optar por una arquitectura donde el compilador tiene la última palabra implica retos, tanto en la robustez de la herramienta como en su capacidad para detectar y gestionar casos límite, errores de mapeo o flujos de datos complejos.

El éxito de esta propuesta dependerá, en parte, de que los desarrolladores no tengan que aprender paradigmas completamente nuevos. Efficient Computer promete que basta con programar en C++ y el compilador se encarga de todo, pero está por ver si la transición desde el modelo mental clásico es realmente fluida.

Adicionalmente, hay dudas razonables sobre el rendimiento en cargas de trabajo muy generales o poco predecibles. Otras iniciativas de arquitecturas de flujo de datos han funcionado muy bien como aceleradores para bucles calientes, pero han reincorporado núcleos RISC convencionales en generaciones posteriores para no perder rendimiento en tareas menos paralelizables.

Puntos críticos de la arquitectura Electron E1

- Ausencia de lógica compleja de control en tiempo real: La red de tiles y la ruta de datos se decide en tiempo de compilación, minimizando la sobrecarga y el consumo de energía.

- Capacidad para ejecutar cualquier tipo de bucle o ramificación: Se han resuelto los problemas habituales que limitaban la flexibilidad de arquitecturas dataflow anteriores.

- Soporte de operaciones en coma flotante de 32 bits, a diferencia de muchos CPUs de bajo consumo que se limitan a enteros o matemáticas en punto fijo, gracias al objetivo de Efficient Computer de escalar la arquitectura a soluciones más potentes y flexibles.

- Integración con frameworks de machine learning como PyTorch, Tensorflow o JAX, aunque no está claro hasta qué punto esta integración es automática o requiere intervención manual.

Comparativa con la competencia y otras experiencias en dataflow

Las CPUs tradicionales gastan gran parte de su energía moviendo datos entre memoria, cachés y registros, no solo ejecutando cálculos. En cambio, el E1 prioriza la eficiencia energética, basando toda su ejecución en la llegada de datos relevantes, lo que puede suponer mejoras significativas en operaciones de bajo nivel y alta repetición.

Algunos expertos escépticos señalan que la mejora real depende mucho del tipo de carga de trabajo y la eficiencia de la herramienta de compilación. La teoría sugiere que en microcontroladores la eficiencia podría duplicarse si se resuelven todos los problemas del flujo de datos, pero la idea de mejoras sostenidas de 100x en código realista puede parecer demasiado optimista. Sin embargo, disponer de silicio funcional y resultados internos muestra un avance real.

¿Hacia dónde irá la familia Electron?

El E1 representa solo el primer paso en la hoja de ruta de Efficient Computer. Ya hay planes para evolucionar hacia una gama completa, con futuros modelos como el E2 y el Photon P1, que ofrecerán más rendimiento, mayor variedad de cargas soportadas y opciones tanto en SOC como en IP para integradores.

El objetivo inmediato es reemplazar a los procesadores ARM en aplicaciones donde la autonomía, duración y fiabilidad sean prioritarias. Con el tiempo, será fundamental convencer a sectores tradicionales, que esperan chips con décadas de vida útil, de que esta nueva arquitectura puede ser tan fiable, predecible y mantenible como los microcontroladores en uso desde hace más de 20 años.

La transición de Efficient Computer de la investigación al producto final es un paso importante. Con Electron E1 ya disponible y kits de desarrollo en manos de los primeros usuarios, el debate pasa a ser técnico y comercial. La aceptación de la industria, la resolución de posibles puntos débiles del compilador y la participación de la comunidad de desarrolladores serán determinantes para su éxito. Es evidente que, por primera vez en mucho tiempo, alguien ha diseñado una CPU generalista desde cero, con un enfoque en superar las limitaciones energéticas y operativas del sector embebido.