- CXL permite expandir, compartir y desagregar memoria del servidor manteniendo coherencia de caché y un modelo de programación muy similar a la DRAM local.

- Modos como 1LM + Vol y Heterogeneous Interleave combinan DRAM y módulos CXL (CMM) como nodos NUMA separados o intercalados, optimizando capacidad y rendimiento.

- El pooling de memoria CXL reduce costes, desbloquea pools de hasta decenas de TiB y mejora drásticamente cargas de IA, bases de datos en memoria y análisis de grafos.

- Con CXL 4.0 y el soporte nativo en CPUs de Intel y AMD, los centros de datos avanzan hacia arquitecturas multi-rack con memoria verdaderamente desagregada.

La configuración de memoria en servidores CXL se ha convertido en uno de los temas calientes dentro de los centros de datos y de la infraestructura para IA. El motivo es sencillo: los cuellos de botella de memoria están frenando de mala manera el rendimiento de GPUs, CPUs y todo tipo de aceleradores, mientras que el coste de la RAM y de la HBM se dispara. En este contexto, CXL deja de ser un concepto de laboratorio para pasar a ser una pieza clave en el diseño de servidores modernos.

Hoy en día ya no basta con poner más módulos DIMM y listo. Los grandes modelos de lenguaje, las bases de datos en memoria o los sistemas de recomendación exigen arquitecturas mucho más flexibles, donde la memoria pueda crecer, agruparse, compartirse y gestionarse con una granularidad que las plataformas tradicionales no ofrecen. Aquí es donde entran en juego las distintas configuraciones de memoria con CXL, los módulos CMM-D/CMM, los controladores inteligentes y modos como 1LM + Vol o Heterogeneous Interleave.

Contexto: por qué la memoria es el nuevo gran problema

En los primeros tiempos de los grandes servidores, la CPU se llevaba gran parte del presupuesto: podía suponer hasta la mitad del coste base de un nodo para centro de datos o HPC. La memoria principal representaba solo en torno a un 15%, con otro 10% para la placa base y un 5-10% para el almacenamiento, que entonces se centraba en discos duros.

Con la llegada de las unidades SSD basadas en flash, el coste del almacenamiento cambió de perfil, pero al mismo tiempo la fuerte competencia entre fabricantes de CPU (especialmente con el regreso de AMD al mercado de servidores) redujo de forma notable el precio del cómputo. El resultado es que hoy la memoria RAM es uno de los componentes más caros del servidor, llegando a superar claramente a la CPU en coste total.

Si miramos el gasto energético, el panorama es similar: la CPU suele ser el mayor consumidor de energía, seguida muy de cerca por la memoria principal. Otros periféricos rondan el 20% y las unidades flash apenas un 5% gracias a su eficiencia frente a las HDD. La memoria no solo es cara de comprar, también es cara de alimentar y refrigerar.

A esto se suma que la capacidad y el ancho de banda de la RAM condicionan directamente lo que puede hacer la CPU. Cuando la memoria se queda corta o no da suficiente ancho de banda, la CPU y las GPUs se pasan el día esperando datos, convirtiendo la memoria en el cuello de botella número uno del sistema.

Además, el número de núcleos de las CPUs y la cantidad de aceleradores por servidor crecen a un ritmo mucho más rápido que el ancho de banda de memoria. Se abre una brecha de rendimiento entre núcleos y DIMM que los controladores de memoria tradicionales no pueden cerrar, por muchas ranuras que añadamos en la placa.

Qué es CXL y cómo encaja en la memoria del servidor

La clave de CXL es que mantiene coherencia entre las cachés de la CPU y la memoria conectada a través de dispositivos CXL, de manera que el software puede ver esa memoria casi igual que la DRAM interna. Para lograrlo, el estándar se divide en tres subprotocolos especializados que trabajan juntos:

- CXL.io: heredero directo de PCIe, se encarga de configuración, inicialización de enlaces, discovery de dispositivos, interrupciones, DMA y accesos a registros mediante operaciones Load/Store no coherentes. Es la base de toda la comunicación de control.

- CXL.cache: permite que los dispositivos (por ejemplo, aceleradores o tarjetas de memoria inteligente) puedan cachear de forma coherente la memoria del host con una interfaz de baja latencia, reduciendo viajes a la RAM principal.

- CXL.mem: habilita que la CPU acceda con coherencia a la memoria del dispositivo (DRAM o memoria no volátil) usando comandos de carga y almacenamiento, tanto para memoria volátil como para memoria no volátil.

En la práctica, esto se materializa a través de dispositivos CXL Type-3, conocidos como expansores de memoria. Estos conectan módulos DDR5 a través de ranuras PCIe o factores de forma tipo EDSFF (como E3.S), actuando como una especie de “puente inteligente” entre la CPU y más capacidad de memoria.

Los controladores CXL actuales añaden alrededor de 70 nanosegundos de latencia extra comparado con la DRAM conectada directamente al controlador de memoria de la CPU. Aunque es un aumento apreciable, sigue siendo entre 20 y 50 veces más rápido que un acceso NVMe, lo que coloca a la memoria CXL en un punto intermedio muy atractivo entre RAM local y almacenamiento.

Con CXL 1.0 y 1.1 se introdujo la base del estándar, y con CXL 2.0 se dio el salto clave al pooling de memoria y al soporte de conmutación, de modo que varios hosts pueden acceder a los mismos dispositivos CXL con asignaciones separadas y se añadió seguridad mediante integridad de datos y cifrado. CXL 3.0, que se asienta sobre PCIe 6.0 con codificación PAM-4, dobló el ancho de banda otra vez, mejoró la coherencia punto a punto vía DMA y habilitó verdaderamente el uso compartido de memoria entre múltiples hosts.

Modos de configuración: 1LM + Vol y Heterogeneous Interleave

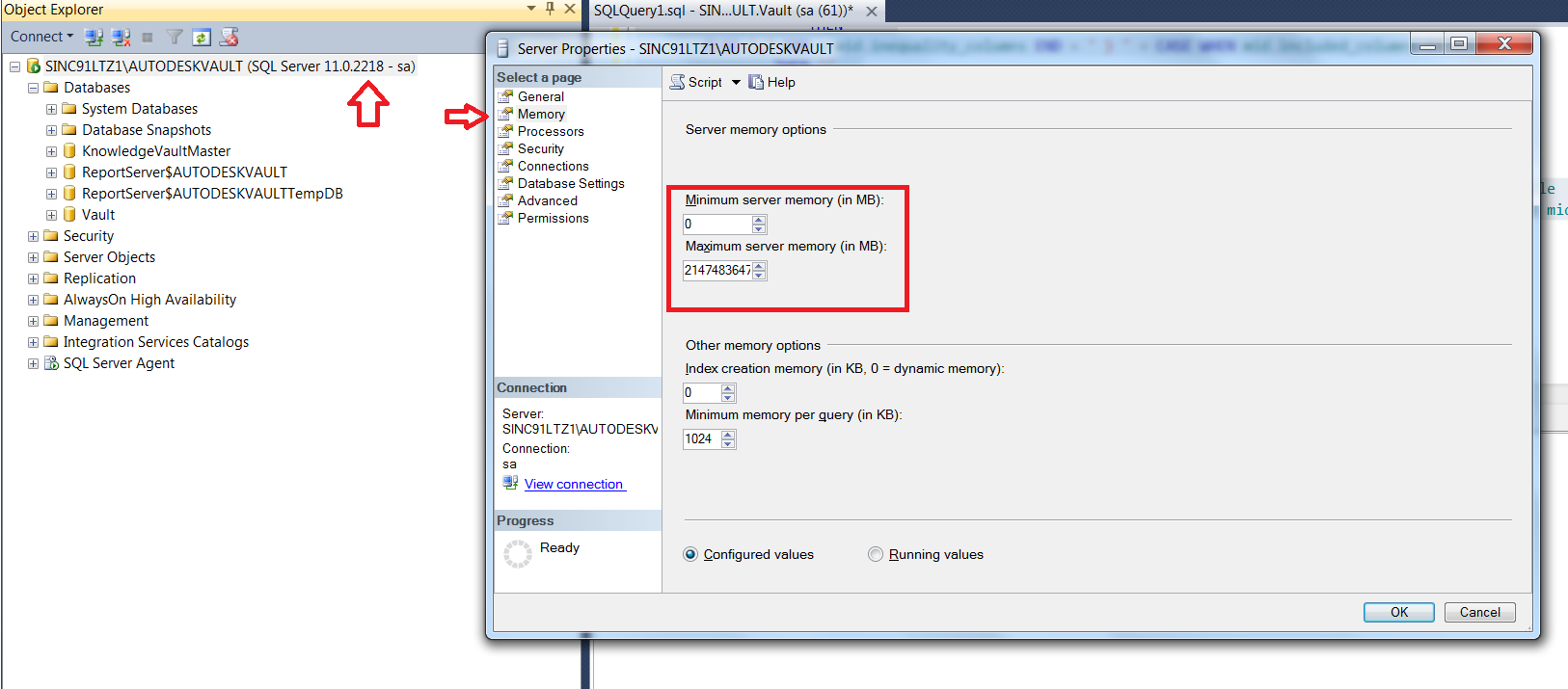

Cuando se combina DRAM tradicional con módulos de memoria CXL (CMM), el sistema puede presentar esa memoria de distintas formas. En algunas plataformas, el firmware UEFI permite seleccionar distintos modos de memoria, entre los que destacan:

- 1LM + Vol: la DRAM y los módulos CMM aparecen para el sistema operativo como dos nodos NUMA totalmente independientes. El software ve un nodo de memoria “clásica” y otro nodo “volumétrico” (generalmente CXL), lo que facilita separar cargas de trabajo o utilizar la memoria CXL como un tier más económico o de mayor capacidad.

- Heterogeneous Interleave: en este modo, DRAM y CMM se combinan para formar un único nodo NUMA intercalado. Desde el punto de vista del SO, es como si fuese una gran región de memoria donde se han mezclado ambas tecnologías, permitiendo que el hardware intercale accesos y reparta el tráfico entre DRAM local y CXL.

La activación de estos modos depende tanto de la configuración de hardware como del firmware. Si el UEFI detecta que falta algún requisito (tipo de módulo, topología, compatibilidad de CPU, etc.), suele hacer fallback automático al modo 1LM + Vol, que es el más conservador. Por eso es importante revisar a fondo el manual de producto y las notas de la plataforma para entender qué combinaciones de RDIMM DDR5 y CMM están soportadas.

En la documentación de algunos servidores se detalla, por ejemplo, qué configuraciones de CMM son válidas, cuántos módulos por canal o por socket se admiten y en qué orden deben instalarse físicamente. Suele indicarse también el menú de UEFI concreto al que hay que entrar para configurar el modo de memoria CMM y los pasos para habilitarlo de forma correcta.

Instalación y coexistencia de RDIMM DDR5 y módulos CXL (CMM)

Los servidores modernos permiten combinar RDIMM DDR5 tradicionales con módulos de memoria CXL (CMM), pero no vale cualquier mezcla. Los fabricantes suelen proporcionar una tabla de compatibilidad donde se especifican las configuraciones soportadas, el número máximo de CMM por socket y las restricciones de población.

En muchas plataformas, la instalación sigue un orden específico para los CMM: primero se completan determinadas ranuras de RDIMM, luego se añaden los módulos CXL en zócalos PCIe o bahías EDSFF indicadas. Saltarse ese orden puede provocar que el servidor no arranque en el modo de memoria deseado o que el firmware desactive funciones avanzadas como el Heterogeneous Interleave.

Para ajustar el modo CMM, el administrador debe entrar en la interfaz de configuración del servidor (UEFI) y acceder a la sección dedicada a la memoria CXL o CMM. Desde ahí se selecciona el modo (1LM + Vol, interleaving heterogéneo, etc.), se validan los dispositivos detectados y se guarda la configuración. Los manuales de servidor incluyen normalmente un apartado específico llamado algo similar a “Módulo de memoria CXL” donde se explican estos pasos.

Todo esto cobra más importancia a medida que los fabricantes lanzan factores de forma como E3.S 2T con soporte CXL 2.0, que convierten la memoria en algo mucho más modular. El mismo chasis puede alojar unidades de almacenamiento NVMe y módulos CMM en formatos muy similares, lo que obliga a tener claro qué bahías se destinan a cada función.

Economía y pooling de memoria: por qué CXL cambia las reglas del juego

En la arquitectura clásica, cada servidor se vende con una configuración de DRAM fija, pensada para cubrir el peor caso de sus cargas de trabajo. Esto obliga a sobreaprovisionar memoria, de forma que buena parte del tiempo tenemos módulos caros infrautilizados. Estudios recientes sitúan la memoria en torno al 30% del valor total del servidor en 2022, con proyecciones que superan el 40% para 2025.

El pooling de memoria que habilita CXL permite que varios servidores compartan acceso a un conjunto centralizado de memoria, asignando capacidad bajo demanda según la carga real. Microsoft, por ejemplo, ha estimado que al adoptar pooling de memoria basado en CXL puede reducir el total de memoria necesaria alrededor de un 10%, lo que se traduce en una bajada del 5% en el coste global de cada servidor.

Otros actores como SMART Modular Technologies calculan que combinar DIMM más económicos con tarjetas CXL adicionales puede ahorrar hasta un 40% en configuraciones de 1 TB de memoria comparado con la alternativa de cambiar a CPUs con más canales o más soporte de RAM. Esto es especialmente atractivo ahora que los precios de DRAM están tensionados por la enorme demanda de HBM para aceleradores de IA.

Los sistemas híbridos que mezclan DRAM local y memoria CXL han demostrado alcanzar entre el 95% y el 100% del rendimiento de una configuración solo con DRAM, mientras reducen hasta la mitad el coste de la memoria combinando técnicas de compresión y pooling eficiente. Para cualquier operador de centro de datos, es una jugada financiera difícil de ignorar.

Las previsiones apuntan a que el mercado de CXL alcanzará unos 15.000 millones de dólares para 2028, con más de 12.000 millones correspondientes a DRAM “detrás de CXL” (la memoria alojada en dispositivos CXL en lugar de colgada directamente de la CPU). Algunas estimaciones hablan de que esta DRAM representará cerca del 10% de toda la memoria de servidor hacia 2029.

Expansión de memoria CXL para cargas de IA generativa

La adopción de CXL está fuertemente impulsada por las cargas de inferencia de grandes modelos de lenguaje. Estos modelos requieren gigantescas KV cache cuya capacidad crece de forma lineal con la longitud de contexto. Para contextos de millones de tokens, el tamaño de la caché puede superar con creces la memoria disponible en las GPUs, incluso en las más caras con HBM masiva.

La investigación reciente muestra que gestionar la KV cache mediante memoria conectada por CXL puede alcanzar mejoras de rendimiento de hasta 21,9 veces, reducir 60 veces la energía consumida por token e incrementar 7,3 veces la eficiencia de coste total frente a implementaciones base que tiran de SSD o de redes RDMA para descargar cachés.

Empresas como XConn Technologies y MemVerge han demostrado en eventos como Supercomputing 2025 que es posible descargar y compartir en tiempo real enormes pools de KV cache entre GPUs y CPUs usando memoria CXL. En estas demos se han visto mejoras superiores a 5 veces frente a configuraciones que usan SSD como respaldo de caché o incluso frente a KV cache sobre RDMA.

Comparado con alternativas puramente de red, el pool de memoria CXL ha mostrado aceleraciones de 3,8x frente a RDMA a 200G y de 6,5x respecto a RDMA a 100G en escenarios de inferencia de IA. No es solo una cuestión de capacidad, también de latencia y de simplicidad de programación.

En 2025 empezaron a aparecer pools comerciales de memoria CXL del orden de 100 TiB, y ya hay planes para despliegues aún mayores en 2026. Astera Labs, por ejemplo, ha demostrado con sus controladores inteligentes Leo CXL que se pueden eliminar cuellos de botella de infraestructura de IA, logrando hasta 3 veces más instancias concurrentes de LLM con mayor rendimiento y 3 veces menos latencia.

Casos de uso más allá de la IA: bases de datos, recomendación y grafos

Aunque la IA generativa se lleve todos los titulares, la expansión de memoria vía CXL también está revolucionando otros tipos de cargas de trabajo. Los sistemas de recomendación de deep learning, las bases de datos completamente en memoria o el análisis de grafos se benefician enormemente de poder acceder a grandes espacios de memoria con buena latencia.

El sistema H3 Falcon de Micron, por ejemplo, combina memoria desagregada mediante CXL con un sistema de ficheros para memoria de acceso directo (FAMFS) soportado por Linux, logrando hasta 20 veces de mejora de rendimiento en bases de datos de grafos. Este tipo de aplicaciones suelen estar limitadas por la cantidad de datos que pueden mantener “calientes” en RAM.

Astera Labs ha publicado resultados en los que sus controladores Leo CXL junto con procesadores AMD EPYC de 5ª generación proporcionan incrementos de rendimiento cercanos al 70% en modelos de recomendación de deep learning, aprovechando arquitecturas híbridas donde parte de la memoria vive en módulos CXL.

SK Hynix, por su parte, ha desarrollado productos como el CMM-Ax (CXL Memory Module Accelerator), que integra capacidades de cómputo directamente junto a la memoria. La nube de IA Petasus de SK Telecom ya ha desplegado estos módulos para acelerar tareas intensivas en datos que se benefician de tener lógica de procesamiento muy cerca de la memoria.

En el ámbito de los servidores más generalistas, CXL permitirá crear tejidos de memoria compartida entre CPUs, GPUs, DPUs y otras XPUs, reduciendo la necesidad de replicar datos en cada dispositivo y facilitando arquitecturas donde varias unidades de cómputo trabajan sobre el mismo conjunto de datos en paralelo.

El ecosistema de controladores CXL y módulos de memoria

El éxito práctico de CXL descansa en una cadena de proveedores de controladores de memoria y módulos CXL que están dando forma a este mercado. En el lado de los controladores, tres nombres destacan especialmente: Astera Labs, Montage Technology y Microchip.

Astera Labs lidera con su familia Leo CXL Smart Memory Controllers, compatibles con CXL 2.0 y capaces de manejar hasta 2 TB de memoria por controlador. Estos chips implementan CXL.mem, CXL.cache y CXL.io, realizan entrelazado por hardware para presentar la memoria agregada como una única región al sistema operativo y añaden características avanzadas de RAS y gestión a través de su suite COSMOS.

La compañía ofrece diferentes formatos: tarjetas A-Series plug-and-play para despliegues rápidos, y variantes E-Series y P-Series para integraciones más personalizadas en servidores y chasis de alto rendimiento. La vista previa de memoria CXL que Microsoft Azure lanzó en noviembre de 2025 se apoya precisamente en controladores Leo, marcando el primer despliegue de memoria conectada por CXL en una nube pública a gran escala.

Montage Technology fue la primera en enviar un CXL Memory eXpander Controller (MXC) comercial, y actualmente suministra chips a gigantes de la memoria como Samsung o SK Hynix. Su controlador CXL 3.1 M88MX6852, presentado en septiembre de 2025, soporta tasas de hasta 64 GT/s en configuraciones x8, integra DDR5 de doble canal a 8000 MT/s y añade apenas unos 70 ns de latencia.

Este controlador se ofrece en un paquete de 25 x 25 mm que soporta tanto factores de forma EDSFF E3.S como tarjetas adicionales PCIe. Samsung y SK Hynix han superado las pruebas de conformidad CXL 2.0 utilizando chips MXC de Montage, lo que legitima aún más su adopción.

Microchip, por último, ha entrado en el juego con soluciones como el SMC 1000 8x25G, orientado a aplicaciones de expansión y pooling de memoria, integrando CXL en un portafolio más amplio de productos para conectividad de memoria, buffers y controladores hub SPD.

Productos de memoria CXL de Samsung, SK Hynix y Micron

En el lado de los módulos, Samsung ha lanzado su serie CMM-D (CXL Memory Module – DDR5), que constituye la línea central de su oferta CXL. El CMM-D 2.0 ofrece capacidades de 128 GB y 256 GB con hasta 36 GB/s de ancho de banda, soporte de CXL 2.0 y compatibilidad con PCIe Gen 5.

Samsung posiciona estos CMM-D como complemento a los DIMM locales existentes, asegurando que se puede ampliar la capacidad de memoria hasta un 50% y el ancho de banda hasta un 100%, con una reducción del coste total de propiedad gracias a la posibilidad de usar CPUs con menos canales de memoria o con menos sockets.

SK Hynix ha mostrado varias líneas de productos CXL, entre ellas módulos CMM-DDR5 que, junto con los controladores de Montage, se usan para expandir la capacidad de memoria del servidor, y los mencionados CMM-Ax que añaden funciones de cómputo en memoria. La compañía también trabaja en controladores propios CXL 3.0 y 3.1 para reducir su dependencia de terceros.

Micron, buscando recortar distancias con Samsung y SK Hynix en el segmento de memoria para servidores de alto margen, ha lanzado módulos de expansión de memoria CXL 2.0 apoyados en capacidades DDR5 de 96 GB. Su estrategia pasa por hacer de CXL una tecnología clave para diferenciar sus soluciones en entornos HPC y de IA.

La combinación de estos módulos con plataformas de software como FAMFS y servidores preparados para CXL permite ofrecer arquitecturas de memoria desagregada donde la capacidad ya no está ligada rígidamente al número de ranuras DIMM de la placa base.

Soporte de CXL en plataformas de servidor Intel y AMD

La carrera por integrar soporte CXL real en CPUs de servidor ha sido desigual. AMD tomó la delantera con EPYC Genoa, lanzado en 2022 con compatibilidad nativa para dispositivos CXL Type-3, lo que le dio una ventaja de varios años frente a su rival histórico.

La generación actual de procesadores AMD EPYC 9005 (Turin) mantiene y amplía este soporte, y las pruebas de rendimiento muestran que combinando controladores Leo CXL con EPYC de 5ª generación se pueden lograr mejoras de alrededor del 70% en modelos de recomendación y arquitecturas híbridas DRAM-CXL que igualan entre el 95 y el 100% del rendimiento de una configuración solo con DRAM.

En el lado de Intel el camino ha sido algo más accidentado. Los Xeon Scalable de 4ª generación “Sapphire Rapids” incluían la base del protocolo CXL, pero no ofrecían soporte real para dispositivos Type-3 de expansión de memoria en su lanzamiento. Esta compatibilidad llegó de forma oficial con la 5ª generación “Emerald Rapids”, aproximadamente un año después.

La familia Intel Xeon 6 introduce, además, el llamado CXL Flat Memory Mode, una capacidad particular que permite ajustar de forma más flexible la relación cómputo-memoria sin penalizar el rendimiento. Microsoft destacó precisamente este Flat Memory Mode al anunciar su vista previa de memoria CXL en Azure, enfatizando que ayudaba a explotar de forma más eficiente la memoria conectada por CXL.

En cuanto a los fabricantes de servidores, plataformas como los Lenovo ThinkSystem V4 con Intel Xeon 6 soportan memoria CXL 2.0 en factor de forma E3.S 2T. Otros actores clave como Dell Technologies, HPE, ASUS o Inventec están lanzando o preparando sistemas alineados con CXL 3.0, anticipando una ola de adopción más amplia a medida que el ecosistema madura.

CXL 4.0 y el salto hacia arquitecturas multi-rack

La publicación de la especificación CXL 4.0 en noviembre de 2025 marca el inicio de la fase de despliegues realmente desagregados a nivel de centro de datos completo. Esta versión se apoya en capas físicas PCIe 7.0 y duplica el ancho de banda de 64 GT/s a 128 GT/s, despejando las dudas sobre si CXL era capaz de escalar a gran distancia sin penalizaciones severas.

Una de las novedades más importantes es la introducción de puertos agrupados (pooled ports), que agregan múltiples conexiones físicas en enlaces lógicos únicos. Esto permite alcanzar hasta 768 GB/s por dirección (1,536 TB/s bidireccional) en configuraciones x16, manteniendo modelos de software relativamente sencillos pese al enorme ancho de banda disponible.

Otra mejora clave de CXL 4.0 es el soporte nativo de anchos de enlace x2 como opción de alto rendimiento, no solo como modo de respaldo para fallos de líneas como ocurría en versiones anteriores. Esto facilita topologías con mucho fan-out, ideales para escenarios de pooling de memoria donde un mismo pool sirve a muchos nodos de cómputo.

El estándar también contempla alcances extendidos mediante hasta cuatro retimers, lo que abre la puerta a configuraciones multi-rack sin degradación significativa de la señal. En la práctica, esto significa que la memoria CXL puede estar físicamente en un rack distinto al de los servidores que la usan, empujando el concepto de desagregación un paso más allá.

Se espera que los primeros sistemas CXL 4.0 multi-rack empiecen a desplegarse alrededor de 2026-2027. La especificación mantiene compatibilidad hacia atrás con CXL 2.0 y 3.x, de modo que las inversiones actuales en hardware CXL no quedan obsoletas, algo fundamental para que los operadores de grandes centros de datos se atrevan a adoptar la tecnología de forma agresiva.

El camino hacia una memoria verdaderamente convergente

Más allá de las versiones concretas, la visión que se dibuja con CXL es la de una memoria convergente capaz de conectar múltiples tipos de procesadores (CPU, GPU, DPU, TPU y demás XPUs) a un gran tejido de memoria compartida. Marvell, uno de los actores implicados en controladores CXL, habla directamente de un futuro donde las XPUs dejan de estar limitadas por la memoria local y se conectan todas a un gran “lago” de memoria.

Para llegar a ese punto todavía queda trabajo: hay que unificar software, controladores, sistemas operativos y herramientas de orquestación para explotar de verdad la memoria desagregada sin que el desarrollador tenga que pelearse con topologías complejas. Pero el movimiento de consorcios como Gen-Z, OpenCAPI o CCIX hacia la integración en el estándar CXL indica que el sector ha decidido apostar por un único camino común.

En paralelo, las empresas están experimentando con factores de forma nuevos para módulos CXL, que permiten más capacidad en un solo slot que un DIMM convencional y que pueden crecer tanto en “altura” como en “ancho” (más chips, más canales) sin las restricciones clásicas del zócalo de memoria. Al ir sobre carriles PCIe, estas tarjetas pueden escalar el ancho de banda añadiendo lanes, aunque la latencia siga siendo algo mayor que la de un controlador DRAM/HBM directo.

En el mundo del PC, CXL todavía no está presente de forma masiva, pero se perfila como uno de los cambios estructurales más profundos que veremos en la forma de entender la RAM. De implementarse de forma plena en CPUs de escritorio, podríamos ver configuraciones en las que la RAM se extiende dinámicamente vía CXL, mezclando memoria local ultrarrápida con pools adicionales de gran capacidad para aplicaciones creativas, juegos o máquinas virtuales.

El horizonte que plantean todas estas tecnologías es el de sistemas donde la memoria deja de ser un recurso rígidamente atado a cada servidor y se convierte en un servicio del centro de datos, ampliable, compartible y reasignable casi en tiempo real. Con la presión de la IA, el HPC y las aplicaciones de datos masivos, es muy probable que la interfaz CXL y la correcta configuración de memoria en servidores CXL acaben siendo uno de los pilares técnicos más determinantes de la próxima década.