- La lógica reversible evita el borrado de información y recupera energía en cada operación.

- Prototipos CMOS con resonadores muestran hasta 50% de recuperación y menos calor.

- Hoja de ruta: demo en 2025, chip de IA en 2027 y objetivos mayores a 10–15 años.

- Alternativas (cuántica, algoritmos) son complementarias; el foco aquí es eficiencia clásica.

En plena fiebre por la inteligencia artificial, la idea de que un chip pueda recuperar parte de la energía que emplea al calcular suena a ciencia ficción, pero un grupo de investigadores y emprendedores ha decidido convertirla en ingeniería práctica. Tras décadas de avances teóricos y prototipos, la llamada computación reversible regresa al primer plano con promesas muy concretas y una hoja de ruta que incluye prototipos a corto plazo y chips para inferencia de IA a medio plazo.

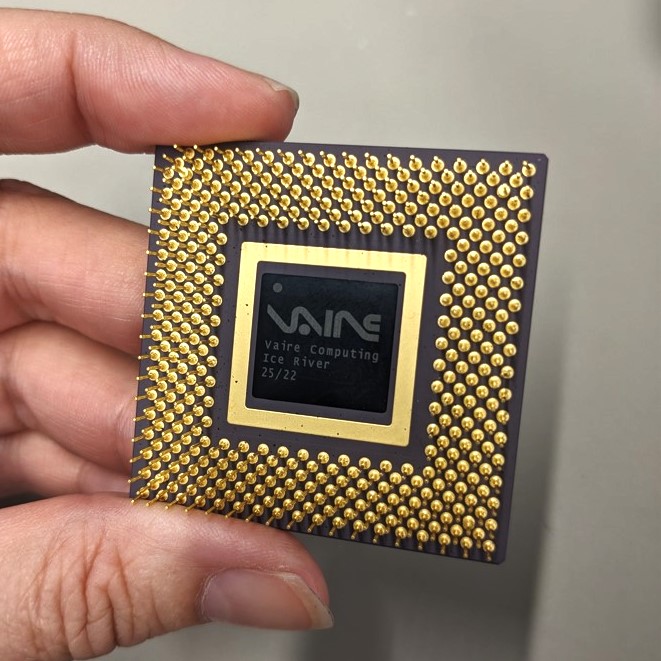

El nombre que más se repite en esta historia es Michael Frank, veterano de Sandia National Laboratories y referencia en este campo desde los 90, que ha dado el salto a la startup Vaire Computing. Su objetivo es ambicioso: demostrar que, con las técnicas adecuadas, la computación reversible puede ser entre decenas y miles de veces más eficiente que la lógica digital clásica, hasta el punto de llegar, en su versión más avanzada, a una mejora potencial de 4.000 veces respecto a los chips actuales, aunque para ese escenario piden paciencia de una década o más.

Qué es exactamente la computación reversible y por qué importa

La clave de la computación reversible es una observación física de 1961: Rolf Landauer, ingeniero de IBM, demostró que el borrado de un bit tiene un coste energético mínimo inevitable y genera calor. Esa conexión profunda entre información y termodinámica implica que toda operación irreversible (como descartar resultados intermedios) aumenta la entropía del sistema y, en consecuencia, disipa energía como calor.

Años más tarde, Charles H. Bennett, también en IBM, planteó un giro elegante: si una máquina pudiera deshacer sus pasos de cálculo, manteniendo suficiente información del historial para revertir las transformaciones, entonces sería posible evitar el borrado y, con ello, esquivar gran parte del coste térmico asociado. En esencia, no tiras información; la reciclas como parte del proceso y solo conservas entradas y salidas finales.

Este marco teórico maduró en círculos académicos y, ya en los 90, Michael Frank y otros pioneros empezaron a explorar chips capaces de recuperar energía. El hallazgo fue doble: en los circuitos internos se observaba cierta recuperación energética, pero buena parte de la ganancia se perdía en la alimentación externa, lo que obligaba a repensar la arquitectura de suministro y sincronización para que el sistema completo fuese realmente eficiente.

Vaire Computing ha retomado esa línea con un enfoque pragmático: lógica reversible implementada sobre transistores CMOS convencionales, apoyándose en resonadores y técnicas de conmutación adiabática para que la energía que normalmente se disiparía en un cambio 0→1 (o 1→0) se almacene y “devuelva” al circuito. Según su planteamiento, en un chip reversible bien diseñado no dejas que la energía se convierta en calor; la circulas y la reciclas internamente.

Por qué el momento es ahora: límites físicos y demanda desatada

La industria del silicio se acerca a topes duros. La miniaturización ha sido la receta durante décadas, pero las mejoras energéticas de cada nodo se reducen justo cuando la IA multiplica la demanda de cómputo. En 2016, Nature ya avisaba de que la Ley de Moore dejaría de marcar el ritmo y, a juicio de análisis del IEEE, la eficiencia de la lógica digital toca meseta antes de acabar la década.

Ese frenazo coincide con centros de datos que elevan su factura eléctrica y térmica a niveles difíciles de sostener. Proyecciones como las de Goldman Sachs apuntan a que los data centers podrían consumir alrededor del 12% de la electricidad en EE. UU. para 2030, mientras que una consulta en modelos tipo ChatGPT ya consume un orden de magnitud más energía que una búsqueda web clásica. En este contexto, cada julio disipado cuenta.

La computación reversible aparece como una alternativa radical pero coherente con la física: si reduces borrados y conviertes las transiciones en procesos más graduales, puedes acercarte al límite de Landauer y recuperar parte de la energía en cada operación. No se trata de violar la termodinámica, sino de operar más cerca de sus límites ideales aprovechando el historial de información del cómputo.

Este interés no llega solo. Se exploran otros caminos, desde la computación cuántica (con avances como el chip Willow de Google y su progreso en corrección de errores) hasta estrategias de eficiencia algorítmica, por ejemplo sustituir operaciones de coma flotante costosas por suma de enteros cuando el caso de uso lo permite. Cada enfoque ataca un ángulo distinto del mismo problema energético.

Cómo se intenta recuperar energía en el chip: resonadores y conmutación adiabática

Vaire Computing propone integrar en CMOS elementos “resonantes” y dominios de reloj en fase que permitan la transferencia gradual de carga en vez de conmutaciones bruscas. En los diseños convencionales, cada cambio lógico provoca picos instantáneos de corriente que se traducen en calor; aquí se busca ralentizar y sincronizar esas transiciones para retener y reutilizar la energía.

Esta filosofía se conoce como conmutación adiabática: en lugar de cargar y descargar nodos a toda velocidad (y quemar la diferencia como calor), el circuito gestiona la energía como si fuera un depósito que se vacía y se llena con cuidado, almacenando el excedente de cada operación en elementos resonantes. De acuerdo con resultados preliminares citados por la compañía, los prototipos muestran recuperaciones cercanas al 50% en bloques específicos, con reducciones de salida térmica del 40% al 75% frente a diseños equivalentes no reversibles.

La investigadora Hannah Earley ha descrito además la relación entre frecuencia y calor: si se reduce la velocidad de reloj moderadamente y se compensa con mayor paralelismo, los modelos sugieren que la energía recuperada crece de forma apreciable. En IA, donde los cálculos se paralelizan de manera natural, este compromiso entre latencia y eficiencia puede ser especialmente atractivo.

En términos prácticos, los bloques reversibles combinan varias ideas: puertas sincronizadas que actúan como depósitos temporales de energía, circuitos de tanque resonante que reciclan el “momento” eléctrico y operaciones que preservan la carga para evitar pago térmico por eliminación de datos. Atar todo eso sin perder tolerancia a fallos ni compatibilidad con flujos de fabricación es el reto de ingeniería.

Arquitectura propuesta: dominios resonantes, reloj multifase y compatibilidad CMOS

Para minimizar pérdidas, Vaire sincroniza grandes grupos de puertas en “dominios resonantes” con señales de reloj en múltiples fases. Esta orquestación fina permite capturar energía en el momento exacto de la inversión computacional y devolverla al siguiente ciclo. Frente a una topología monolítica y de reloj único, la arquitectura por dominios incrementa complejidad, pero gana control sobre dónde fluye la energía.

El planteamiento mantiene el sustrato tecnológico en terreno conocido: transistores CMOS. Esto ayuda a que, sobre el papel, la transición industrial no requiera reinventar la fabricación, aunque sí exige nuevas herramientas de verificación, redes de distribución de reloj más sofisticadas y módulos de recuperación con tolerancia a errores para que una desalineación no convierta el ahorro en calor indeseado.

| Característica | Enfoque reversible (Vaire) | Diseño tradicional |

|---|---|---|

| Señales de reloj | Multifase sincronizada por dominios | Frecuencia única global |

| Gestión de energía | Tanques resonantes y reciclaje de carga | Disipación pasiva como calor |

| Topología | Arquitectura basada en dominios | Estructura monolítica |

| Calendario de mercado | Prototipos 2025–2027; pilotos en torno a 2028 | Mejoras incrementales de eficiencia |

Hoja de ruta: de prototipos a chips de IA, sin prometer milagros instantáneos

El plan de Vaire arranca con un prototipo de circuito aritmético reversible fabricado en el primer trimestre de 2025, cuyo hito clave será demostrar por primera vez que un chip recupera energía durante su operación normal. Es un paso modesto en alcance funcional, pero crucial en señal.

Tras esa validación, la meta es un procesador orientado a inferencia de IA hacia 2027, un terreno donde el paralelismo y la eficiencia por vatio pesan más que la frecuencia pura. En paralelo, consorcios de investigación prevén producciones a escala piloto alrededor de 2028, a medida que maduren herramientas y flujos para integrar estos bloques reversibles en cadenas de fabricación estándar.

La visión a largo plazo sigue siendo la más rompedora: una plataforma reversible avanzada con hasta 4.000× de mejora potencial sobre chips actuales. La propia compañía sitúa ese escenario en un umbral temporal de 10 a 15 años, un recordatorio de que la física permite los beneficios, pero la ingeniería a gran escala lleva su tiempo, sus validaciones y sus iteraciones.

Mientras llega esa meta, la expectativa realista se centra en bloques concretos (operadores aritméticos, rutas de datos específicas) donde las ganancias de recuperación puedan medirse, estandarizarse y empaquetarse para aplicaciones que sufran cuellos de botella térmicos, como centros de datos con limitaciones de refrigeración.

IA y paralelismo: dónde más brilla la reversibilidad

El mundo de la IA es un candidato natural porque distribuye las cargas en paralelo. Si un chip reversible opera más despacio por núcleo, pero permite desplegar más instancias con menor calor por operación, el rendimiento global por vatio puede ser superior al de arquitecturas convencionales que exprimen frecuencia a costa de disipación.

En cálculos matriciales para inferencia, varios prototipos citados en la literatura muestran caídas de la potencia térmica del 40%–60% respecto a GPU clásicas en condiciones de laboratorio. Hay que traducir esos números a silicio comercial, pero son indicios de que la estrategia de bajar la temperatura de operación y reciclar carga encaja con las necesidades de despliegues de IA sostenibles.

Además, la reversibilidad puede convivir con mejoras algorítmicas de siempre: usar representación de enteros y operaciones más baratas cuando la precisión lo permite, podar modelos, y ajustar arquitecturas para bajar el coste energético por token. Ir sumando capas de eficiencia es clave para escalar IA sin chocar con límites de potencia y refrigeración.

Contexto y alternativas: de la cuántica a optimizaciones de software

En paralelo, la computación cuántica sigue avanzando a su ritmo. Google presentó su chip Willow, con un ejercicio de referencia extremadamente favorable a los cúbits que resolvió en minutos lo que a un supercomputador le llevaría una eternidad. Los expertos aclaran que es un hito experimental aún lejos de aplicaciones masivas, aunque con progresos notables en corrección de errores.

Su impacto a corto plazo será sobre todo en simulaciones donde los efectos cuánticos son intrínsecos (química, materiales, quizá fusión), mientras que la reversibilidad aborda el problema energético de la lógica clásica allí donde ya se consume a gran escala. Son caminos complementarios: uno redefine el modelo de cómputo, el otro exprime la física para acercarse a los límites termodinámicos en silicio convencional.

También hay margen de mejora desde el software: elegir formatos numéricos más baratos, reducir multiplicaciones en coma flotante, y priorizar métodos que minimicen el “borra y recalcula”. Ninguna de estas ideas compite frontalmente con la reversibilidad; más bien se suman para recortar vatios por operación de forma acumulativa.

Termodinámica, entropía e información: el suelo físico del problema

El principio de Landauer cuantifica el coste mínimo de borrar un bit: E = kT ln 2. A temperatura ambiente, ese umbral ronda los 2,75 zJ por operación irreversible. Aunque los chips convencionales están muy por encima de ese límite, la meta de los diseños reversibles es acercarse recuperando estados de carga en vez de descartarlos a cada paso.

La conexión entre información y calor se aprecia en el paralelismo formal entre la entropía de Shannon (H) y la entropía térmica de Boltzmann (S). En términos operativos, cuando la lógica trata los datos como desechables, acelera el crecimiento del desorden y paga ese precio en forma de calor. Conservar el historial suficiente para deshacer operaciones revierte parte del incremento de entropía.

Lejos de desafiar la segunda ley, la computación reversible la respeta: la energía no se crea de la nada; se reencauza para que una porción significativa vuelva al circuito en lugar de disiparse. Este enfoque no elimina toda pérdida, pero sí permite dramáticas reducciones frente a la conmutación abrupta y al borrado frecuente de estados.

Retos de ingeniería: sincronización, verificación y escalado

Coordinar millones (o miles de millones) de puertas en dominios resonantes no es trivial. La arquitectura tolera menos desajustes de reloj y requiere sincronización fina para que la energía capturada no se “fugue” como calor. Una sola operación desalineada puede degradar el ahorro a escala de bloque, así que el margen de error es estrecho.

Además, escalar desde demostradores aislados a sistemas completos demanda herramientas nuevas: verificación específica para redes de reloj por dominios, paquetes de recuperación de carga con corrección de errores, e incluso apilado 3D compatible con fundiciones existentes. Como resume un ingeniero de una gran foundry, lo que hace falta es silicio funcional que encaje en flujos de trabajo actuales, no solo papers brillantes.

Otro reto es económico: cada nodo de vanguardia eleva los costes. Los diseños de 2 nm exigen inversiones enormes por máscara y validación, lo que limita quién puede iterar rápido. La promesa de la reversibilidad mejora si se puede demostrar en nodos maduros CMOS, donde la adopción sea viable sin reinventar la fábrica.

Aun con estos desafíos, hay señales positivas: reducciones térmicas repetibles en prototipos, y pilotos industriales en el horizonte de 2028. Si los bloques reversibles se integran como IP reutilizable con garantías de verificación y herramientas de síntesis compatibles, su despliegue podría acelerarse dentro del ecosistema existente.

Impacto en centros de datos: del calor residual al ahorro operativo

La realidad operativa en data centers es tozuda: buena parte de la potencia de entrada se pierde en forma de calor, y los costes de refrigeración llegan a superar a los de hardware en regiones calientes. Casos como el de Phoenix, con servidores de IA rozando temperaturas elevadas, ilustran dónde un chip que devuelva energía al circuito cambia las reglas del juego.

Reducir la entropía generada por operación impacta directamente en la factura térmica: estimaciones citadas apuntan a ahorros del 30%–50% en cooling si la disipación por operación cae lo suficiente. En despliegues a gran escala, ese diferencial se traduce en densidad de cómputo mayor por rack, menos agua o refrigerantes y, sobre todo, margen eléctrico para seguir creciendo sin ahogar la red.

Vaire Computing: quiénes son y qué prometen

Fundada por la investigadora Hannah Earley y el emprendedor Rodolfo Rosini, Vaire opera desde Londres con equipos en Cambridge (Reino Unido), Seattle y Washington. La firma ha sido seleccionada por programas de incubación como Chip Start con apoyo del Reino Unido, lo que les da acceso a software de diseño, propiedad intelectual y mentorización específicos para semiconductores.

Su mensaje es claro: los chips actuales desperdician casi toda la energía de entrada como calor, mientras que un diseño reversible bien orquestado puede reciclarla internamente. Empezarán con un chip de alcance acotado, seguirán con un procesador de IA para inferencia en 2027 y no esperan la versión realmente “4.000×” antes de 10–15 años. Ambición sí, humo no: distinguen entre promesa física y producto comercial.

Mirando el conjunto, la computación reversible aporta un camino tangible para aliviar el choque entre límites físicos y sed de cómputo: desde Landauer y Bennett hasta los resonadores CMOS de Vaire, todo encaja en una narrativa donde reciclar energía dentro del chip no es ya un truco teórico, sino una apuesta industrial con plazos, métricas y un terreno de juego ideal en la IA y los centros de datos.